Altra® Platform Hardware Design Specification

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Android in the Cloud on Arm Native Servers

Android in the Cloud on Arm Native Servers Introduction All the chatter about Arm servers and the role of Android in the cloud in recent years generates questions about what these things could mean for a largely mobile based platform like Arm/Android. This whitepaper examines the practical and commercial use cases that are driving a new paradigm linking the primary mobile and embedded computing platform in the world today with its new cousin in cloud infrastructure: Arm servers + virtualization + native Android execution. While detailing the use cases driving a mobile platform migration to cloud infrastructure, this whitepaper also showcases the solution that Ampere Computing, Canonical, and NETINT Technologies have partnered to produce addressing this migration. The solution is a stellar example of how a service provider or developer can take advantage of Arm native computing in a cloud context to bring together an ecosystem of over 3M primarily mobile apps integrated with benefits from a cloud enabled infrastructure. A case study around cloud gaming fills in the practical real-world considerations of this hot new paradigm. Cloud gaming really showcases the advantages of all the solution components the partners have integrated to make a scalable, efficient cloud resource available to a new class of cloud-native applications catering to the billions of users with Arm based devices worldwide. The whitepaper concludes with thoughts and predictions about the evolution of this new paradigm as hardware and software components mature in the coming years. A New Paradigm The Arm architecture has dominated the mobile processor market with its unrivaled ability to maximize power-efficiency. -

ISSCC 2022 INTELLIGENT SILICON for a SUSTAINABLE WORLD February 20-24, 2022 | San Francisco Marriott Marquis | San Francisco, California, USA Plenary Talks

ISSCC 2022 INTELLIGENT SILICON FOR A SUSTAINABLE WORLD February 20-24, 2022 | San Francisco Marriott Marquis | San Francisco, California, USA Plenary Talks ClassicMoore to SysMoore, The Future of the Intelligent Sensing: Power, Energy, High Performance Semiconductor Enabling the Next and the Si Saturation: all we need is a 1000X… Industry and Design “Automation Age” Design What and How? Aart de Geus Renée James Marco Cassis Inyup Kang Founder, Chairman and Founder, Chairman, and CEO, President, Sales, Marketing, Communications President and General Manager of co-Chief Executive Officer, Synopsys Ampere Computing and Strategy Development STMicroelectronics System LSI Business at Samsung Electronics Tutorials Student Activities Analog Circuit Design in Bipolar-CMOS-DMOS (BCD) Technologies Student Research Preview (SRP): Short Presentations w/ Poster Session Marco Berkhout, Goodix Technology, Nijmegen, The Netherlands Silkroad Award: Scholarships awarded for Far-East full-time students Fundamentals of High Frequency DC-DC Converters Kousuke Miyaji, Shinshu University, Nagano, Japan Invited Industry Track Noise-Shaping SAR ADCs Two Invited Industry tracks will highlight recent hot-product releases and discuss innovative ways they solved Yun-Shiang Shu, MediaTek, Hsinchu City, Taiwan product-level challenges. The focus this year is on Digital/ML, Systems and Quantum Computing. Fundamentals of Self-Sensing Processing Systems Special Events Shidhartha Das, Arm, Cambridge, United Kingdom Fundamentals of Process Monitors for Signoff-Oriented Circuit Next Gen Circuit Designer Workshop The Next Gen Circuit Designer Workshop 2022 is an educational workshop for EE undergraduates and early graduate students Design (Master's students/1-2 years of PhD) who are interested in choosing a career in integrated circuit (IC) design. -

NVIDIA and Tech Leaders Team to Build GPU-Accelerated Arm Servers for New Era of Diverse HPC Architectures

NVIDIA and Tech Leaders Team to Build GPU-Accelerated Arm Servers for New Era of Diverse HPC Architectures Arm, Ampere, Cray, Fujitsu, HPE, Marvell to Build NVIDIA GPU-Accelerated Servers for Hyperscale-Cloud to Edge, Simulation to AI, High-Performance Storage to Exascale Supercomputing SC19 -- NVIDIA today introduced a reference design platform that enables companies to quickly build GPU-accelerated Arm®-based servers, driving a new era of high performance computing for a growing range of applications in science and industry. Announced by NVIDIA founder and CEO Jensen Huang at the SC19 supercomputing conference, the reference design platform -- consisting of hardware and software building blocks -- responds to growing demand in the HPC community to harness a broader range of CPU architectures. It allows supercomputing centers, hyperscale-cloud operators and enterprises to combine the advantage of NVIDIA's accelerated computing platform with the latest Arm-based server platforms. To build the reference platform, NVIDIA is teaming with Arm and its ecosystem partners -- including Ampere, Fujitsu and Marvell -- to ensure NVIDIA GPUs can work seamlessly with Arm-based processors. The reference platform also benefits from strong collaboration with Cray, a Hewlett Packard Enterprise company, and HPE, two early providers of Arm-based servers. Additionally, a wide range of HPC software companies have used NVIDIA CUDA-X™ libraries to build GPU-enabled management and monitoring tools that run on Arm-based servers. “There is a renaissance in high performance computing,'' Huang said. “Breakthroughs in machine learning and AI are redefining scientific methods and enabling exciting opportunities for new architectures. Bringing NVIDIA GPUs to Arm opens the floodgates for innovators to create systems for growing new applications from hyperscale-cloud to exascale supercomputing and beyond.'' Rene Haas, president of the IP Products Group at Arm, said: “Arm is working with ecosystem partners to deliver unprecedented performance and efficiency for exascale-class Arm-based SoCs. -

OCP19 DRAFT Prospectus 081418

OCP GLOBAL SUMMIT | March 14–15, 2019 San Jose McEnery Convention Center | San Jose, CA SPONSOR PROSPECTUS 2018 OCP Global Summit Stats Attendees by Organizational Role Analyst 4% Marketer 7% Technology Engineer Architect 30% 11% Product Manager 12% Senior Business Executive Development/ 19% Account Manager 17% 3,441 813 100+ Companies Summit Attendees Media/Analysts Represented 81 34 Sponsors/ Countries Exhibitors Represented Page !2 of !19 Previous Summit Exhibitors and Sponsors OCP Global Summit 2018 - San Jose, CA 10Gtek Edgecore Networks Liqid Inc. Radisys Corporation 3M Eoptolink Liquid Telecom Rittal ADC Technologies Inc. Facebook LITE-On Storage Samsung ADLINK Technology Fadu LTO Ultrium Program Samtec Advanced Micro Devices, Fidelity Marvell Schneider Electric Inc. (AMD) Ampere Computing Finisar Mellanox Seagate Amphenol Flex Micron SK hynix Apstra Geist Microsoft Solarflare Artesyn Geist Global Mojo Networks Starline (Universal Electric Corp) ASRock Rack GIGABYTE Murata TE Connectivity Barefoot Networks Gigalight Nephos Inc. Telecom Infra Project (TIP) Bel Power Solutions HPE NGD Systems The Linux Foundation Big Switch Networks Huawei Nimbus Data TidalScale Cambridge Industries Hyve Solutions Nokia Toshiba Memory USA, Inc. America, Inc. Cavium Innovium OpenCAPI Consortium Vertiv ColorChip Inspur OpenPower Wave 2 Wave Solutions Lmtd. Cumulus Intel OpenStack Wiwynn DCD IP Infusion, Inc. OpenSwitch ZT Systems Dell EMC Ixia Penguin Delta Jess-link Products Co. Ltd. QCT/Quanta Distributed Management Lenovo Qualcomm Task Force (DMTF) -

SPONSORSHIP PROSPECTUS March 4–5, 2020 | San Jose Mcenery Convention Center | San Jose, California 2019 OCP Global Summit Stats

2020 OCP GLOBAL SUMMIT SPONSORSHIP PROSPECTUS March 4–5, 2020 | San Jose McEnery Convention Center | San Jose, California 2019 OCP Global Summit Stats Chart Title Analyst 4% Marketer 7% Technology Architect Engineer 11% 30% Product Manager 12% Business Senior Development Executive /Account 19% Manager 17% 3,600 727 100+ Summit Attendees Companies Media/Analysts Represented 77 42 Sponsors/ Countries Exhibitors Represented 2 Previous Summit Exhibitors and Sponsors 2019 OCP Global Summit - San Jose, CA 2CRSI Edgecore Networks Man Zai Industrial Co., Ltd. Schneider Electric 3M Eoptolink Marvell Seagate AMD Facebook Mellanox SK hynix Ampere Computing Finisar Micron SNIA Amphenol Flex Microsoft Starline AOI GIGABYTE MiTAC STORDIS GmbH Apstra HPE Molex Submer Immersion Cooling Arrcus Huawei Murata TE Connectivity Artesyn Hyve Solutions Nephos The Linux Foundation ASRock Rack Innovium Netronome TIP Auras Inspur Nokia Toshiba Barefoot Networks Intel OpenCAPI Vertiv Bel Power Solutions IT Renew OpenPOWER Western Digital Big Switch Networks Ixia, a Keysight Business OpenStack Wiwynn CIARA, a Hypertec Brand Juniper Networks Penguin Computing XCloud Networks CIG Lattice Semi QCT Xilinx Cumulus Networks Lenovo Rittal ZT Systems Dell LinkedIn Ruijie Networks Delta Electronics Americas Liqid Samsung DMTF Lite On Samtec 3 Schedule Overview* Day 1: Wednesday, March 4 Time Event 7:30am 9:00am Registration and Breakfast 9:00am 11:00am Keynotes 11:00am 12:00pm Expo Hall Open 12:00pm 2:00pm Lunch / Expo Hall Open / Expo Hall Talks 2:00pm 6:00pm Expo Hall Open -

LF Edge TAC Technical Advisory Council

LF Edge TAC Technical Advisory Council 21 October 2020 Meeting Details › October 21, 2020 (@ 7:00am PDT) › Meeting Info: › Join Zoom Meeting › https://zoom.us/j/286673048?pwd=REJlT1E2RmU3T3lpL0YrMzFHVVVsdz09 › › Meeting ID: 286 673 048 › Passcode: 254638 › › Dial by your location › 855 880 1246 US Toll-free › 877 369 0926 US Toll-free › Meeting ID: 286 673 048 › Find your local number: https://zoom.us/u/aeeh8taqXU Antitrust Policy Notice › Linux Foundation meetings involve participation by industry competitors, and it is the intention of the Linux Foundation to conduct all of its activities in accordance with applicable antitrust and competition laws. It is therefore extremely important that attendees adhere to meeting agendas, and be aware of, and not participate in, any activities that are prohibited under applicable US state, federal or foreign antitrust and competition laws. › Examples of types of actions that are prohibited at Linux Foundation meetings and in connection with Linux Foundation activities are described in the Linux Foundation Antitrust Policy available at http://www.linuxfoundation.org/antitrust-policy. If you have questions about these matters, please contact your company counsel, or if you are a member of the Linux Foundation, feel free to contact Andrew Updegrove of the firm of Gesmer Updegrove LLP, which provides legal counsel to the Linux Foundation. 8/28/20 3 LF Edge TAC Project/ Representative Named Alternate Project/ Representative Named Alternate Member Member Altran Shamik Mishra Nilanjan Samajdar GE Research Joel Markham James Ward Arm Reed Hinkel Tina Tsou HP Inc. Henry Lau AT&T Kandan Kathirvel HPE Rodney Richter Arun Thulasi Baidu Leding Li Huawei JianGuo Zeng Gabriel Yuyang Charter Jeffrey Saelens Mohammad IBM Joseph Pearson Ryan Anderson Zebetian Dell David Lake Trevor Conn Intel Jim St. -

Our Vision Our Story

The world is adopting the cloud. Almost everything you access today on a technology FOUNDED IN device (music, photos, games, computing, enterprise apps, retail experiences) resides OCTOBER 2017 in a cloud somewhere. Distributed computing environments in data centers with servers Chief Executive Officer: that process and manage all these workloads are not new. At Ampere, we believe it Renée James is time for a new hardware technology to run this new software world of the cloud. We believe that a new approach is required to run cloud data center servers efficiently and to ensure that consumers have a fast, reliable and secure experience. We believe HEADQUARTERS an innovative and different approach will change the future of everything you do with 4555 Great America Pkwy, technology in the cloud. With Ampere’s new server chip solution, cloud computing Ste. 601 just got a whole lot better. Santa Clara, CA 95054 Tel: +1408-542-8600 Fax: +1408-542-8601 Our vision At Ampere, we believe the future of hyperscale cloud computing requires a new kind of approach, with hardware and software designed for the distinct requirements of the cloud software environment. In our view, this is not something that can be borrowed from legacy systems. New technology designed specifically for the cloud will drive new innovations not even imagined yet, enabling the proliferation of more apps managed in the cloud, ranging from web search and categorization; online retail; content hosting and distribution; social media; communication services; artificial intelligence and machine learning; more secure storage of content; and much more. Our vision is to become the new standard for hyperscale, cloud computing data centers. -

Optimos™ Source-Down a New Era in MOSFET Performance

www.eenewseurope.com April 2020 electronics europeNews News OptiMOS™ Source-Down a new era in MOSFET performance european business press 200324_TBB_EENE_EU.indd 1 3/23/20 1:35 PM CONTENTS APRIL 2020 Dear readers, www.eenewseurope.com April 2020 Confinement has become the norm for most of Europeans and restrictions are taking place all over the world, giving a devastating blow to many industries and livelihoods electronics europeNews News yet promising casualty mitigation. The extreme economical context is calling for societal changes. The urgency to find medical and welfare solutions is accelerating research, unleashing new funds, open-source projects are flourishing and companies of all sizes are rushing to put remote work strategies into place and re-organize their workforce with new priori- ties. These changes will be long lasting, and hopefully for the better. Our April edition looks at some of the latest edge hardware and AI firmware solu- tions, some of which may find direct use in deciphering the vast amounts of data put to contribution by epidemiologists to predict the progression of the virus and possibly decide on the best confinement strategies. OptiMOS™ Source-Down Other features covered in eeNews Europe’s April edition include Optoelectron- a new era in MOSFET performance ics, Power Supplies and Batteries. european business press Until confinement restrictions become a thing of the past, stay safe, read and educate yourself. Feel free to share your academic and business news with us. Julien Happich Editor in Chief 4 - 49: OPINION 34 - 43: EDGE COMPUTING & AI Uncommon Market: Industry 4.0: edge Food system at risk of computing power is key crash? Edge computing used in conjunction with cloud Last Word: computing – that is, Haptics is ready for processing data locally standardization then sending it to the cloud – is becoming an increasingly indispens- 6 - 25: NEWS & TECHNOLOGY able element of the burgeoning Industry 4.0 concept. -

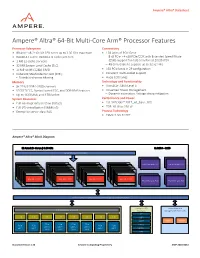

Ampere® Altra® 64-Bit Multi-Core Arm® Processor Datasheet

Ampere® Altra® Datasheet Ampere® Altra® 64-Bit Multi-Core Arm® Processor Features Processor Subsystem Connectivity • 80 Arm® v8.2+ 64-bit CPU cores up to 3.30 GHz maximum • 128 lanes of PCIe Gen4 • 64 KB L1 I-cache, 64 KB L1 D-cache per core ‒ 8 x8 PCIe + 4 x16 PCIe/CCIX with Extended Speed Mode • 1 MB L2 cache per core (ESM) support for data transfers at 20/25 GT/s • 32 MB System Level Cache (SLC) ‒ 48 controllers to support up to 32 x2 links • 2x full-width (128b) SIMD • 192 PCIe lanes in 2P configuration • Coherent Mesh Interconnect (CMI): • Coherent multi-socket support ‒ Distributed snoop filtering • 4 x16 CCIX lanes Memory Technology and Functionality • 8x 72-bit DDR4-3200 channels • Armv8.2+, SBSA Level 4 • SECDED ECC, Symbol-based ECC, and DDR4 RAS features • Advanced Power Management • Up to 16 DIMMs and 4 TB/socket ‒ Dynamic estimation, Voltage droop mitigation System Resources Performance and Power • Full interrupt virtualization (GICv3) • Est. SPECrate® 2017_int_base: 300 • Full I/O virtualization (SMMUv3) • TDP: 45 W to 250 W • Enterprise server-class RAS Process Technology • TSMC 7 nm FinFET Ampere® Altra® Block Diagram 80 Armv8.2+ Cores @ 3.30 GHz 8x DDR4 – 3200 GICv3 Interrupt Controller 72b DDR4 with ECC 72b DDR4 with ECC L1 Cache L1 Cache L1 Cache L1 Cache L1 Cache L1 Cache L1 Cache L1 Cache L1 Cache L1 Cache L1 Cache L1 Cache L1 Cache L1 Cache L1 Cache L1 Cache L2 ArmCache v8.2+ CPU L2 ArmCache v8.2+ CPU L2 ArmCache v8.2+ CPU L2 ArmCache v8.2+ CPU L2 Cache L2 Cache L2 Cache L2 Cache 72b DDR4 with ECC 72b DDR4 with ECC -

MACOM Technology Solutions Holdings, Inc. (Exact Name of Registrant As Specified in Its Charter)

UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 FORM 10-Q (Mark One) ý QUARTERLY REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the quarterly period ended December 29, 2017 or ¨ TRANSITION REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the transition period from to Commission File Number: 001-35451 MACOM Technology Solutions Holdings, Inc. (Exact name of registrant as specified in its charter) Delaware 27-0306875 (State or other jurisdiction of (I.R.S. Employer incorporation or organization) Identification No.) 100 Chelmsford Street Lowell, MA 01851 (Address of principal executive offices and zip code) (978) 656-2500 (Registrant’s telephone number, including area code) Indicate by check mark whether the registrant (1) has filed all reports required to be filed by Section 13 or 15(d) of the Securities Exchange Act of 1934 during the preceding 12 months (or for such shorter period that the registrant was required to file such reports) and (2) has been subject to such filing requirements for the past 90 days. Yes x No ¨ Indicate by check mark whether the registrant has submitted electronically and posted on its corporate Website, if any, every Interactive Data File required to be submitted and posted pursuant to Rule 405 of Regulation S-T (§232.405 of this chapter) during the preceding 12 months (or for such shorter period that the registrant was required to submit and post such files). Yes x No ¨ Indicate by check mark whether the registrant is a large accelerated filer, an accelerated filer, a non-accelerated filer, or a smaller reporting company. -

COMMSCOPE HOLDING COMPANY, INC. (Name of Registrant As Specified in Its Charter)

Table of Contents UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 SCHEDULE 14A (RULE 14a-101) SCHEDULE 14A INFORMATION Proxy Statement Pursuant to Section 14(a) of the Securities Exchange Act of 1934 Filed by the Registrant ☒ Filed by a Party other than the Registrant ☐ Check the appropriate box: ☐ Preliminary Proxy Statement ☐ Confidential, for Use of the Commission Only (as permitted by Rule 14a-6(e)(2)) ☒ Definitive Proxy Statement ☐ Definitive Additional Materials ☐ Soliciting Material Pursuant to § 240.14a-12 COMMSCOPE HOLDING COMPANY, INC. (Name of Registrant as Specified in its Charter) (Name of Person(s) Filing Proxy Statement, if other than the Registrant) Payment of Filing Fee (Check the appropriate box): ☒ No fee required. ☐ Fee computed on table below per Exchange Act Rules 14a-6(i)(1) and 0-11. (1) Title of each class of securities to which transaction applies: (2) Aggregate number of securities to which transaction applies: (3) Per unit price or other underlying value of transaction computed pursuant to Exchange Act Rule 0-11 (set forth the amount on which the filing fee is calculated and state how it was determined): (4) Proposed maximum aggregate value of transaction: (5) Total fee paid: ☐ Fee paid previously with preliminary materials. ☐ Check box if any part of the fee is offset as provided by Exchange Act Rule 0-11(a)(2) and identify the filing for which the offsetting fee was paid previously. Identify the previous filing by registration statement number, or the Form or Schedule and the date of its filing. (1) Amount Previously Paid: (2) Form, Schedule or Registration Statement No.: (3) Filing Party: (4) Date Filed: Table of Contents Table of Contents March 23, 2021 Dear CommScope Stockholders, 2020 was a tumultuous year for most of us: we suffered many things, achieved many things, and learned many things. -

Consolidated Financial Report for the Three-Month Period Ended June 30, 2021 (IFRS)

This English translation of the financial report was prepared for reference purposes only and is qualified in its entirety by the original Japanese version. The financial information contained in this report is derived from our unaudited consolidated financial statements appearing in item 3 of this report. SoftBank Group Corp. Consolidated Financial Report For the Three-Month Period Ended June 30, 2021 (IFRS) Tokyo, August 10, 2021 1. Financial Highlights (Millions of yen; amounts are rounded to the nearest million yen) (1) Results of Operations (Percentages are shown as year-on-year changes) Net income Total Income Net sales Net income attributable to comprehensive before income tax owners of the parent income Amount % Amount % Amount % Amount % Amount % Three-month period ended ¥1,479,134 15.6 ¥1,292,478 55.0 ¥932,489 (29.2) ¥761,509 (39.4) ¥996,400 (12.3) June 30, 2021 Three-month period ended ¥1,279,973 - ¥834,120 - ¥1,316,421 11.8 ¥1,255,712 11.9 ¥1,136,007 52.0 June 30, 2020 Basic earnings per Diluted earnings per share (Yen) share (Yen) Three-month period ended ¥437.45 ¥394.73 June 30, 2021 Three-month period ended ¥615.95 ¥589.96 June 30, 2020 Note: * Net sales and income before income tax are presented based on the amounts from continuing operations only. Year-on-year percentage changes in net sales and income before income tax for the three-month period ended June 30, 2020 are not presented because corresponding amounts for the three-month period ended June 30, 2020 are revised and presented respectively.