Memory Hierarchies

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Wind Rose Data Comes in the Form >200,000 Wind Rose Images

Making Wind Speed and Direction Maps Rich Stromberg Alaska Energy Authority [email protected]/907-771-3053 6/30/2011 Wind Direction Maps 1 Wind rose data comes in the form of >200,000 wind rose images across Alaska 6/30/2011 Wind Direction Maps 2 Wind rose data is quantified in very large Excel™ spreadsheets for each region of the state • Fields: X Y X_1 Y_1 FILE FREQ1 FREQ2 FREQ3 FREQ4 FREQ5 FREQ6 FREQ7 FREQ8 FREQ9 FREQ10 FREQ11 FREQ12 FREQ13 FREQ14 FREQ15 FREQ16 SPEED1 SPEED2 SPEED3 SPEED4 SPEED5 SPEED6 SPEED7 SPEED8 SPEED9 SPEED10 SPEED11 SPEED12 SPEED13 SPEED14 SPEED15 SPEED16 POWER1 POWER2 POWER3 POWER4 POWER5 POWER6 POWER7 POWER8 POWER9 POWER10 POWER11 POWER12 POWER13 POWER14 POWER15 POWER16 WEIBC1 WEIBC2 WEIBC3 WEIBC4 WEIBC5 WEIBC6 WEIBC7 WEIBC8 WEIBC9 WEIBC10 WEIBC11 WEIBC12 WEIBC13 WEIBC14 WEIBC15 WEIBC16 WEIBK1 WEIBK2 WEIBK3 WEIBK4 WEIBK5 WEIBK6 WEIBK7 WEIBK8 WEIBK9 WEIBK10 WEIBK11 WEIBK12 WEIBK13 WEIBK14 WEIBK15 WEIBK16 6/30/2011 Wind Direction Maps 3 Data set is thinned down to wind power density • Fields: X Y • POWER1 POWER2 POWER3 POWER4 POWER5 POWER6 POWER7 POWER8 POWER9 POWER10 POWER11 POWER12 POWER13 POWER14 POWER15 POWER16 • Power1 is the wind power density coming from the north (0 degrees). Power 2 is wind power from 22.5 deg.,…Power 9 is south (180 deg.), etc… 6/30/2011 Wind Direction Maps 4 Spreadsheet calculations X Y POWER1 POWER2 POWER3 POWER4 POWER5 POWER6 POWER7 POWER8 POWER9 POWER10 POWER11 POWER12 POWER13 POWER14 POWER15 POWER16 Max Wind Dir Prim 2nd Wind Dir Sec -132.7365 54.4833 0.643 0.767 1.911 4.083 -

Openpower AI CERN V1.Pdf

Moore’s Law Processor Technology Firmware / OS Linux Accelerator sSoftware OpenStack Storage Network ... Price/Performance POWER8 2000 2020 DRAM Memory Chips Buffer Power8: Up to 12 Cores, up to 96 Threads L1, L2, L3 + L4 Caches Up to 1 TB per socket https://www.ibm.com/blogs/syst Up to 230 GB/s sustained memory ems/power-systems- openpower-enable- bandwidth acceleration/ System System Memory Memory 115 GB/s 115 GB/s POWER8 POWER8 CPU CPU NVLink NVLink 80 GB/s 80 GB/s P100 P100 P100 P100 GPU GPU GPU GPU GPU GPU GPU GPU Memory Memory Memory Memory GPU PCIe CPU 16 GB/s System bottleneck Graphics System Memory Memory IBM aDVantage: data communication and GPU performance POWER8 + 78 ms Tesla P100+NVLink x86 baseD 170 ms GPU system ImageNet / Alexnet: Minibatch size = 128 ADD: Coherent Accelerator Processor Interface (CAPI) FPGA CAPP PCIe POWER8 Processor ...FPGAs, networking, memory... Typical I/O MoDel Flow Copy or Pin MMIO Notify Poll / Int Copy or Unpin Ret. From DD DD Call Acceleration Source Data Accelerator Completion Result Data Completion Flow with a Coherent MoDel ShareD Mem. ShareD Memory Acceleration Notify Accelerator Completion Focus on Enterprise Scale-Up Focus on Scale-Out and Enterprise Future Technology and Performance DriVen Cost and Acceleration DriVen Partner Chip POWER6 Architecture POWER7 Architecture POWER8 Architecture POWER9 Architecture POWER10 POWER8/9 2007 2008 2010 2012 2014 2016 2017 TBD 2018 - 20 2020+ POWER6 POWER6+ POWER7 POWER7+ POWER8 POWER8 P9 SO P9 SU P9 SO 2 cores 2 cores 8 cores 8 cores 12 cores w/ NVLink -

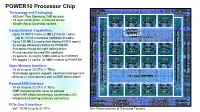

POWER10 Processor Chip

POWER10 Processor Chip Technology and Packaging: PowerAXON PowerAXON - 602mm2 7nm Samsung (18B devices) x x 3 SMT8 SMT8 SMT8 SMT8 3 - 18 layer metal stack, enhanced device 2 Core Core Core Core 2 - Single-chip or Dual-chip sockets + 2MB L2 2MB L2 2MB L2 2MB L2 + 4 4 SMP, Memory, Accel, Cluster, PCI Interconnect Cluster,Accel, Memory, SMP, Computational Capabilities: PCI Interconnect Cluster,Accel, Memory, SMP, Local 8MB - Up to 15 SMT8 Cores (2 MB L2 Cache / core) L3 region (Up to 120 simultaneous hardware threads) 64 MB L3 Hemisphere Memory Signaling (8x8 OMI) (8x8 Signaling Memory - Up to 120 MB L3 cache (low latency NUCA mgmt) OMI) (8x8 Signaling Memory - 3x energy efficiency relative to POWER9 SMT8 SMT8 SMT8 SMT8 - Enterprise thread strength optimizations Core Core Core Core - AI and security focused ISA additions 2MB L2 2MB L2 2MB L2 2MB L2 - 2x general, 4x matrix SIMD relative to POWER9 - EA-tagged L1 cache, 4x MMU relative to POWER9 SMT8 SMT8 SMT8 SMT8 Core Core Core Core Open Memory Interface: 2MB L2 2MB L2 2MB L2 2MB L2 - 16 x8 at up to 32 GT/s (1 TB/s) - Technology agnostic support: near/main/storage tiers - Minimal (< 10ns latency) add vs DDR direct attach 64 MB L3 Hemisphere PowerAXON Interface: - 16 x8 at up to 32 GT/s (1 TB/s) SMT8 SMT8 SMT8 SMT8 x Core Core Core Core x - SMP interconnect for up to 16 sockets 3 2MB L2 2MB L2 2MB L2 2MB L2 3 - OpenCAPI attach for memory, accelerators, I/O 2 2 + + - Integrated clustering (memory semantics) 4 4 PCIe Gen 5 PCIe Gen 5 PowerAXON PowerAXON PCIe Gen 5 Interface: Signaling (x16) Signaling -

Power8 Quser Mspl Nov 2015 Handout

IBM Power Systems Power Systems Hardware: Today and Tomorrow November 2015 Mark Olson [email protected] © 2015 IBM Corporation IBM Power Systems POWER8 Chip © 2015 IBM Corporation IBM Power Systems Processor Technology Roadmap POWER11 Or whatever it is POWER10 named Or whatever it is POWER9 named Or whatever it is named POWER7 POWER8 POWER6 45 nm 22 nm POWER5 65 nm 130 nm POWER4 90 nm 180 nm 130 nm 2001 2004 2007 2010 2014 Future 3 © 2015 IBM Corporation IBM Power Systems Processor Chip Comparisons POWER5 POWER6 POWER7 POWER7+ POWER8 2004 2007 2010 2012 45nm SOI 32nm SOI 22nm SOI Technology 130nm SOI 65nm SOI eDRAM eDRAM eDRAM Compute Cores 2 2 8 8 12 Threads SMT2 SMT2 SMT4 SMT4 SMT8 Caching On-chip 1.9MB (L2) 8MB (L2) 2 + 32MB (L2+3) 2 + 80MB (L2+3) 6 + 96MB (L2+3) Off-chip 36MB (L3) 32MB (L3) None None 128MB (L4) Bandwidth Sust. Mem. 15GB/s 30GB/s 100GB/s 100GB/s 230GB/s Peak I/O 6GB/s 20GB/s 40GB/s 40GB/s 96GB/s 4 © 2015 IBM Corporation IBM Power Systems Processor Designs POWER5+ POWER6 POWER7 POWER7+ POWER8 Max cores 4 2 8 8 12 Technology 90nm 65nm 45nm 32nm 22nm Size 245 mm2 341 mm2 567 mm2 567 mm2 650 mm2 * Transistors 276 M 790 M 1.2 B 2.1 B 4.2 B * 1.9 4 - 5 3 – 4 Up to 4.4 Up to 4.1 Frequencies GHz GHz GHz GHz GHz ** SMT (threads) 2 2 4 4 8 L2 Cache 1.9MB Shared 4MB / Core 256KB / core 256KB / core 512KB/core 4MB / Core 10MB / Core 8MB / Core L3 Cache 36MB 32MB On chip On chip On chip L4 Cache -- -- -- -- Up to 128MB Bandwidth Sust memory 15GB/s 30GB/s 100GB/s 100GB/s 230GB/s Peak I/O 6GB/s 20GB/s 40GB/s 40GB/s 96GB/s * with 12-core -

IBM's Next Generation POWER Processor

IBM’s Next Generation POWER Processor Hot Chips August 18-20, 2019 Jeff Stuecheli Scott Willenborg William Starke Proposed POWER Processor Technology and I/O Roadmap Focus of 2018 talk POWER7 Architecture POWER8 Architecture POWER9 Architecture POWER10 2010 2012 2014 2016 2017 2018 2020 2021 POWER7 POWER7+ POWER8 POWER8 P9 SO P9 SU P9 AIO P10 8 cores 8 cores 12 cores w/ NVLink 12/24 cores 12/24 cores 12/24 cores TBA cores 45nm 32nm 22nm 12 cores 14nm 14nm 14nm 22nm New Micro- New Micro- Enhanced Enhanced New Micro- Enhanced Enhanced Micro- New Micro- Architecture Micro- Architecture Architecture Micro- Micro- Architecture Architecture Architecture Architecture Architecture With NVLink Direct attach memory Buffered New New Process Memory Memory New Process New Process Subsystem New Process Technology Technology Technology New Process Technology Technology Up To Up To Up To Up To Up To Up To Up To Up To Sustained Memory Bandwidth 65 GB/s 65 GB/s 210 GB/s 210 GB/s 150 GB/s 210 GB/s 650 GB/s 800 GB/s Standard I/O Interconnect PCIe Gen2 PCIe Gen2 PCIe Gen3 PCIe Gen3 PCIe Gen4 x48 PCIe Gen4 x48 PCIe Gen4 x48 PCIe Gen5 20 GT/s 25 GT/s Advanced I/O Signaling N/A N/A N/A 25 GT/s 25 GT/s 32 & 50 GT/s 160GB/s 300GB/s 300GB/s 300GB/s CAPI 2.0, CAPI 2.0, CAPI 2.0, CAPI 1.0 , Advanced I/O Architecture N/A N/A CAPI 1.0 OpenCAPI3.0, OpenCAPI3.0, OpenCAPI4.0, TBA NVLink NVLink NVLink NVLink © 2019 IBM Corporation Statement of Direction, Subject to Change 2 Proposed POWER Processor Technology and I/O Roadmap Focus of today’s talk POWER7 Architecture POWER8 -

Starting at the Top of the Hour V2 © IBM Corporation, 2020 1

7/7/2020 AIX User Meeting 1 Starting at the top of the hour V2 © IBM Corporation, 2020 1 AIX User Meeting 1 https://ibm.webex.com/meet/nag Regular Sections in the following areas: 1. Recent News 2. AIX releases you should be running! 3. What you really need to know about ... <various topics> 4. Interesting information sources 5. Questions: That we have answered in the last few weeks! 6. Can you help? Perhaps you know answers or techniques that IBM does not. 7. Fun facts or favourite features! © IBM Corporation, 2020 2 1 7/7/2020 AIX User Meeting 1 https://ibm.webex.com/meet/nag Website https://www.ibm.com/support/pages/aix-user-meetings No pre-announcements – Once Announced: YES No official statements Yes: Technical Techie Talk Informal chat – these are Nigel’s opinions Will try leaving the microphones open - so you can ask questions - Unless we have too many people Shorter 5 to 10 minute topics, with where to get more information © IBM Corporation, 2020 3 AIX njmon (& nmon) user meeting & user meeting Aimed at hands-on AIX System admin, Aimed at AIX and Linux AIX operations & architects performance monitoring techies We are going to keep this simple We are going to keep this simple - Just turn up - Just turn up - Next event: - Next event: - Monday 6th July 2020 - Monday 6th July 2020 - 3 pm BST - 4:30 pm BST (British Summer Time = UTC+1) (British Summer Time = UTC+1) - Browse to - Browse to https://ibm.webex.com/meet/nag https://ibm.webex.com/meet/nag - To be recorded for replay - To be recorded for replay © IBM Corporation, 2020 4 2 7/7/2020 AIX User Meeting 1 Recent News 1. -

POWER Processor

POWER Processor Technology Overview Myron Slota POWER Systems, IBM Systems © 2017 IBM Corporation Quarter Century of POWER 22nm Legacy of Leadership Innovation 45/32nm Driving Client Value 65nm POWER8 0.18um 0.25um 130/90nm POWER7/7+ 0.35um Business 0.5um RS64IV Sstar 180/130nm POWER6 0.5um RS64III Pulsar RS64II North Star 0.5um POWER5/5+ RS64I Apache 0.22um Cobra A10 Muskie POWER4/4+ A35 Modern UNIX Era 0.35um Workstation POWER3 -630 0.72um POWER2 P2SC 1.0um RSC 0.25um POWER1 0.35um PC 0.6um 604e 603 601 1990 1995 2000 2005 2010 2015 © 2017 IBM Corporation 2 IBM Optimized Semiconductor Technology World class technology with value-added features for server business. POWER9 is built on 14nm finFET technology transitioned to Global Foundaries 17-layer copper wire Silicon On Insulator On-chip eDRAM (14nm) -Faster Transistor, Less Noise - 6x latency improvement - No off-chip signaling required - 8x bandwidth improvement - 3x less area than SRAM - 5x less energy than SRAM Dense interconnect - Faster connections - Low latency distance paths - High density complex circuits - 2X wire per transistor DT DT eDRAM Cell “IBM is committed to meeting the rising demands of cognitive systems and cloud computing. GF’s leading performance in 7LP process technology, reflecting our joint Research collaboration, will allow IBM Power and Mainframe systems to push beyond limitations to provide high-performance computing solutions while aggressively pursuing 5nm to advance our leadership for years to come.” Tom Rosamilia, Senior Vice President, IBM Systems © 2017 -

Despite the Pandemic, IBM POWER10 Is on the Near Horizon By

Feb. 9, 2021 Despite the Pandemic, IBM POWER10 is on the Near Horizon By Jean S. Bozman Even in the teeth of the pandemic, IBM is expected to deliver its POWER10 processors in calendar 2021, continuing its drive to place a new generation of POWER microprocessor engines in the world’s cloud data centers. Cloud migrations, accelerated by the pandemic’s impact on business worldwide, are making it possible to deploy many types of CPUs and GPUs in the cloud infrastructure, which is dominated by servers based on Intel x86 processors. POWER10 processors are aimed at running in the hybrid cloud, supporting AI/ML analytics applied to enterprise applications and scalable enterprise workloads (e.g., SAP, SAS). That strongly aligns the POWER10 processors with IBM’s strategic marketing priorities for hybrid cloud and AI/ML. The POWER10’s life in the extended hybrid cloud, coexisting with other types of processors from Intel and AMD, will be possible because cloud infrastructure supports mixed hardware types in a scale-out hyperscale world where clusters are the cloud’s go-to resources for running specific workloads. POWER10 is positioned for use in highly scalable (scale-up) systems – and in optimized scale-out cloud-native workloads. So, it is intended for supporting workloads that are migrating from the enterprise data center into the hybrid cloud. The emphasis is on faster processing of enterprise applications; support for accelerated AI analytics; support for multi-PB (petabyte) memory clusters, embedded math acceleration and extremely high security. How Will POWER10 Fit Into Hybrid Clouds? POWER10’s presence in the cloud is significant, because IBM’s stated corporate strategy focuses on hybrid clouds and AI. -

Cpus, Gpus, Accelerators and Memory.Pdf

CPUs, GPUs, accelerators and memory Andrea Sciabà On behalf of the Technology Watch WG HOW Workshop 18-22 March 2019 Jefferson Lab, Newport News Introduction • The goal of the presentation is to give a broad overview of the status and prospects of compute technologies – Intentionally, with a HEP computing bias • Focus on processors and accelerators – Not anymore just R&D, but soon to be used in production by LHC experiments • The wider purpose of the working group is to provide information that can be used to optimize investments – Market trends, price evolution • More detailed information is already available in a document – Soon to be added to the WG website 2 Outline • General market trends • CPUs – Intel, AMD – ARM – Specialized CPUs – Other architectures • GPUs • FPGAs • Interconnect, packaging and manufacturing technologies • Memory technologies 3 Semiconductor device market and trends • Global demand for semiconductors topped 1 trillion units shipped for the first time • Global semiconductor sales got off to a slow start in 2019, as year-to-year sales decreased • Long-term outlook remains promising, due to the ever-increasing semiconductor content in a range of consumer products • Strongest unit growth rates foreseen for components of – smartphones – automotive electronics systems – devices for deep learning applications 4 Semiconductor fabrication • Taiwan leading all regions/countries in wafer capacity • TSMC held 67% of Taiwan’s capacity and is leading • Samsung and SK Hynix represent 94% of the installed IC wafer capacity in -

IBM Power Systems POWER9 Processor/Server and IBM I Update

IBM Power Systems POWER9 Processor/Server and IBM i Update Daniel R Sundt Partner Technical Advocate BP Technical Sales & Enablement 3605 Highway 52 North IBM Power Systems Rochester, MN 55901 Tel 507 253 3228 Mobile 507 261 5329 [email protected] John J. Nelson Tim Spencer Client Systems Manager Client Technical Sales Industrial Market IBM Power Systems Industrial Market Mobile 612 414 9272 Mobile 414 870 0832 [email protected] [email protected] IBM Power Systems Strategy Hybrid Cloud Innovation: Resilient, Scalable, & Secure: Application Modernization: Agility, Flexibility & Automation Architectural Strength & Enterprise AI, Advanced On-prem and Public Cloud Superiority Analytics, Containerization, Extension via Microservices AIX IBM i Enterprise Linux IBM Public Cloud Extend resilient, scalable and Extend the most integrated Deliver optimized infrastructure Leverage Power Systems in the IBM mission critical Unix environment operating system with for workload modernization and Public Cloud across AIX/IBM i and with new innovative on-prem and innovative resiliency platform growth on Power Systems Enterprise Linux as clients adopt public cloud offerings with in Db2 Mirror, open source through SAP HANA, SAS Viya, mission-critical workloads in public consistent industry automation. languages and AI integration. OpenShift & Cloud Paks. clouds. Built on the Innovative POWER Processor Roadmap in conjunction with stack integration across Hardware Systems and System Software POWER9 14nm POWER10 7nm POWER11 © Copyright IBM Corporation 2020 IBM POWER Processor Roadmap POWER10 POWER7+ POWER9 POWER8 14 nm 32 nm 22 nm POWER7 POWER8NV 2+-4+ GHz 45 nm 3-4+ GHz POWER6+ 22 nm POWER6 65 nm 3-4+GHz POWER5™ POWER5+ 65 nm 90 nm . -

Elfv2 ABI Compliance TH/TS Specification

www.openpowerfoundation.org ELFv2 ABI Compliance TH/TS March 28, 2021 Revision 1.5 Specification ELFv2 ABI Compliance TH/TS Specification: Test Harness and Test Suite Definition Compliance Work Group <[email protected]> OpenPower Foundation Revision 1.5 (March 28, 2021) Copyright © 2017, 2020, 2021 OpenPOWER Foundation All capitalized terms in the following text have the meanings assigned to them in the OpenPOWER Intellectual Property Rights Policy (the "OpenPOWER IPR Policy"). The full Policy may be found at the OpenPOWER website or are available upon request. This document and translations of it may be copied and furnished to others, and derivative works that comment on or otherwise explain it or assist in its implementation may be prepared, copied, published, and distributed, in whole or in part, without restriction of any kind, provided that the above copyright notice and this section are included on all such copies and derivative works. However, this document itself may not be modified in any way, including by removing the copyright notice or references to OpenPOWER, except as needed for the purpose of developing any document or deliverable produced by an OpenPOW- ER Work Group (in which case the rules applicable to copyrights, as set forth in the OpenPOWER IPR Policy, must be followed) or as required to translate it into languages other than English. The limited permissions granted above are perpetual and will not be revoked by OpenPOWER or its successors or assigns. This document and the information contained -

Opencapi and Its Roadmap Myron Slota, President Opencapispeaker Name, Consortium Title Company/Organization Name

OpenCAPI and its Roadmap Myron Slota, President OpenCAPISpeaker name, Consortium Title Company/Organization Name Join the Conversation #OpenPOWERSummit Industry Collaboration and Innovation OpenCAPI and its Roadmap Topics . Industry Background and its influence on IBM’s IO and microprocessor roadmap . Limitations of CAPI running over PCIe . Creation of the OpenCAPI architecture and its benefits . OpenCAPI Consortium . Potential solutions based on coherent attached accelerators Industry Background that Defined OpenCAPI . Emerging workloads driving computational demand (e.g., AI, cognitive computing) . Moore’s Law not being supported by traditional silicon scaling Computation Data Access . Driving increased dependence on Hardware Acceleration for performance to continue on Moore’s Law • Hyperscale Datacenters and HPC • Require much higher network bandwidth (100 Gb/s -> 200 Gb/s -> 400Gb/s are emerging) • HPC and Artificial Intelligence (deep learning, inferencing) • Need more bandwidth between accelerators and memory • Emerging memory/storage technologies • Driving need for bandwidth with low latency 4 Industry Background that Defined OpenCAPI . Hardware accelerators are defining the attributes required of a high performance bus • Offload the computational demand on the microprocessor – if you are going to use accelerators, the bus needs to handle large amounts of data quickly • Growing demand for network performance and offload Computation Data Access • Introduction of device coherency requirements • Emergence of complex storage and memory