Stochastic Modeling and Performance Analysis of Multimedia Socs

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

An Emerging Architecture in Smart Phones

International Journal of Electronic Engineering and Computer Science Vol. 3, No. 2, 2018, pp. 29-38 http://www.aiscience.org/journal/ijeecs ARM Processor Architecture: An Emerging Architecture in Smart Phones Naseer Ahmad, Muhammad Waqas Boota * Department of Computer Science, Virtual University of Pakistan, Lahore, Pakistan Abstract ARM is a 32-bit RISC processor architecture. It is develop and licenses by British company ARM holdings. ARM holding does not manufacture and sell the CPU devices. ARM holding only licenses the processor architecture to interested parties. There are two main types of licences implementation licenses and architecture licenses. ARM processors have a unique combination of feature such as ARM core is very simple as compare to general purpose processors. ARM chip has several peripheral controller, a digital signal processor and ARM core. ARM processor consumes less power but provide the high performance. Now a day, ARM Cortex series is very popular in Smartphone devices. We will also see the important characteristics of cortex series. We discuss the ARM processor and system on a chip (SOC) which includes the Qualcomm, Snapdragon, nVidia Tegra, and Apple system on chips. In this paper, we discuss the features of ARM processor and Intel atom processor and see which processor is best. Finally, we will discuss the future of ARM processor in Smartphone devices. Keywords RISC, ISA, ARM Core, System on a Chip (SoC) Received: May 6, 2018 / Accepted: June 15, 2018 / Published online: July 26, 2018 @ 2018 The Authors. Published by American Institute of Science. This Open Access article is under the CC BY license. -

Comparative Study of Various Systems on Chips Embedded in Mobile Devices

Innovative Systems Design and Engineering www.iiste.org ISSN 2222-1727 (Paper) ISSN 2222-2871 (Online) Vol.4, No.7, 2013 - National Conference on Emerging Trends in Electrical, Instrumentation & Communication Engineering Comparative Study of Various Systems on Chips Embedded in Mobile Devices Deepti Bansal(Assistant Professor) BVCOE, New Delhi Tel N: +919711341624 Email: [email protected] ABSTRACT Systems-on-chips (SoCs) are the latest incarnation of very large scale integration (VLSI) technology. A single integrated circuit can contain over 100 million transistors. Harnessing all this computing power requires designers to move beyond logic design into computer architecture, meet real-time deadlines, ensure low-power operation, and so on. These opportunities and challenges make SoC design an important field of research. So in the paper we will try to focus on the various aspects of SOC and the applications offered by it. Also the different parameters to be checked for functional verification like integration and complexity are described in brief. We will focus mainly on the applications of system on chip in mobile devices and then we will compare various mobile vendors in terms of different parameters like cost, memory, features, weight, and battery life, audio and video applications. A brief discussion on the upcoming technologies in SoC used in smart phones as announced by Intel, Microsoft, Texas etc. is also taken up. Keywords: System on Chip, Core Frame Architecture, Arm Processors, Smartphone. 1. Introduction: What Is SoC? We first need to define system-on-chip (SoC). A SoC is a complex integrated circuit that implements most or all of the functions of a complete electronic system. -

Overview of CPU Power Consumption and Management in Smartphones

Overview of CPU Power Consumption and Management in Smartphones Prof. Sasu Tarkoma University of Helsinki, Aalto University, Helsinki Institute for Information Technology Contents • Modern smartphone SoC and CPUs – The CPU: power states – Power management basics • Smartphone solutions – Linux CPU Frequency subsystem – Power models • Intra-device task offloading – Sensor hub – Heterogeneous multiprocessing • Computation offloading Smartphones • Smartphones have become hubs for applications and connecting with the Internet • Cloud has emerged as a backend for mobile applications • Mobile data and WiFi are the dominant protocols for connecting with Internet resources • The next generation solutions are addressing limitations of the current smartphones – Coordination of resource usage – Offloading in its many forms – Heterogeneous environment and the emergence of IoT / M2M / wearables Observations • Smartphone and mobile device hardware and software evolve rapidly • Multiple wireless protocols • Heterogeneous computing over multiple cores – Dedicated subsystems (sensor hubs) – Increasing number of sensing subsystems – Always-on sensing • Battery technology has not kept pace with the development • Software is not, in many cases, optimized • Difficult to balance between local versus distributed processing • Difficult to control traffic across interfaces Mobile Evolution 1995 2000 2005 2010 2015 Processor Single Single Single Dual-core Quad-core and beyond, auxiliary processors, sensor hubs Cellular 2G 2.5-3G 3.5G Transition 4G generation toward 4G Standard GSM GPRS HSPA HSPA, LTE LTE, LTE-A Downlink (Mb/ 0.01 0.1 1 10 100 s) Display pixels 4 16 64 256 1024 (x1000) Communicatio - - WiFi, WiFi, WiFi, Bluetooth LE, ns modules Bluetooth Bluetooth RFID Battery 1 2 3 4 5 capacity (Wh) Software (MB) 0.1 1 10 100 1000 Example Smartphone SoC Modem Subsystem Multicore Subsystem Multimedia Subsystem LTE Adreno World KRAIT CPU KRAIT CPU GPU Modem Audio, GPS,Wi-Fi, Video HW, BT,FM Accelerator L1 Cache L1 Cache s DSP DSP DSP L2 Cache Multim. -

M-Line BROCHURE

The Novasom Industries M-line was created for those advanced multimedia applications where the computing power and the presence of specific HW accelerators are needed as much as the advanced connectivity to various kinds of displays while maintaining the classic low-level industrial connectivity. Novasom Industries M11 series, based on the new Intel Apollo Lake x5 6th generation Atom CPU with Microsoft Windows 10 and UHD (4k) video capabilities, is perfect for the typical Kiosks & Digital-Signage applications. The M7 is based on the Rockchip RK3328, a 4X A53 processor and can drive UHD (4k) displays, has USB3 & 2, HDMI and supports Android OS. Complete SBC with immediate bootstrap Native Android & Linux support O.S. (M7, M8 & M9) M8 board runs Qualcomm Snapdragon 410E with Android and Windows 10 IoT and can be connected to FHD displays. Native Window 10 and Linux (M11) Embedded UPS manager with battery and Redundant The M9, based on the Rockchip RK3399 offers an android like Power Input experience and high side multimedia application with UHD, multiple video and camera input. HD Audio output and Optical SPDIF mPCIe interface slot (M9, M7 & M11) All the M-Line boards support Linux OS. Fluidity and no scratch on Heavy UHD play RASPMOOD form factor for M7, M8 and M9: dimensions, guaranteed mechanical holes, expansion pin on strip, connector Fully certified board, visit kind and position are similar to the famous Pi Family. www.novasomindustries.com for details So if you've started with a toy-board and want to use in an industrial proposal, we are ready. -

QTEE STOR, Is Shown in Figure 4

Qualcomm Snapdragon, Qualcomm Trusted Execution Environment, Qualcomm Secure Storage Solutions, Qualcomm Secure Processing Unit, Qualcomm Secure File System, and Qualcomm Fast Trusted Storage are products of Qualcomm Technologies, Inc. and/or its subsidiaries. Qualcomm and Snapdragon are trademarks of Qualcomm Incorporated, registered in the United States and other countries. Other products and brand names may be trademarks or registered trademarks of their respective owners. The contents of this document are provided on an “as-is” basis without warranty of any kind. Qualcomm Technologies, Inc. specifically disclaims the implied warranties of merchantability and fitness for a particular purpose. Qualcomm Technologies, Inc. 5775 Morehouse Drive San Diego, CA 92121 U.S.A. © 2019 Qualcomm Technologies, Inc. and/or its affiliated companies. All Rights Reserved. Overview .............................................................................................................................. 1 Acronyms ............................................................................................................................. 2 Limitation of pure software-based solutions ...................................................................... 3 Hardware building blocks .................................................................................................... 4 Qualcomm® Trusted Execution Environment ................................................................. 4 Hardware Crypto Engine ................................................................................................ -

![Arxiv:1910.06663V1 [Cs.PF] 15 Oct 2019](https://docslib.b-cdn.net/cover/5599/arxiv-1910-06663v1-cs-pf-15-oct-2019-1465599.webp)

Arxiv:1910.06663V1 [Cs.PF] 15 Oct 2019

AI Benchmark: All About Deep Learning on Smartphones in 2019 Andrey Ignatov Radu Timofte Andrei Kulik ETH Zurich ETH Zurich Google Research [email protected] [email protected] [email protected] Seungsoo Yang Ke Wang Felix Baum Max Wu Samsung, Inc. Huawei, Inc. Qualcomm, Inc. MediaTek, Inc. [email protected] [email protected] [email protected] [email protected] Lirong Xu Luc Van Gool∗ Unisoc, Inc. ETH Zurich [email protected] [email protected] Abstract compact models as they were running at best on devices with a single-core 600 MHz Arm CPU and 8-128 MB of The performance of mobile AI accelerators has been evolv- RAM. The situation changed after 2010, when mobile de- ing rapidly in the past two years, nearly doubling with each vices started to get multi-core processors, as well as power- new generation of SoCs. The current 4th generation of mo- ful GPUs, DSPs and NPUs, well suitable for machine and bile NPUs is already approaching the results of CUDA- deep learning tasks. At the same time, there was a fast de- compatible Nvidia graphics cards presented not long ago, velopment of the deep learning field, with numerous novel which together with the increased capabilities of mobile approaches and models that were achieving a fundamentally deep learning frameworks makes it possible to run com- new level of performance for many practical tasks, such as plex and deep AI models on mobile devices. In this pa- image classification, photo and speech processing, neural per, we evaluate the performance and compare the results of language understanding, etc. -

Arm-Based Computing Platform Solutions Accelerating Your Arm Project Development

Arm-based Computing Platform Solutions Accelerating Your Arm Project Development Standard Hardware Solutions AIM-Linux & AIM-Android Services Integrated Peripherals Trusty Ecosystem QT Automation SUSI API Transportation Medical MP4 BSP NFS Video Driver LOADER Acceleration Kernel Security Boot Loader Networking www.advantech.com Key Factors for Arm Business Success Advantech’s Arm computing solutions provide an open and unified development platform that minimizes effort and increases resource efficiency when deploying Arm-based embedded applications. Advantech Arm computing platforms fulfill the requirements of power- optimized mobile devices and performance-optimized applications with a broad offering of Computer-on-Modules, single board, and box computer solutions based on the latest Arm technologies. This year, Advantech’s Arm computing will roll out three new innovations to lead embedded Arm technologies into new arena: 1. The i.MX 8 series aims for next generation computing performance and targets new application markets like AI. 2. Developing a new standard: UIO20/40-Express, an expansion interface for extending various I/Os easily and quickly for different embedded applications. 3. We are announcing the Advantech AIM-Linux and AIM-Android, which provide unfiled BSP, modularized App Add-Ons, and SDKs for customers to accelerate their application development. Standardized Hardware Solutions • Computer on Module • Single Board Computer • Computer Box AIM-Linux AIM-Linux & AIM-Android • Unified Embedded Platforms AIM-Android • App Add-Ons -

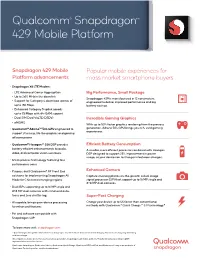

Qualcomm® Snapdragon™ 429 Mobile Platform

Qualcomm® Snapdragon™ 429 Mobile Platform Snapdragon 429 Mobile Popular mobile experiences for Platform advancements mass market smartphone buyers • Snapdragon X6 LTE Modem: o LTE Advanced Carrier Aggregation Big Performance, Small Package o Up to 2x10 MHz in the downlink Snapdragon 429 is manufactured in 12 nanometers, o Support for Category 4 download speeds of engineered to deliver improved performance and big up to 150 Mbps battery savings. o Enhanced Category 5 uplink speeds up to 75 Mbps with 64-QAM support o Dual SIM Dual VoLTE (DSDV) Incredible Gaming Graphics o eMBMS With up to 50% faster graphics rendering from the previous • Qualcomm® Adreno™ 504 GPU engineered to generation, Adreno 504 GPU brings you rich, vivid gaming experiences. support stunning, life-like graphics and gaming at lower power. • Qualcomm® Hexagon™ 536 DSP provides E cient Battery Consumption battery-ecient enhancements to audio, A smaller, more ecient processor combined with Hexagon video, and computer vision use cases. DSP designed to support 25% improvement in power usage, so your device can last longer in between charges. • 12 nm process technology featuring four performance cores • Purpose-built Qualcomm® RF Front End Enhanced Camera solutions for implementing Snapdragon All Capture stunning photos on-the-go with a dual image Mode for China and emerging regions. signal processor (ISP) that support up to 16 MP single and 8+8 MP dual cameras. • Dual ISPs supporting up to 16 MP single and 8+8 MP dual cameras with enhanced auto- focus and zero shutter lag. Super-Fast Charging • AI capable, bringing on-device processing Charge your device up to 4X faster than conventional ® for enhanced features methods with Qualcomm Quick Charge™ 3.0 technology.* • Pin and soware compatible with Snapdragon 439 To learn more visit: snapdragon.com * Quick Charge is designed to allow devices to charge up to four times faster than conventional charging. -

(12) Patent Application Publication (10) Pub. No.: US 2015/0254416 A1 Shih (43) Pub

US 20150254416A1 (19) United States (12) Patent Application Publication (10) Pub. No.: US 2015/0254416 A1 Shih (43) Pub. Date: Sep. 10, 2015 (54) METHOD AND SYSTEM FOR PROVIDING (52) U.S. Cl. MEDICAL ADVICE CPC .......... G06F 19/3425 (2013.01); G06F 19/322 (2013.01) (71) Applicant: ClickMedix, Gaithersburg, MD (US) (72) Inventor: Ting-Chih Shih, Rockville, MD (US) (57) ABSTRACT (73) Assignee: CLICKMEDIX, Gaithersburg, MD A method and system for providing medical services wherein (US) a server establishes a wireless connection with a mobile device or computer of a user. The mobile device or computer (21) Appl. No.: 14/199,559 has already been provided with an application for the entry of (22) Filed: Mar. 6, 2014 user information. The server receives encrypted user infor mation from the mobile device or computer, decrypts the user Publication Classification information, and forwards the user information to experts selected on the basis of the user information. The server (51) Int. Cl. collects responses from the experts, and provides expert G06F 9/00 (2006.01) advice to the user of the mobile device or computer. NTERNET SERVICE SERVER PROVIDER 25 Patent Application Publication Sep. 10, 2015 Sheet 1 of 10 US 2015/0254416 A1 S. OO L gy2 O ch : 2 > S 2 v 9 --- ---m-m- Patent Application Publication Sep. 10, 2015 Sheet 2 of 10 US 2015/0254416 A1 ZI IZ| -----———————? |------ OT Patent Application Publication Sep. 10, 2015 Sheet 3 of 10 US 2015/0254416 A1 dXB:LHB Patent Application Publication Sep. 10, 2015 Sheet 4 of 10 US 2015/0254416 A1 ——— ?II || | | || | |NOIIVWHOHNI Å ||GO?I Nodisva HITV3HLNBILVd ______.ISOH______ ~~~~}dno89v10BTES!| S183dXBHO| |~\~~~~|||| †7·314 || | | || | ZO? A | } }} | }{ | l Patent Application Publication US 2015/0254416 A1 ?euauss)| Patent Application Publication Sep. -

Snapdragon Product Brief 630.Indd

QUALCOMM® User Experiences TM SNAPDRAGON Outstanding image quality The 14-bit Qualcomm Spectra 160 ISP supports capture of up to 24 megapixels with zero shutter lag, and off ers smooth zoom, fast autofocus and 630 true-to-life colors for outstanding image quality. MOBILE PLATFORM Enhanced graphics Snapdragon 630 mobile and 3D gaming platform advancements: With up to 30% improved performance1, Adreno 508 GPU supports lifelike visuals and more eff icient + Qualcomm Spectra™ 160 Camera ISP: rendering of advanced 3D graphics. Developers gain Dual 14-bit ISPs support up to 24MP access to the latest graphics APIs. single or dual 13MP cameras for the ultimate photography and videography experience Faster, consistent 1 + Qualcomm® Adreno™ 508 GPU: Up to connection 30% better graphics and enhanced 2 1 With LTE downlink speeds up to 2X faster , the gaming performance for lifelike visuals Snapdragon X12 modem is engineered to quickly and more eff icient rendering of download a favorite TV show or an entire album advanced 3D graphics worth of songs in more locations, with greater + Qualcomm® Hexagon™ 642 DSP consistency. designed to provide battery-eff icient enhancements to audio, video, and computer vision use cases On device machine + Snapdragon X12 LTE modem: Industry learning leading connectivity with LTE download Qualcomm® Machine Learning Platform supports speeds up to 600 Mbps and integrated high performance, intelligent, on-device processes, 802.11ac Wi-Fi with MU-MIMO utilizing heterogenous compute capabilities to power immersive and engaging experiences. + Advanced RF front end technologies including Qualcomm® TruSignal™ adaptive antenna tuning with carrier aggregation and Envelope Tracking Power when it’s + Qualcomm® Quick Charge™ 4 needed most technology: 20% faster, 30% more Do more throughout the day: stream music and eff icient than previous generation, videos, play games, talk, all while getting 2 charge from zero to 50% in 15 minutes extended battery life. -

Qualcomm® Snapdragon™

The new architectures of the Qualcomm® Snapdragon™ 712 Mobile Platform are engineered to optimize key experiences including AI, gaming, performance, and power for some of the most in-demand mobile devices. Qualcomm® Faster performance, better battery life1 ™ Snapdragon Now you can do more on a single charge. With a 10 nm processor, architecture enhancements and core improvements, you’ll experience a 10% performance uplift across gaming, web browsing and more1. When it’s time to recharge, rely on Qualcomm® Quick Charge™ 4+ technology to take your phone from 0% to 50% in 15 minutes!2 • Qualcomm Spectra™ 250 ISP and Qualcomm® Adreno™ 616 GPU enable significant power improvements 712 • Architectural improvements across the CPU, GPU, DSP, and more help bring performance to a new level Mobile Platform AI helps your device work smarter, not harder Our 3rd generation multi-core Qualcomm® AI Engine delivers improvements for mobile AI applications. Devices powered by the Snapdragon 712 can better manage battery usage, auto-adjust settings for pictures, and understand your voice cues more naturally. • Supports highly-advanced on-device AI • Qualcomm® Hexagon™ Vector architecture designed to execute neural networks more efficiently • Optimizations for fixed and floating-point networks on Qualcomm® Kryo™ CPU and Adreno DSP Rich on-device experiences Let your entertainment take you places. The Adreno 616 GPU is designed for exceptional console- like gaming and cinematic movie experiences on your smartphone. With 10% faster graphics rendering1 and 4K HDR playback, you’ll be immersed in over 1 billion shades of color—delivered with an incredible audio experience. • Wi-Fi latency manager for responsive gaming • Qualcomm® aptX™ Adaptive Audio and Qualcomm Aqstic™ Audio Technologies deliver smooth, crystal-clear audio More stunning photos and videos per charge Capture vibrant, high-quality photos and videos thanks to new architectures in the 2nd generation Qualcomm Spectra ISP. -

Gables: a Roofline Model for Mobile Socs

2019 IEEE International Symposium on High Performance Computer Architecture (HPCA) Gables: A Roofline Model for Mobile SoCs Mark D. Hill∗ Vijay Janapa Reddi∗ Computer Sciences Department School Of Engineering And Applied Sciences University of Wisconsin—Madison Harvard University [email protected] [email protected] Abstract—Over a billion mobile consumer system-on-chip systems with multiple cores, GPUs, and many accelerators— (SoC) chipsets ship each year. Of these, the mobile consumer often called intellectual property (IP) blocks, driven by the market undoubtedly involving smartphones has a significant need for performance. These cores and IPs interact via rich market share. Most modern smartphones comprise of advanced interconnection networks, caches, coherence, 64-bit address SoC architectures that are made up of multiple cores, GPS, and many different programmable and fixed-function accelerators spaces, virtual memory, and virtualization. Therefore, con- connected via a complex hierarchy of interconnects with the goal sumer SoCs deserve the architecture community’s attention. of running a dozen or more critical software usecases under strict Consumer SoCs have long thrived on tight integration and power, thermal and energy constraints. The steadily growing extreme heterogeneity, driven by the need for high perfor- complexity of a modern SoC challenges hardware computer mance in severely constrained battery and thermal power architects on how best to do early stage ideation. Late SoC design typically relies on detailed full-system simulation once envelopes, and all-day battery life. A typical mobile SoC in- the hardware is specified and accelerator software is written cludes a camera image signal processor (ISP) for high-frame- or ported.