HP-Measure-1993-05-06.Pdf

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Inside HP Labs... O Dolores Hall Fashions an Array of Light Emitting-Diodes at the HPA Division in Palo Alto

Who let the cat out of the bag? Overall, our size, complexity and success tors have been given extra time to rethink make our activities increasingly news and execute their strategy. Your field sales worthy-whether we want that or not. people quickly sense the situation and be To see how it works, put yourself in gm to concentrate on other products. And the place of a division marketing manager: you may even have legal problems. All in Through a combination of marketing all it's going to cost a bundle-in loss of tactics, including news releases, press con sales, of company reputation and of sense ferences, industry showings and advertis of achievement. "Loose as a goose!" ing programs, plus product availability Such potential consequences are by and sales force briefiings, you have plotted no means limited to product introductions. "Leaky as a sieH~" a strategy that you expect will enable your The subject may concern new orders, dol at secrets? Arc there an}' left product to hit the market with maximum lar volume of sales, negotiations of various nd here?" impact. Your goal is to have the world of kinds, price changes, expansion plans, im customers aU of a sudden buzzing with portant contracts, and technical develop the news, clamoring to see and buy-and ments. Leaks of this kind of information getting a big jump on the competition. can be of great interest to the press-and Those comments may sound flippant, Instead, a number of weeks prior to very beneficial and instructive to com but actually they represent serious ap the grand unveiling, Corporate Public petitors. -

Software Orchestration of Instruction Level Parallelism on Tiled Processor Architectures

Software Orchestration of Instruction Level Parallelism on Tiled Processor Architectures by Walter Lee B.S., Computer Science Massachusetts Institute of Technology, 1995 M.Eng., Electrical Engineering and Computer Science Massachusetts Institute of Technology, 1995 Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of MiASSACHUSETTS INST IJUE DOCTOR OF PHILOSOPHY OF TECHNOLOGY at the OCT 2 12005 MASSACHUSETTS INSTITUTE OF TECHNOLOGY LIBRARIES May 2005 @ 2005 Massachusetts Institute of Technology. All rights reserved. Signature of Author: Department of Electrical Engineering and Computer Science A May 16, 2005 Certified by: Anant Agarwal Professr of Computer Science and Engineering Thesis Supervisor Certified by: Saman Amarasinghe Associat of Computer Science and Engineering Thesis Supervisor Accepted by: Arthur C. Smith Chairman, Departmental Graduate Committee BARKER ovlv ". Software Orchestration of Instruction Level Parallelism on Tiled Processor Architectures by Walter Lee Submitted to the Department of Electrical Engineering and Computer Science on May 16, 2005 in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in Electrical Engineering and Computer Science ABSTRACT Projection from silicon technology is that while transistor budget will continue to blossom according to Moore's law, latency from global wires will severely limit the ability to scale centralized structures at high frequencies. A tiled processor architecture (TPA) eliminates long wires from its design by distributing its resources over a pipelined interconnect. By exposing the spatial distribution of these resources to the compiler, a TPA allows the compiler to optimize for locality, thus minimizing the distance that data needs to travel to reach the consuming computation. -

Emerging Technologies Multi/Parallel Processing

Emerging Technologies Multi/Parallel Processing Mary C. Kulas New Computing Structures Strategic Relations Group December 1987 For Internal Use Only Copyright @ 1987 by Digital Equipment Corporation. Printed in U.S.A. The information contained herein is confidential and proprietary. It is the property of Digital Equipment Corporation and shall not be reproduced or' copied in whole or in part without written permission. This is an unpublished work protected under the Federal copyright laws. The following are trademarks of Digital Equipment Corporation, Maynard, MA 01754. DECpage LN03 This report was produced by Educational Services with DECpage and the LN03 laser printer. Contents Acknowledgments. 1 Abstract. .. 3 Executive Summary. .. 5 I. Analysis . .. 7 A. The Players . .. 9 1. Number and Status . .. 9 2. Funding. .. 10 3. Strategic Alliances. .. 11 4. Sales. .. 13 a. Revenue/Units Installed . .. 13 h. European Sales. .. 14 B. The Product. .. 15 1. CPUs. .. 15 2. Chip . .. 15 3. Bus. .. 15 4. Vector Processing . .. 16 5. Operating System . .. 16 6. Languages. .. 17 7. Third-Party Applications . .. 18 8. Pricing. .. 18 C. ~BM and Other Major Computer Companies. .. 19 D. Why Success? Why Failure? . .. 21 E. Future Directions. .. 25 II. Company/Product Profiles. .. 27 A. Multi/Parallel Processors . .. 29 1. Alliant . .. 31 2. Astronautics. .. 35 3. Concurrent . .. 37 4. Cydrome. .. 41 5. Eastman Kodak. .. 45 6. Elxsi . .. 47 Contents iii 7. Encore ............... 51 8. Flexible . ... 55 9. Floating Point Systems - M64line ................... 59 10. International Parallel ........................... 61 11. Loral .................................... 63 12. Masscomp ................................. 65 13. Meiko .................................... 67 14. Multiflow. ~ ................................ 69 15. Sequent................................... 71 B. Massively Parallel . 75 1. Ametek.................................... 77 2. Bolt Beranek & Newman Advanced Computers ........... -

Hewlett-Packard Company ("HP") 3000 Hanover Street Palo Alto, California 94304

The NASDAQ Stock Market LLC Form 1 - Exhibit C, Tab 29 Name and Address: Hewlett-Packard Company ("HP") 3000 Hanover Street Palo Alto, California 94304 Details of organization: Stock corporation organized under in its current form under the General Corporation law of the State of Delaware on February 11, 1998. Contractual relationship: The Nasdaq Stock Market, Inc. and HP are parties to Master Lease and Financing Agreements dated October 26,2004 and October 27,2004 and an Enterprise Site License Agreement dated November 15,2004, and 11/15/04. Business or functions: Hewlett-Packard provides the servers and operating systems software for the systems that comprise the Nasdaq Market Center and securities information processor. Certificate of Incorporation: Attached as Exhibit A. By-Laws: Attached as Exhibit B. Officers, Governors, and Standing Committee Members Attached as Exhibit C. I, HARRIET SMITH WINDSOR, SECRETARY OF STATE OF THE STATE OF DELAWARE, DO HEREBY CER!CIPY THE ATTACHED IS A TRUE AND CORRECT COPY OF THE CERTIFICATE OF INCORPORATION OF "HBWLETT-PACRARD COMPANY", FILED IN THIS OFFICE ON THE ELEVENTH DAY OF FEBRUARY, A.D. 1998, AT 5 O'CLOCK P.M. 5d-%b Huric Smith Windsor. kr~yof State 2858384 8100 AUTBEWTICATION: 1665671 020170126 * DATE: 03-14-02 - STATE OF DWiAMARE SZCRETARP OF STAR DXVfSICHI OF CORRaRPTIWS FZW 05: 00 FW 02/11/2998 981055490 - 2858384 CERTIFICATE OF INCORPORATION HEWLET'#'-PACKARD COMPANY ARTICLE I The name of this corporation is Hewlett-Packard Company (the "Corporationn). The addresa of the Corporation's registered office in the State of Ddawan is 1209 Orange Strat, Wilmington, Delaware 19801, County ofNew Castle. -

January-February 1991

HP Labs: singular! 3 For 2:) y<'ars, HP Lahoratories ha.... (pd HP's long-rangt' rest'arch. page 10 Driving up quality at Ford 10 Ford amI liP team to develop an ele<.'troni<- toolhox for automohiles. Your turn 14 History in a box 15 HP's profl'ssional ar('hives is a trt'aSUfC'-trov(' of information. Open for business: Silicon Valley's new garage 19 A million people a year art' expected to visit a new high-tl'eh {·xhihil. People 22 ,Jim Hanl('Y's inten'sts range from high tN'h to primitiw art. No room for dinosaurs 25 1900 was a da....sie exampll' ofttw constant Ill'ell to adapt to change. Letter from John Young 27 John ('xplains hew,; HP's new organizational structure is taking shape. ExtraMeasure 29 MEASURE Editor AssocIate edrtor Aft D,rector GraphiC des,gner Crrculat.on JoyCoIemon Belly Gerard Annerte Yc10VllZ Thomas J Brown Kathleen Miller Measure IS published SI' t'mes a year lor emplayees ana assoclctes 01 HewleN·Packard Compo<1y Produced by Corporate PublIC RelaIJon\ Employee CommunlcaIJon\ Department Brad Whll'worttl manager Addless correspondence 10 Measure....ew'e"·Pac~ard Companv. WBR PO Box 10301 Palo Alto. Calitornla 9<1303-0890 UY>. (.l15) 857-4146 Report changes ol address 10 yOU' local perSOnnel deportment c Copynghl 1991 by HewlelT Pac~ard Company MoIenal may be reprinted wllh permiSSIon Member. Inlerna1ranal Association of BUSiness Communicators Hewlert·Packard Company IS an International monufacturer 01 measurement ana computaTion products and sy.;lems recognized lOt excellence In quality and support The compony's products and services ore used ,n Industry. -

Exploiting Choice: Instruction Fetch and Issue on an Implementable Simultaneous Multithreading Processor

Exploiting Choice: Instruction Fetch and Issue on an Implementable Simultaneous Multithreading Processor ¡ Dean M. Tullsen , Susan J. Eggers , Joel S. Emer , Henry M. Levy , ¡ Jack L. Lo , and Rebecca L. Stamm ¡ Dept of Computer Science and Engineering Digital Equipment Corporation University of Washington HLO2-3/J3 Box 352350 77 Reed Road Seattle, WA 98195-2350 Hudson, MA 01749 Abstract an SMT processor to achieve signi®cantly higher throughput than either a wide superscalar or a multithreaded processor. That paper Simultaneous multithreading is a technique that permits multiple also demonstrated the advantages of simultaneous multithreading independent threads to issue multiple instructions each cycle. In over multiple processors on a single chip, due to SMT's ability to previous work we demonstrated the performance potential of si- dynamically assign execution resources where needed each cycle. multaneous multithreading, based on a somewhat idealized model. Those results showed SMT's potential based on a somewhat ide- In this paper we show that the throughput gains from simultaneous alized model. This paper extends that work in four signi®cant ways. multithreading can be achieved without extensive changes to a con- First, we demonstrate that the throughput gains of simultaneous mul- ventional wide-issue superscalar, either in hardware structures or tithreading are possible without extensive changesto a conventional, sizes. We present an architecture for simultaneous multithreading wide-issue superscalar processor. We propose an architecture that that achieves three goals: (1) it minimizes the architectural impact is more comprehensive, realistic, and heavily leveraged off existing on the conventional superscalar design, (2) it has minimal perfor- superscalar technology. -

Agood Forty Years

Agood forty years... No trumpets blew when Dave Packard and Bill Hewlett walked up to receive their 40th year service awards from John Young on December 18. A few reminis cences and they turned to the business at hand: passing out 25·, 30- and 35-year I awards to other HP veterans gathered for the annual Bay Area awards luncheon. Of course, technically speaking, these weren't even the first 40-year awards handed out at Hewlett-Packard- that honor had already gone to a handful of Waltham Division employees who were credited with years spent working for a venerable acquisition, the Sanborn Company. And yet, those 40-year awards to Dave and Bill last month were clearly something quite special in the history of the company they founded four decades ago. For a few minutes the co-founders thought back to those early days in Palo Alto when they were beginning to build devices in a garage workshop during Dave Packard and Bill Hewlett mark 40 years 01 Hewlett-Packard service with a handshake. The ollicial starting date 01 the company's co-launders was January 1,1939. spare hours sandwiched between graduate study and work at Stanford University. The idea of having their own com pany had occurred to the young men five years earlier when they were engineering undergraduates together at Stanford. By the end of 1938 they were halfway to that goal-Dave Packard and his wife Lucile living in an apartment in downtown Palo Cover: After receiving their 40-year Alto, Bill Hewlett batching in a cottage service awards last month, HP founders Dave Packard (left) and Bill Hewlett (right) looked over some photographs of the company's earlier days. -

Agilent Technologies' Spin Make It Acceptable for Printing'?" with Any Employees

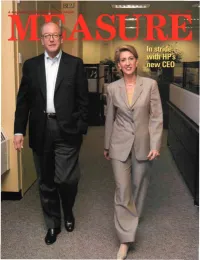

FROM THE EDITOR can't say exactly when I became meeting to talk ""ith customers or a big fan of CEO Lew Platt, but visitors-and ended up staying I think it was one day in Febru longer than either of you imagined ary 1993. he would. He cares deeply about. I had written a MEASURE article the personal tonch. about HP's order-fulfillment problems. For the past few years, Lew has A couple of senior executives felt the gotten into the habit of eating lunch (one was too honest. Lew was asked with several of us from HP Communi to arbitrate the dispute. In many cations. I think he enjoyed the fact companies, that would have been that we rarely talk about work. an easy decision: senior executives 1, Name a topic-sports, current events, employee publication O. fine wine, photography, literature, Lew walked over to my office and wombats-and Lew invmiably explained-almost apologetically knows more about it than anyone On the cover: Carly Fiorina, that the article had some problems at the table. HP's new president and and needed to be pulled from the Here's a guy who regularly coun CEO, sets a fast and ener· getic pace for the company magazine, which was due to go to the sels and dines with CEOs, world lead to follow. Retiring President printer within a few days. I countered, ers and royalty; yet, he seems equally and CEO Lew Platt is non "You mean there's no middle ground? happy eating chicken strips and fries executive chairman of the HP Board while overseeing There's no way to edit the story to in the company cafeteria and t.alking Agilent Technologies' spin make it acceptable for printing'?" with any employees. -

Memristor Devices: Fabrication, Characterization, Simulation

MEMRISTOR DEVICES: FABRICATION, CHARACTERIZATION, SIMULATION, AND CIRCUIT DESIGN Thesis Submitted to The School of Engineering of the UNIVERSITY OF DAYTON In Partial Fulfillment of the Requirements for The Degree of Master of Science in Electrical Engineering By Chris Yakopcic Dayton, Ohio August, 2011 MEMRISTOR DEVICES: FABRICATION, CHARACTERIZATION, SIMULATION, AND CIRCUIT DESIGN Name: Yakopcic, Chris APPROVED BY: _________________________________ _________________________________ Tarek M. Taha, Ph.D. Guru Subramanyam, Ph.D. Advisory Committee Chairman Committee Member Associate Professor Chair and Professor Electrical and Computer Engineering Electrical and Computer Engineering _________________________________ Andrew Sarangan, Ph.D. Committee Member Associate Professor Electro-Optics _________________________________ _________________________________ John G. Weber, Ph.D. Tony E. Saliba, Ph.D. Associate Dean Dean, School of Engineering School of Engineering & Wilke Distinguished Professor ii ©Copyright by Chris Yakopcic All Rights Reserved 2011 iii ABSTRACT MEMRISTOR DEVICES: FABRICATION, CHARACTERIZATION, SIMULATION, AND CIRCUIT DESIGN Name: Yakopcic, Chris University of Dayton Advisor: Dr. Tarek M. Taha Significant interest has been placed on developing systems based on memristors since the initial fabrication by HP Labs in 2008 [1]. The memristor is a nanoscale device with dynamic resistance that is able to retain the last programmed resistance value after power is removed from the device. This property shows that the memristor can be used as a non-volatile memory component, and has potential to enhance many types of systems, such as high density memory, and neuromorphic computing architectures. This thesis presents the fabrication and characterization results obtained based memristor devices developed at the University of Dayton. In addition, a comparison between the existing memristor device models was completed to show how the memristor can be used in a multistate operation. -

Register Assignment for Software Pipelining with Partitioned Register Banks

Register Assignment for Software Pipelining with Partitioned Register Banks Jason Hiser Steve Carr Philip Sweany Department of Computer Science Michigan Technological University Houghton MI 49931-1295 ¡ jdhiser,carr,sweany ¢ @mtu.edu Steven J. Beaty Metropolitan State College of Denver Department of Mathematical and Computer Sciences Campus Box 38, P. O. Box 173362 Denver, CO 80217-3362 [email protected] Abstract Trends in instruction-level parallelism (ILP) are putting increased demands on a machine’s register resources. Computer architects are adding increased numbers of functional units to allow more instruc- tions to be executed in parallel, thereby increasing the number of register ports needed. This increase in ports hampers access time. Additionally, aggressive scheduling techniques, such as software pipelining, are requiring more registers to attain high levels of ILP. These two factors make it difficult to maintain a single monolithic register bank. One possible solution to the problem is to partition the register banks and connect each functional unit to a subset of the register banks, thereby decreasing the number of register ports required. In this type of architecture, if a functional unit needs access to a register to which it is not directly connected, a delay is incurred to copy the value so that the proper functional unit has access to it. As a consequence, the compiler now must not only schedule code for maximum parallelism but also for minimal delays due to copies. In this paper, we present a greedy framework for generating code for architectures with partitioned register banks. Our technique is global in nature and can be applied using any scheduling method £ This research was supported by NSF grant CCR-9870871 and a grant from Texas Instruments. -

A VLIW Architecture for a Trace Scheduling Compiler

A VLIW Architecture for a Trace Scheduling Compiler Robert P. Colwell, Robert P. Nix, John J. O'Donnell, David B. Papworth, Paul K. Rodman Multiflow Computer 175 North Main Street Branford, CT. 06405 (203) 488-6090 1. Abstract Very Long Instruction Word (VLIW) architectures were prom- Researchers at Yale, however, Fish83,Elli86 found that fine- ised to deliver far more than the factor of two or three that grained parallelism could be exploited by a sufficiently clever current architectures achieve £rom overlapped execution. Using compiler to greatly increase the execution throughput of a suit- a new type of compiler which compacts ordinary sequential code ably constructed computer. The compiler exploited statistical into long instruction words, a VLIW machine was expected to information about program branching to allow searching beyond provide from ten to thirty times the performance of a more con- the obvious basic blocks in a program (e.g., past conditional ventional machine built of the same implementation technology. branches) for operations that could be performed in parallel with other possibly-unrelated operations. Fish79 Logical incon- Multiflow Computer, Inc., has now built a VLIW called the sistencies that were created by these motions were corrected by TRACE'" along with its companion Trace Scheduling" com- special compensation code inserted by the compiler. pacting compiler. This new machine has fulfilled the perfor- mance promises that were made. Using many fast functional These researchers labelled their proposed architecture -

2006 HP Annual Report Dear Fellow Stockholders

2006 HP Annual Report [Cover depicts a solid green background with a thin white horizontal stretch bar wrapping around the cover. The HP logo sits in the lower right-hand corner. 2006 HP Annual Report sits within the white bar.] Dear Fellow Stockholders, HP made solid progress this past year toward our goal of becoming the world’s leading IT company. We want to create the best technology on the planet — and be the best at selling, servicing and supporting that technology. To get there, we are focusing our portfolio of products and services on simplifying our customers’ experiences with technology and helping them do what they want to do, wherever they are. For example, in our enterprise business, we are working on helping our customers run their businesses with automated, super-efficient data centers. In our imaging and printing business, we are helping customers more rapidly achieve the benefits of printing from a digital source in areas such as commercial printing and retail photo printing. And in our personal systems business, we are working to empower customers with simple, always-connected, mobile computing experiences at work, at home or on the go. While we worked toward these strategic goals, we also improved the health of our financials. Our revenue increased 6 percent in fiscal year 2006 to $91.7 billion. Non-GAAP EPS increased 47 percent to $2.38¹, and GAAP diluted EPS increased 166 percent to $2.18. And we generated record cash flow from operations of $11.4 billion. We also achieved the most balanced profit mix by business group that HP has seen in years.