Silicon Fabrication Process Pdf

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

On-Wafer Fabrication of Cavity Mirrors for Ingan-Based Laser Diode Grown

www.nature.com/scientificreports OPEN On-wafer fabrication of cavity mirrors for InGaN-based laser diode grown on Si Received: 25 January 2018 Junlei He1,2, Meixin Feng1,3, Yaozong Zhong1, Jin Wang1,4, Rui Zhou1,2, Hongwei Gao1,3, Yu Accepted: 17 April 2018 Zhou1,3, Qian Sun1,2,3, Jianxun Liu1, Yingnan Huang1, Shuming Zhang1,2, Huaibing Wang1, Published: xx xx xxxx Masao Ikeda1 & Hui Yang1,2 Direct bandgap III-V semiconductor lasers grown on silicon (Si) are highly desired for monolithic integration with Si photonics. Fabrication of semiconductor lasers with a Fabry–Pérot cavity usually includes facet cleavage, however, that is not compatible with on-chip photonic integration. Etching as an alternative approach holds a great advantage in preparing cavity mirrors with no need of breaking wafer into bars. However, gallium nitride (GaN) sidewalls prepared by dry etching often have a large roughness and etching damages, which would cause mirror loss due to optical scattering and carrier injection loss because of surface non-radiative recombination. A wet chemical polishing process of GaN sidewall facets formed by dry etching was studied in detail to remove the etching damages and smooth the vertical sidewalls. The wet chemical polishing technique combined with dry etching was successfully applied to the on-wafer fabrication of cavity mirrors, which enabled the realization of room temperature electrically injected InGaN-based laser diodes grown on Si. Silicon photonics call for electrically injected semiconductor laser diodes (LDs) as on-chip light sources1–3. When grown on Si, III-nitride (Al, Ga, In)N semiconductors with a direct-band emission wavelength ranging from 0.2 to 1.8 μm ofer a new approach for achieving on-chip lasers4–7. -

Inside HP Labs... O Dolores Hall Fashions an Array of Light Emitting-Diodes at the HPA Division in Palo Alto

Who let the cat out of the bag? Overall, our size, complexity and success tors have been given extra time to rethink make our activities increasingly news and execute their strategy. Your field sales worthy-whether we want that or not. people quickly sense the situation and be To see how it works, put yourself in gm to concentrate on other products. And the place of a division marketing manager: you may even have legal problems. All in Through a combination of marketing all it's going to cost a bundle-in loss of tactics, including news releases, press con sales, of company reputation and of sense ferences, industry showings and advertis of achievement. "Loose as a goose!" ing programs, plus product availability Such potential consequences are by and sales force briefiings, you have plotted no means limited to product introductions. "Leaky as a sieH~" a strategy that you expect will enable your The subject may concern new orders, dol at secrets? Arc there an}' left product to hit the market with maximum lar volume of sales, negotiations of various nd here?" impact. Your goal is to have the world of kinds, price changes, expansion plans, im customers aU of a sudden buzzing with portant contracts, and technical develop the news, clamoring to see and buy-and ments. Leaks of this kind of information getting a big jump on the competition. can be of great interest to the press-and Those comments may sound flippant, Instead, a number of weeks prior to very beneficial and instructive to com but actually they represent serious ap the grand unveiling, Corporate Public petitors. -

A Review of Different Etching Methodologies and Impact of Various Etchants in Wet Etching in Micro Fabrication

ISSN (Online) : 2319 – 8753 ISSN (Print) : 2347 - 6710 International Journal of Innovative Research in Science, Engineering and Technology An ISO 3297: 2007 Certified Organization, Volume 3, Special Issue 1, February 2014 International Conference on Engineering Technology and Science-(ICETS’14) On 10th & 11th February Organized by Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India A Review of Different Etching Methodologies and Impact of various etchants in Wet Etching in Micro Fabrication Benjamin. J1, Grace Jency. J2, Vijila. G3 Department of ECE, Karunya University, Karunya Nagar, Coimbatore – 641114, India1, 2, 3 Abstract-- The concept of miniaturization was each and every wafer undergo a lot of etching process. introduced because of advancement in science and The material which is used to protect the wafer from the technology during 1980s. These miniaturized etchants is known as the masking material, which is used structures and designs are of high significance for in many etching steps to resist etching. This masking making up with the macroscopic technology, for the material can be a photoresist and it is patterned using sake of interfacing with microscopic world. The photolithography.Etching can also be referred as making fabrication of micro structures and designs which are cavities and these cavities should have specific depth the advanced applications of micro fabrication are according to the purposes. The depth of such cavities used for the process of micromachining structures in produced can be controlled by etching time and the three dimensions as it is essential for interfacing with etching rate. -

Hewlett-Packard Company ("HP") 3000 Hanover Street Palo Alto, California 94304

The NASDAQ Stock Market LLC Form 1 - Exhibit C, Tab 29 Name and Address: Hewlett-Packard Company ("HP") 3000 Hanover Street Palo Alto, California 94304 Details of organization: Stock corporation organized under in its current form under the General Corporation law of the State of Delaware on February 11, 1998. Contractual relationship: The Nasdaq Stock Market, Inc. and HP are parties to Master Lease and Financing Agreements dated October 26,2004 and October 27,2004 and an Enterprise Site License Agreement dated November 15,2004, and 11/15/04. Business or functions: Hewlett-Packard provides the servers and operating systems software for the systems that comprise the Nasdaq Market Center and securities information processor. Certificate of Incorporation: Attached as Exhibit A. By-Laws: Attached as Exhibit B. Officers, Governors, and Standing Committee Members Attached as Exhibit C. I, HARRIET SMITH WINDSOR, SECRETARY OF STATE OF THE STATE OF DELAWARE, DO HEREBY CER!CIPY THE ATTACHED IS A TRUE AND CORRECT COPY OF THE CERTIFICATE OF INCORPORATION OF "HBWLETT-PACRARD COMPANY", FILED IN THIS OFFICE ON THE ELEVENTH DAY OF FEBRUARY, A.D. 1998, AT 5 O'CLOCK P.M. 5d-%b Huric Smith Windsor. kr~yof State 2858384 8100 AUTBEWTICATION: 1665671 020170126 * DATE: 03-14-02 - STATE OF DWiAMARE SZCRETARP OF STAR DXVfSICHI OF CORRaRPTIWS FZW 05: 00 FW 02/11/2998 981055490 - 2858384 CERTIFICATE OF INCORPORATION HEWLET'#'-PACKARD COMPANY ARTICLE I The name of this corporation is Hewlett-Packard Company (the "Corporationn). The addresa of the Corporation's registered office in the State of Ddawan is 1209 Orange Strat, Wilmington, Delaware 19801, County ofNew Castle. -

Etch Overview for Microsystems Primary Knowledge Participant Guide

Etch Overview for Microsystems Primary Knowledge Participant Guide Description and Estimated Time to Complete This Learning Module introduces the most common etch processes used in the fabrication of microsystems. Activities allow you to demonstrate your understanding of the terminology and basic concepts of these processes. This unit provides an overview of the etch processes as they apply to the fabrication of Microsystems or Microelectromechanical Systems (MEMS). It is designed to provide basic information on the etch processes and how they are used in the fabrication of MEMS. This unit will introduce you to etch terminology, purpose and processes. Additional instructional units provide more in-depth discussion of the topics introduced in this overview. Estimated Time to Complete Allow at least 30 minutes to review. Southwest Center for Microsystems Education (SCME) Page 1 of 21 Fab_Etch_PK00_PG_April2017.docx Etch Overview PK Introduction Pattern Transfer For microsystems fabrication etch is a process that removes select materials from • the wafer's surface, • below the wafer's surface, or • from within the substrate. The etch process normally follows photolithography or deposition during which a protective masking layer is applied to the wafer's surface. The protective masking layer is used to identify the material to be etched and to protect material that is to remain. The figure labeled “Pattern Transfer,” illustrates a mask pattern transferred into a photosensitive layer, shown in red (masking layer), on the wafer's surface (Photolithography Process). During the Etch Process (right), that pattern is transferred into the surface layer, removing exposed areas of the surface layer and leaving areas in the underlying layer open to a subsequent process step. -

High Resolution Inductively Coupled Plasma Etching of 30 Nm Lines and Spaces in Tungsten and Silicon Andrew L

High resolution inductively coupled plasma etching of 30 nm lines and spaces in tungsten and silicon Andrew L. Goodyeara) and Sinclair Mackenzie Oxford Instruments Plasma Technology, North End, Yatton, Bristol, United Kingdom Deirdre L. Olynick and Erik H. Anderson Lawrence Berkeley National Laboratory, Berkeley, California ͑Received 1 June 2000; accepted 23 August 2000͒ Dry etching of 30 nm features was investigated for x-ray and integrated electronics applications. These typically require etching of either a tungsten absorber layer or a silicon mold. Through the use of an inductively coupled plasma source and accurate control over substrate temperature it was possible to achieve highly anisotropic patterning of tungsten and silicon. Densely patterned features as small as 30 nm and at pitches of 70 nm were etched in tungsten and silicon, to depths of 100 and 200 nm, respectively. © 2000 American Vacuum Society. ͓S0734-211X͑00͒18406-9͔ I. INTRODUCTION takes this process further by producing the densely packed fine features with better sidewalls and higher aspect ratios. Patterning of sub-100 nm features has become essential This is critical for the production of the highest resolution for advanced research and development in electronics, op- x-ray optics. tics, and material science applications. This is especially true The etching of these fine features requires advanced and for x-ray applications such as microscopy zone plate lenses. sophisticated processes and equipment. The high ion density, The critical steps in the production of densely packed sub- low pressure ICP etch regime is one of the few ways to 100 nm features for x-ray applications are high resolution provide highly anisotropic profiles with excellent control e-beam lithography and precisely controlled dry etching of over selectivity to mask materials. -

January-February 1991

HP Labs: singular! 3 For 2:) y<'ars, HP Lahoratories ha.... (pd HP's long-rangt' rest'arch. page 10 Driving up quality at Ford 10 Ford amI liP team to develop an ele<.'troni<- toolhox for automohiles. Your turn 14 History in a box 15 HP's profl'ssional ar('hives is a trt'aSUfC'-trov(' of information. Open for business: Silicon Valley's new garage 19 A million people a year art' expected to visit a new high-tl'eh {·xhihil. People 22 ,Jim Hanl('Y's inten'sts range from high tN'h to primitiw art. No room for dinosaurs 25 1900 was a da....sie exampll' ofttw constant Ill'ell to adapt to change. Letter from John Young 27 John ('xplains hew,; HP's new organizational structure is taking shape. ExtraMeasure 29 MEASURE Editor AssocIate edrtor Aft D,rector GraphiC des,gner Crrculat.on JoyCoIemon Belly Gerard Annerte Yc10VllZ Thomas J Brown Kathleen Miller Measure IS published SI' t'mes a year lor emplayees ana assoclctes 01 HewleN·Packard Compo<1y Produced by Corporate PublIC RelaIJon\ Employee CommunlcaIJon\ Department Brad Whll'worttl manager Addless correspondence 10 Measure....ew'e"·Pac~ard Companv. WBR PO Box 10301 Palo Alto. Calitornla 9<1303-0890 UY>. (.l15) 857-4146 Report changes ol address 10 yOU' local perSOnnel deportment c Copynghl 1991 by HewlelT Pac~ard Company MoIenal may be reprinted wllh permiSSIon Member. Inlerna1ranal Association of BUSiness Communicators Hewlert·Packard Company IS an International monufacturer 01 measurement ana computaTion products and sy.;lems recognized lOt excellence In quality and support The compony's products and services ore used ,n Industry. -

Mos Technology, 1963-1974: a Dozen Crucial Years

One of IBM’s most important MOS Technology, 1963-1974: A Dozen Crucial Years contributions to MOS research came from the Components Division, which was responsible for developing by Ross Knox Bassett and manufacturing bipolar transistors for its large computer systems and had very little interest in MOS transistors line can be drawn from the as such. As part of its work on Frosch’s and Derick’s work on bipolar transistors, Donald Kerr and silicon dioxide to the MOS (metal- a group of engineers had discovered A that depositing small amounts of oxide-semiconductor) transistor’s domi- nance of semiconductor technology, phosphorous on the silicon-dioxide but it is neither short nor straight. That surface and forming a layer of line has several discernable segments, phosphosilicate glass (PSG) could first from Frosch and Derick’s work, limit the amount of leakage in bipolar until 1963. In this interval, by and transistors and play an important role large, no one thought seriously about a in enhancing the stability of MOS metal-oxide-semiconductor as a viable transistors. Jerome Eldridge and Pieter technology in its own right. The second Balk from IBM Research implemented segment runs from 1963, when the this work by using thin layers of combination of integrated circuits and PSG to make stable MOS devices. the planar manufacturing process had Other important work on the physics FIG. 2. Drawing of Atalla and Kahng’s “silicon-silicon dioxide surface device,” now known as and chemistry of MOS devices done led people to see MOS transistors as a the MOS transistor, from a 1961 Bell Labs technical memorandum by Kahng. -

Agood Forty Years

Agood forty years... No trumpets blew when Dave Packard and Bill Hewlett walked up to receive their 40th year service awards from John Young on December 18. A few reminis cences and they turned to the business at hand: passing out 25·, 30- and 35-year I awards to other HP veterans gathered for the annual Bay Area awards luncheon. Of course, technically speaking, these weren't even the first 40-year awards handed out at Hewlett-Packard- that honor had already gone to a handful of Waltham Division employees who were credited with years spent working for a venerable acquisition, the Sanborn Company. And yet, those 40-year awards to Dave and Bill last month were clearly something quite special in the history of the company they founded four decades ago. For a few minutes the co-founders thought back to those early days in Palo Alto when they were beginning to build devices in a garage workshop during Dave Packard and Bill Hewlett mark 40 years 01 Hewlett-Packard service with a handshake. The ollicial starting date 01 the company's co-launders was January 1,1939. spare hours sandwiched between graduate study and work at Stanford University. The idea of having their own com pany had occurred to the young men five years earlier when they were engineering undergraduates together at Stanford. By the end of 1938 they were halfway to that goal-Dave Packard and his wife Lucile living in an apartment in downtown Palo Cover: After receiving their 40-year Alto, Bill Hewlett batching in a cottage service awards last month, HP founders Dave Packard (left) and Bill Hewlett (right) looked over some photographs of the company's earlier days. -

2015 IEDM Conference Proceedings

2015 IEDM Conference Proceedings For More Information Social Networks: IEDM Online: ieee-iedm.org ieee-iedm.org/social-media Table of Contents Intro .....................................................3 Committees ...........................................3 Topics of Interest ....................................7 Program: Tutorials ................................................8 Short Courses ........................................8 Plenary Session ......................................9 Focus Session ........................................9 Technical Program ................................10 IEDM Luncheon ....................................11 Panel Discussion ..................................11 Entrepreneur’s Luncheon ........................11 Abstracts, Bios for Tutorials, Short Courses & Technical Program ......................Appendix 2020 IEEE International Electron Devices Meeting 2 Intro IEEE International Electron Devices Meeting (IEDM) is the world’s preeminent forum for reporting technological breakthroughs in the areas of semiconductor and electronic device technology, design, manufacturing, physics, and modeling. IEDM is the fl agship conference for nanometer-scale CMOS transistor technology, advanced memory, displays, sensors, MEMS devices, novel quantum and nano-scale devices and phenomenology, optoelectronics, devices for power and energy harvesting, high-speed devices, as well as process technology and device modeling and simulation. Digital & Social Media •LinkedIn: https://www.linkedin.com/groups/7475096/ •Twitter: -

Agilent Technologies' Spin Make It Acceptable for Printing'?" with Any Employees

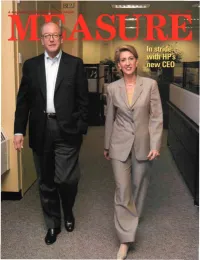

FROM THE EDITOR can't say exactly when I became meeting to talk ""ith customers or a big fan of CEO Lew Platt, but visitors-and ended up staying I think it was one day in Febru longer than either of you imagined ary 1993. he would. He cares deeply about. I had written a MEASURE article the personal tonch. about HP's order-fulfillment problems. For the past few years, Lew has A couple of senior executives felt the gotten into the habit of eating lunch (one was too honest. Lew was asked with several of us from HP Communi to arbitrate the dispute. In many cations. I think he enjoyed the fact companies, that would have been that we rarely talk about work. an easy decision: senior executives 1, Name a topic-sports, current events, employee publication O. fine wine, photography, literature, Lew walked over to my office and wombats-and Lew invmiably explained-almost apologetically knows more about it than anyone On the cover: Carly Fiorina, that the article had some problems at the table. HP's new president and and needed to be pulled from the Here's a guy who regularly coun CEO, sets a fast and ener· getic pace for the company magazine, which was due to go to the sels and dines with CEOs, world lead to follow. Retiring President printer within a few days. I countered, ers and royalty; yet, he seems equally and CEO Lew Platt is non "You mean there's no middle ground? happy eating chicken strips and fries executive chairman of the HP Board while overseeing There's no way to edit the story to in the company cafeteria and t.alking Agilent Technologies' spin make it acceptable for printing'?" with any employees. -

Memristor Devices: Fabrication, Characterization, Simulation

MEMRISTOR DEVICES: FABRICATION, CHARACTERIZATION, SIMULATION, AND CIRCUIT DESIGN Thesis Submitted to The School of Engineering of the UNIVERSITY OF DAYTON In Partial Fulfillment of the Requirements for The Degree of Master of Science in Electrical Engineering By Chris Yakopcic Dayton, Ohio August, 2011 MEMRISTOR DEVICES: FABRICATION, CHARACTERIZATION, SIMULATION, AND CIRCUIT DESIGN Name: Yakopcic, Chris APPROVED BY: _________________________________ _________________________________ Tarek M. Taha, Ph.D. Guru Subramanyam, Ph.D. Advisory Committee Chairman Committee Member Associate Professor Chair and Professor Electrical and Computer Engineering Electrical and Computer Engineering _________________________________ Andrew Sarangan, Ph.D. Committee Member Associate Professor Electro-Optics _________________________________ _________________________________ John G. Weber, Ph.D. Tony E. Saliba, Ph.D. Associate Dean Dean, School of Engineering School of Engineering & Wilke Distinguished Professor ii ©Copyright by Chris Yakopcic All Rights Reserved 2011 iii ABSTRACT MEMRISTOR DEVICES: FABRICATION, CHARACTERIZATION, SIMULATION, AND CIRCUIT DESIGN Name: Yakopcic, Chris University of Dayton Advisor: Dr. Tarek M. Taha Significant interest has been placed on developing systems based on memristors since the initial fabrication by HP Labs in 2008 [1]. The memristor is a nanoscale device with dynamic resistance that is able to retain the last programmed resistance value after power is removed from the device. This property shows that the memristor can be used as a non-volatile memory component, and has potential to enhance many types of systems, such as high density memory, and neuromorphic computing architectures. This thesis presents the fabrication and characterization results obtained based memristor devices developed at the University of Dayton. In addition, a comparison between the existing memristor device models was completed to show how the memristor can be used in a multistate operation.