Semiconductor Technology Dry Etching

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

On-Wafer Fabrication of Cavity Mirrors for Ingan-Based Laser Diode Grown

www.nature.com/scientificreports OPEN On-wafer fabrication of cavity mirrors for InGaN-based laser diode grown on Si Received: 25 January 2018 Junlei He1,2, Meixin Feng1,3, Yaozong Zhong1, Jin Wang1,4, Rui Zhou1,2, Hongwei Gao1,3, Yu Accepted: 17 April 2018 Zhou1,3, Qian Sun1,2,3, Jianxun Liu1, Yingnan Huang1, Shuming Zhang1,2, Huaibing Wang1, Published: xx xx xxxx Masao Ikeda1 & Hui Yang1,2 Direct bandgap III-V semiconductor lasers grown on silicon (Si) are highly desired for monolithic integration with Si photonics. Fabrication of semiconductor lasers with a Fabry–Pérot cavity usually includes facet cleavage, however, that is not compatible with on-chip photonic integration. Etching as an alternative approach holds a great advantage in preparing cavity mirrors with no need of breaking wafer into bars. However, gallium nitride (GaN) sidewalls prepared by dry etching often have a large roughness and etching damages, which would cause mirror loss due to optical scattering and carrier injection loss because of surface non-radiative recombination. A wet chemical polishing process of GaN sidewall facets formed by dry etching was studied in detail to remove the etching damages and smooth the vertical sidewalls. The wet chemical polishing technique combined with dry etching was successfully applied to the on-wafer fabrication of cavity mirrors, which enabled the realization of room temperature electrically injected InGaN-based laser diodes grown on Si. Silicon photonics call for electrically injected semiconductor laser diodes (LDs) as on-chip light sources1–3. When grown on Si, III-nitride (Al, Ga, In)N semiconductors with a direct-band emission wavelength ranging from 0.2 to 1.8 μm ofer a new approach for achieving on-chip lasers4–7. -

A Review of Different Etching Methodologies and Impact of Various Etchants in Wet Etching in Micro Fabrication

ISSN (Online) : 2319 – 8753 ISSN (Print) : 2347 - 6710 International Journal of Innovative Research in Science, Engineering and Technology An ISO 3297: 2007 Certified Organization, Volume 3, Special Issue 1, February 2014 International Conference on Engineering Technology and Science-(ICETS’14) On 10th & 11th February Organized by Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India A Review of Different Etching Methodologies and Impact of various etchants in Wet Etching in Micro Fabrication Benjamin. J1, Grace Jency. J2, Vijila. G3 Department of ECE, Karunya University, Karunya Nagar, Coimbatore – 641114, India1, 2, 3 Abstract-- The concept of miniaturization was each and every wafer undergo a lot of etching process. introduced because of advancement in science and The material which is used to protect the wafer from the technology during 1980s. These miniaturized etchants is known as the masking material, which is used structures and designs are of high significance for in many etching steps to resist etching. This masking making up with the macroscopic technology, for the material can be a photoresist and it is patterned using sake of interfacing with microscopic world. The photolithography.Etching can also be referred as making fabrication of micro structures and designs which are cavities and these cavities should have specific depth the advanced applications of micro fabrication are according to the purposes. The depth of such cavities used for the process of micromachining structures in produced can be controlled by etching time and the three dimensions as it is essential for interfacing with etching rate. -

Etch Overview for Microsystems Primary Knowledge Participant Guide

Etch Overview for Microsystems Primary Knowledge Participant Guide Description and Estimated Time to Complete This Learning Module introduces the most common etch processes used in the fabrication of microsystems. Activities allow you to demonstrate your understanding of the terminology and basic concepts of these processes. This unit provides an overview of the etch processes as they apply to the fabrication of Microsystems or Microelectromechanical Systems (MEMS). It is designed to provide basic information on the etch processes and how they are used in the fabrication of MEMS. This unit will introduce you to etch terminology, purpose and processes. Additional instructional units provide more in-depth discussion of the topics introduced in this overview. Estimated Time to Complete Allow at least 30 minutes to review. Southwest Center for Microsystems Education (SCME) Page 1 of 21 Fab_Etch_PK00_PG_April2017.docx Etch Overview PK Introduction Pattern Transfer For microsystems fabrication etch is a process that removes select materials from • the wafer's surface, • below the wafer's surface, or • from within the substrate. The etch process normally follows photolithography or deposition during which a protective masking layer is applied to the wafer's surface. The protective masking layer is used to identify the material to be etched and to protect material that is to remain. The figure labeled “Pattern Transfer,” illustrates a mask pattern transferred into a photosensitive layer, shown in red (masking layer), on the wafer's surface (Photolithography Process). During the Etch Process (right), that pattern is transferred into the surface layer, removing exposed areas of the surface layer and leaving areas in the underlying layer open to a subsequent process step. -

High Resolution Inductively Coupled Plasma Etching of 30 Nm Lines and Spaces in Tungsten and Silicon Andrew L

High resolution inductively coupled plasma etching of 30 nm lines and spaces in tungsten and silicon Andrew L. Goodyeara) and Sinclair Mackenzie Oxford Instruments Plasma Technology, North End, Yatton, Bristol, United Kingdom Deirdre L. Olynick and Erik H. Anderson Lawrence Berkeley National Laboratory, Berkeley, California ͑Received 1 June 2000; accepted 23 August 2000͒ Dry etching of 30 nm features was investigated for x-ray and integrated electronics applications. These typically require etching of either a tungsten absorber layer or a silicon mold. Through the use of an inductively coupled plasma source and accurate control over substrate temperature it was possible to achieve highly anisotropic patterning of tungsten and silicon. Densely patterned features as small as 30 nm and at pitches of 70 nm were etched in tungsten and silicon, to depths of 100 and 200 nm, respectively. © 2000 American Vacuum Society. ͓S0734-211X͑00͒18406-9͔ I. INTRODUCTION takes this process further by producing the densely packed fine features with better sidewalls and higher aspect ratios. Patterning of sub-100 nm features has become essential This is critical for the production of the highest resolution for advanced research and development in electronics, op- x-ray optics. tics, and material science applications. This is especially true The etching of these fine features requires advanced and for x-ray applications such as microscopy zone plate lenses. sophisticated processes and equipment. The high ion density, The critical steps in the production of densely packed sub- low pressure ICP etch regime is one of the few ways to 100 nm features for x-ray applications are high resolution provide highly anisotropic profiles with excellent control e-beam lithography and precisely controlled dry etching of over selectivity to mask materials. -

2015 IEDM Conference Proceedings

2015 IEDM Conference Proceedings For More Information Social Networks: IEDM Online: ieee-iedm.org ieee-iedm.org/social-media Table of Contents Intro .....................................................3 Committees ...........................................3 Topics of Interest ....................................7 Program: Tutorials ................................................8 Short Courses ........................................8 Plenary Session ......................................9 Focus Session ........................................9 Technical Program ................................10 IEDM Luncheon ....................................11 Panel Discussion ..................................11 Entrepreneur’s Luncheon ........................11 Abstracts, Bios for Tutorials, Short Courses & Technical Program ......................Appendix 2020 IEEE International Electron Devices Meeting 2 Intro IEEE International Electron Devices Meeting (IEDM) is the world’s preeminent forum for reporting technological breakthroughs in the areas of semiconductor and electronic device technology, design, manufacturing, physics, and modeling. IEDM is the fl agship conference for nanometer-scale CMOS transistor technology, advanced memory, displays, sensors, MEMS devices, novel quantum and nano-scale devices and phenomenology, optoelectronics, devices for power and energy harvesting, high-speed devices, as well as process technology and device modeling and simulation. Digital & Social Media •LinkedIn: https://www.linkedin.com/groups/7475096/ •Twitter: -

The Study of Reactive Ion Etching of Heavily Doped Polysilicon Based on Hbr/O2/He Plasmas for Thermopile Devices

materials Article The Study of Reactive Ion Etching of Heavily Doped Polysilicon Based on HBr/O2/He Plasmas for Thermopile Devices Na Zhou 1,*, Junjie Li 1 , Haiyang Mao 1,2,*, Hao Liu 3, Jinbiao Liu 1, Jianfeng Gao 1, Jinjuan Xiang 1, Yanpeng Hu 1, Meng Shi 1, Jiaxin Ju 4, Yuxiao Lei 4, Tao Yang 1, Junfeng Li 1 and Wenwu Wang 1 1 Key Laboratory of Microelectronics Devices & Integrated Technology, Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China; [email protected] (J.L.); [email protected] (J.L.); [email protected] (J.G.); [email protected] (J.X.); [email protected] (Y.H.); [email protected] (M.S.); [email protected] (T.Y.); [email protected] (J.L.); [email protected] (W.W.) 2 Advanced Sensing Department, Wuxi Internet of Things Innovation Center Co. Ltd., Wuxi 214001, China 3 School of Science, China University of Geosciences, Beijing 10083, China; [email protected] 4 College of Electronic and Information Engineering, North China University of Technology, Beijing 100144, China; [email protected] (J.J.); [email protected] (Y.L.) * Correspondence: [email protected] (N.Z.); [email protected] (H.M.); Tel.: +86-010-8299-5794 (N.Z.) Received: 7 August 2020; Accepted: 21 September 2020; Published: 25 September 2020 Abstract: Heavily doped polysilicon layers have been widely used in the fabrication of microelectromechanical systems (MEMS). However, the investigation of high selectivity, anisotropy, and excellent uniformity of heavily doped polysilicon etching is limited. -

Optimization of Mesa Etch for a Quasi-Vertical Gan Schottky Barrier Diode (SBD) by Inductively Coupled Plasma (ICP) and Device Characteristics

nanomaterials Article Optimization of Mesa Etch for a Quasi-Vertical GaN Schottky Barrier Diode (SBD) by Inductively Coupled Plasma (ICP) and Device Characteristics Yue Sun 1,2,3, Xuanwu Kang 2,* , Yingkui Zheng 2, Ke Wei 2, Pengfei Li 2, Wenbo Wang 1, Xinyu Liu 2 and Guoqi Zhang 3,* 1 Shenzhen Institute of Wide-Bandgap Semiconductors, Shenzhen 518000, China; [email protected] (Y.S.); [email protected] (W.W.) 2 Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China; [email protected] (Y.Z.); [email protected] (K.W.); [email protected] (P.L.); [email protected] (X.L.) 3 Department of Microelectronics, Delft University of Technology, 2628 CD Delft, The Netherlands * Correspondence: [email protected] (X.K.); [email protected] (G.Z.); Tel.: +86-186-0009-6727 (X.K.) Received: 24 February 2020; Accepted: 29 March 2020; Published: 1 April 2020 Abstract: The optimization of mesa etch for a quasi-vertical gallium nitride (GaN) Schottky barrier diode (SBD) by inductively coupled plasma (ICP) etching was comprehensively investigated in this work, including selection of the etching mask, ICP power, radio frequency (RF) power, ratio of mixed gas, flow rate, and chamber pressure, etc. In particular, the microtrench at the bottom corner of the mesa sidewall was eliminated by a combination of ICP dry etching and tetramethylammonium hydroxide (TMAH) wet treatment. Finally, a highly anisotropic profile of the mesa sidewall was realized by using the optimized etch recipe, and a quasi-vertical GaN SBD was demonstrated, achieving a low reverse current density of 10 8 A/cm2 at 10 V. -

Lecture 26: Etching and Deposition

Lecture 26: Etching and deposition Contents 1 Etching 1 1.1 Wet etching . .2 1.2 Etching challenges . .3 1.2.1 Incomplete etch . .3 1.2.2 Over etch and undercutting . .5 1.2.3 Etch selectivity . .5 2 Dry etching 6 2.1 Plasma etch . .8 2.2 Ion beam etch . 10 2.3 Reactive ion etching . 10 3 Deposition 12 3.1 Chemical vapor deposition (CVD) . 13 3.2 Molecular beam epitaxy (MBE) . 15 3.3 Deposited Si . 16 1 Etching Etching refers to the removal of material from the wafer surface. The process is usually combined with lithography in order to select specific areas on the wafer from which material is to be removed. Etching represents one way of permanently transferring the mask pattern from the photoresist to the wafer surface. The complementary process to etching is deposition (or growth), where new material is added. Unlike oxidation (or nitridation), where the underlying Si is consumed to form the oxide (nitride) layer, in deposition, new material is added without consuming the underlying wafer. There are two main types of etching 1. Wet etching 1 MM5017: Electronic materials, devices, and fabrication Figure 1: Schematic of the wet etching process. A controlled portion of the wafer surface is exposed to the etchant which then removes materials by chemical reaction. Adapted from Fundamentals of semiconductor manufac- turing and process control - May and Spanos. 2. Dry etching 1.1 Wet etching In wet etching, the wafers are immersed in a tank of the etchant (mix of chemicals), as shown in figure 1. -

Clean-Room Lithographical Processes for the Fabrication of Graphene Biosensors

materials Article Clean-Room Lithographical Processes for the Fabrication of Graphene Biosensors Patrícia D. Cabral 1,2 , Telma Domingues 1, George Machado, Jr. 1, Alexandre Chicharo 1 , Fátima Cerqueira 1,2, Elisabete Fernandes 1, Emília Athayde 3 , Pedro Alpuim 1,2,* and Jérôme Borme 1 1 International Iberian Nanotechnology Laboratory, 4715-330 Braga, Portugal; [email protected] (P.D.C.); [email protected] (T.D.); [email protected] (G.M.J.); [email protected] (A.C.); [email protected] (F.C.); [email protected] (E.F.); [email protected] (J.B.) 2 Center of Physics, University of Minho, 4710-057 Braga, Portugal 3 Center of Mathematics, University of Minho, 4710-057 Braga, Portugal; [email protected] * Correspondence: [email protected] Received: 30 September 2020; Accepted: 13 December 2020; Published: 15 December 2020 Abstract: This work is on developing clean-room processes for the fabrication of electrolyte-gate graphene field-effect transistors at the wafer scale for biosensing applications. Our fabrication process overcomes two main issues: removing surface residues after graphene patterning and the dielectric passivation of metallic contacts. A graphene residue-free transfer process is achieved by using a pre-transfer, sacrificial metallic mask that protects the entire wafer except the areas around the channel, source, and drain, onto which the graphene film is transferred and later patterned. After the dissolution of the mask, clean gate electrodes are obtained. The multilayer SiO2/SiNx dielectric passivation takes advantage of the excellent adhesion of SiO2 to graphene and the substrate materials and the superior impermeability of SiNx. -

III. Wet and Dry Etching

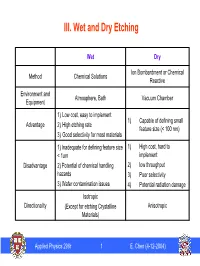

III. Wet and Dry Etching Wet Dry Ion Bombardment or Chemical Method Chemical Solutions Reactive Environment and Atmosphere, Bath Vacuum Chamber Equipment 1) Low cost, easy to implement 1) Capable of defining small Advantage 2) High etching rate feature size (< 100 nm) 3) Good selectivity for most materials 1) Inadequate for defining feature size 1) High cost, hard to < 1um implement Disadvantage 2) Potential of chemical handling 2) low throughput hazards 3) Poor selectivity 3) Wafer contamination issues 4) Potential radiation damage Isotropic Directionality (Except for etching Crystalline Anisotropic Materials) Applied Physics 298r 1 E. Chen (4-12-2004) Pattern Generation (Transfer): Etch vs. Liftoff Etching Liftoff Mask Mask Mask Film Film Lithography Lithography Substrate Substrate Film Film Mask Film Deposit Mask Film Mask Etching Film Substrate Substrate Film Film Strip Remove Mask (Resist) Substrate Mask (Resist) Substrate (Liftoff) Applied Physics 298r 2 E. Chen (4-12-2004) Isotropic vs. Anisotropic Etching Mask Isotropic Etching: Etching rate is the same in both horizontal and vertical direction Anisotropic Etching: Etching rate is different in horizontal and vertical direction RL = 1 Lateral Etch Ratio: Mask Horizontal Etch Rate (rH ) RL = Vertical Etch Rate ()rV 0 < R < 1 Isotropic Etching: RL = 1 L Anisotropic Etching: 0 < RL < 1 Mask Directional Etching: RL = 0 Bias: the difference in lateral dimensions between the feature on mask and the actually etched pattern RL = 0 ¨ smaller RL results in smaller bias Applied Physics 298r 3 E. Chen (4-12-2004) “Under Cut” and “Over Etch” Bias Bias Mask Mask Film Film “Under Cut” Substrate Good for Lift-off Substrate (Rl = 1, pattern dimension (Rl = 0.5, pattern dimension is poorly defined) is better defined) Mask Mask Substrate Substrate Over-Etch ¬ results in more vertical profile Worse in thick film but larger bias ¬ Poor CD control in thick film using wet etch Applied Physics 298r 4 E. -

Silicon Fabrication Process Pdf

Silicon fabrication process pdf Continue The manufacturing process used to create integrated circuits This article needs additional quotes to verify. Please help improve this article by adding quotes to reliable sources. Non-sources of materials can be challenged and removed. Find sources: Semiconductor Manufacturing - JSTOR Newspaper News Books (September 2008) (Узнайте, как и когда удалить это сообщение шаблона) Масштабирование (узлы процесса) 010 мкм - 1971 006 мкм - 1974 003 мкм - 1977 1,5 мкм - 1981 0 1984 800 нм - 1987 600 нм - 1990 350 нм - 1993 250 нм - 1996 180 нм - 1999 130 нм - 2001 090 нм - 2003 0 65 нм - 2005 045 нм - 2007 032 нм - 2009 022 нм - 2012 014 нм - 2014 010 нм - 2016 007 нм - 2018 005 нм - 2020 Будущее 003 нм - 2022 002 нм - No 2023< Половина узлов Плотность CMOS Устройство (много ворот) Мур закон полупроводниковой промышленности Nanoelectronics vte НАСА Гленн исследовательский центр чистой комнате Внешнее изображение Фото интерьера чистой комнате 300mm fab в ведении TSMC полупроводникового устройства изготовления является процесс, используемый для производства полупроводниковых устройств , как правило , metal-oxide-semiconductor (MOS) devices used in integrated circuits (IC) chips that are present in everyday electrical and electronic devices. This is a multi-step sequence of stages of photolithographic and chemical processing (such as surface passivation, thermal oxidation, planar diffusion and compound insulation), during which electronic circuits are gradually created on a plate of pure semiconductor materials. Silicon is almost always used, but different semiconductor compounds are used for specialized applications. The entire manufacturing process, from the beginning to the packaged chips ready for shipment, takes six to eight weeks and is performed in highly specialized semiconductor plants, also called foundries or fabs. -

Micro-Fabrication and High-Productivity Etching System for 65-Nm Node and Beyond

Hitachi Review Vol. 55 (2006), No. 2 83 Micro-fabrication and High-productivity Etching System for 65-nm Node and Beyond Takashi Tsutsumi OVERVIEW: In regard to cutting-edge semiconductor devices, mass Masanori Kadotani production of 65-nm node devices is about to begin, and development aiming beyond the 45-nm node has already started. Along with this trend, demands Go Saito for advanced miniaturization and precision-improvement techniques are Masahito Mori growing, and the needs for handling new materials and establishing production stability are getting stronger. With these circumstances in mind and taking miniaturization, high precision, and high throughput as a base concept, Hitachi High-Technologies Corporation has developed etching systems and processes for handling the post-65-nm node. Aimed at improving the uniformity across a wafer surface during etching of 300-mm-diameter wafers, an etching reactor—with uniformized discharge-gas rate and a mechanism for controlling electrode-temperature difference—was developed. A “resist trimming” technique, which can handle dimensions that surpass the exposure limit of current lithography, was also developed. Moreover, the etching reactor was designed and developed to realize low CoO, namely, improved operability and shorter maintenance downtime, and is targeting silicon-etching systems for handling the post-45-nm node. INTRODUCTION ITRS (International Technology Roadmap for IN regard to semiconductor-device manufacturers, Semiconductors),(1) the physical gate length in an MPU development aimed at mass production of 65-nm node (micro-processor unit) is forecast to reach 25 nm for devices is progressing. Accordingly, in 2006, the 65-nm node and 18 nm for the 45-nm node.