AN741: Using the Sim3l1xx Advanced Capture Counter in LC

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

C I L Q LC Circuit

Your Comments I am not feeling great about this midterm...some of this stuff is really confusing still and I don't know if I can shove everything into my brain in time, especially after spring break. Can you go over which topics will be on the exam Wednesday? This was a very confusing prelecture. Do you think you could go over thoroughly how the LC circuits work qualitatively? I may have missed something simple, but in question 1 during the prelecture why does the charge on the capacitor have to be 0 at t=0? I feel like that bit of knowledge will help me with the test wednesday I remember you mentioning several weeks ago that there was one equation you were going to add to the 2013 equation sheet... which formula was that? Thanks! Electricity & Magnetism Lecture 19, Slide 1 Some Exam Stuff Exam Wed. night (March 27th) at 7:00 Covers material in Lectures 9 – 18 Bring your ID: Rooms determined by discussion section (see link) Conflict exam at 5:15 Don’t forget: • Worked examples in homeworks (the optional questions) • Other old exams For most people, taking old exams is most beneficial Final Exam dates are now posted The Big Ideas L9-18 Kirchoff’s Rules Sum of voltages around a loop is zero Sum of currents into a node is zero Kirchoff’s rules with capacitors and inductors • In RC and RL circuits: charge and current involve exponential functions with time constant: “charging and discharging” Q dQ Q • E.g. IR R V C dt C Capacitors and inductors store energy Magnetic fields Generated by electric currents (no magnetic charges) Magnetic -

Analysis of Magnetic Resonance in Metamaterial Structure

Analysis of magnetic resonance in Metamaterial structure Rajni#1, Anupma Marwaha#2 #1 Asstt. Prof. Shaheed Bhagat Singh College of Engg. And Technology,Ferozepur(Pb.)(India), #2 Assoc. Prof., Sant Longowal Institute of Engg. And Technology,Sangrur(Pb.)(India) [email protected] 2 [email protected] Abstract: ‘Metamaterials’ is one of the most 1. Introduction recent topics in several areas of science and technology due to its vast potential in various Metamaterials are artificial materials synthesized applications. These are artificially fabricated by embedding specific inclusions like periodic materials which exhibit negative permittivity structures in host media. These materials have and/or negative permeability. The unusual the unique property of negative permittivity electromagnetic properties of metamaterial and/or negative permeability not encountered in have opened more opportunities for better the nature. If materials have both parameters antenna design to surmount the limitations of negative at the same time, then they exhibit an conventional antennas. Metamaterials have effective negative index of refraction and are created many designs in a broad frequency referred to as Left-Handed Metamaterials spectrum from microwave to millimeter wave (LHM). This name is given to these materials to optical structures. The edifice building because the electric field, magnetic field and the blocks of metamaterials are synthetically wave vector form a left-handed system. These fabricated periodic structures of having materials offer a new dimension to the antenna lattice constants smaller than the wavelength applications. The phase velocity and group of the incident radiation. Thus metamaterial velocity in these materials are anti-parallel to properties can be controlled by the design of each other i.e. -

6.453 Quantum Optical Communication Reading 4

Massachusetts Institute of Technology Department of Electrical Engineering and Computer Science 6.453 Quantum Optical Communication Lecture Number 4 Fall 2016 Jeffrey H. Shapiro c 2006, 2008, 2014, 2016 Date: Tuesday, September 20, 2016 Reading: For the quantum harmonic oscillator and its energy eigenkets: C.C. Gerry and P.L. Knight, Introductory Quantum Optics (Cambridge Uni- • versity Press, Cambridge, 2005) pp. 10{15. W.H. Louisell, Quantum Statistical Properties of Radiation (McGraw-Hill, New • York, 1973) sections 2.1{2.5. R. Loudon, The Quantum Theory of Light (Oxford University Press, Oxford, • 1973) pp. 128{133. Introduction In Lecture 3 we completed the foundations of Dirac-notation quantum mechanics. Today we'll begin our study of the quantum harmonic oscillator, which is the quantum system that will pervade the rest of our semester's work. We'll start with a classical physics treatment and|because 6.453 is an Electrical Engineering and Computer Science subject|we'll develop our results from an LC circuit example. Classical LC Circuit Consider the undriven LC circuit shown in Fig. 1. As in Lecture 2, we shall take the state variables for this system to be the charge on its capacitor, q(t) Cv(t), and the flux through its inductor, p(t) Li(t). Furthermore, we'll consider≡ the behavior of this system for t 0 when one≡ or both of the initial state variables are non-zero, i.e., q(0) = 0 and/or≥p(0) = 0. You should already know that this circuit will then undergo simple6 harmonic motion,6 i.e., the energy stored in the circuit will slosh back and forth between being electrical (stored in the capacitor) and magnetic (stored in the inductor) as the voltage and current oscillate sinusoidally at the resonant frequency ! = 1=pLC. -

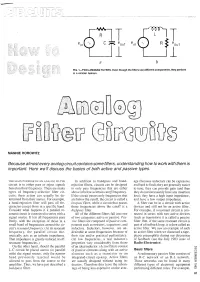

How to Design Analog Filter Circuits.Pdf

a b FIG. 1-TWO LOWPASS FILTERS. Even though the filters use different components, they perform in a similiar fashion. MANNlE HOROWITZ Because almost every analog circuit contains some filters, understandinghow to work with them is important. Here we'll discuss the basics of both active and passive types. THE MAIN PURPOSE OF AN ANALOG FILTER In addition to bandpass and band- age (because inductors can be expensive circuit is to either pass or reject signals rejection filters, circuits can be designed and hard to find); they are generally easier based on their frequency. There are many to only pass frequencies that are either to tune; they can provide gain (and thus types of frequency-selective filter cir- above or below a certain cutoff frequency. they do not necessarily have any insertion cuits; their action can usually be de- If the circuit passes only frequencies that loss); they have a high input impedance, termined from their names. For example, are below the cutoff, the circuit is called a and have a low output impedance. a band-rejection filter will pass all fre- lo~~passfilter, while a circuit that passes A filter can be in a circuit with active quencies except those in a specific band. those frequencies above the cutoff is a devices and still not be an active filter. Consider what happens if a parallel re- higlzpass filter. For example, if a resonant circuit is con- sonant circuit is connected in series with a All of the different filters fall into one . nected in series with two active devices signal source. -

Quasi-Static and Propagating Modes in Three-Dimensional Thz Circuits

Quasi-static and propagating modes in three-dimensional THz circuits Mathieu Jeannin,1 Djamal Gacemi,1 Angela Vasanelli,1 Lianhe Li,2 Alexander Giles Davies,2 Edmund Linfield,2 Giorgio Biasiol,3 Carlo Sirtori1 and Yanko Todorov1,* 1Laboratoire de Physique de l’École Normale Supérieure, ENS, Université PSL, CNRS, Sorbonne Université, université de Paris, F-75005 Paris, France 2School of Electronic and Electrical Engineering, University of Leeds, LS2 9JT Leeds, United Kingdom 3Laboratori TASC, CNR-IOM at Area Science Park, Strada Statale 14, km163.5, Basovizza, TS34149, Italy *[email protected] Abstract: We provide an analysis of the electromagnetic modes of three-dimensional metamaterial resonators in the THz frequency range. The fundamental resonance of the structures is fully described by an analytical circuit model, which not only reproduces the resonant frequencies but also the coupling of the metamaterial with an incident THz radiation. We also evidence the contribution of the propagation effects, and show how they can be reduced by design. In the optimized design the electric field energy is lumped into ultra-subwavelength (λ/100) capacitors, where we insert semiconductor absorber based onλ/100) capacitors,whereweinsertsemiconductorabsorberbasedon the collective electronic excitation in a two dimensional electron gas. The optimized electric field confinement is evidenced by the observation of the ultra-strong light-matter coupling regime, and opens many possible applications for these structures for detectors, modulators and sources of THz radiation. 1. Introduction The majority of metamaterials has a two-dimensional geometry and benefit from well-established planar top-down fabrication techniques. When used as passive optical components, this two-dimensional character results in flat optical elements, such as lenses or phase control/phase shaping devices [1]–[4]. -

Notes on LRC Circuits and Maxwell's Equations Last Quarter, in Phy133

Notes on LRC circuits and Maxwell's Equations Last quarter, in Phy133, we covered electricity and magnetism. There was not enough time to finish these topics, and this quarter we start where we left off and complete the classical treatment of the electro-magnetic interaction. We begin with a discussion of circuits which contain a capacitor, resistor, and a significant amount of self-induction. Then we will revisit the equations for the electric and magnetic fields and add the final piece, due to Maxwell. As we will see, the missing term added by Maxwell will unify electromagnetism and light. Besides unifying different phenomena and our understanding of physics, Maxwell's term lead the way to the development of wireless communication, and revolutionized our world. LRC Circuits Last quarter we covered circuits that contained batteries and resistors. We also considered circuits with a capacitor plus resistor as well as resistive circuits that has a large amount of self-inductance. The self-inductance was dominated by a coiled element, i.e. an inductor. Now we will treat circuits that have all three properties, capacitance, resistance and self-inductance. We will use the same "physics" we discussed last quarter pertaining to circuits. There are only two basic principles needed to analyze circuits. 1. The sum of the currents going into a junction (of wires) equals the sum of the currents leaving that junction. Another way is to say that the charge flowing into equals the charge flowing out of any junction. This is essentially a state- ment that charge is conserved. 1) The sum of the currents into a junction equals the sum of the currents flowing out of the junction. -

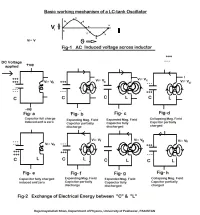

LC Oscillator Basics

4/10/2020 LC Oscillator Tutorial and Tuned LC Oscillator Basics Home / Oscillator / LC Oscillator Basics LC Oscillator Basics Oscillators are electronic circuits that generate a continuous periodic waveform at a precise frequency Oscillators convert a DC input (the supply voltage) into an AC output (the waveform), which can have a wide range of different wave shapes and frequencies that can be either complicated in nature or simple sine waves depending upon the application. Oscillators are also used in many pieces of test equipment producing either sinusoidal sine waves, square, sawtooth or triangular shaped waveforms or just a train of pulses of a variable or constant width. LC Oscillators are commonly used in radio-frequency circuits because of their good phase noise characteristics and their ease of implementation. An Oscillator is basically an Amplifier with “Positive Feedback”, or regenerative feedback (in- phase) and one of the many problems in electronic circuit design is stopping amplifiers from oscillating while trying to get oscillators to oscillate. Oscillators work because they overcome the losses of their feedback resonator circuit either in the form of a capacitor, inductor or both in the same circuit by applying DC energy at the required frequency into this resonator circuit. In other words, an oscillator is a an amplifier which uses positive feedback that generates an output frequency without the use of an input signal. Thus Oscillators are self sustaining circuits generating an periodic output waveform at a precise frequency -

VIII.A Acronyms and Definitions

Northwest Engineering and Vehicle Technology Exchange Vehicle Electrification System Standards VIII. DC – DC Converters Systems VIII.a Acronyms and Definitions Image Name Acronym Definition Alternating Current AC A type of electrical current in which, the direction of the flow of electrons switches back and forth at specified intervals or cycles. The cycles per second (Hz) can be variable or fixed. Amp (Current) Clamp Automotive DC-DC; A Direct-Current to Direct BEV/FCEV/HEV/PHEV APM Current (DC-DC) converter DC-DC Converter is an electronic circuit or electromechanical device that converts a source of NSF / ATE Grant Award # 1700708 Northwest Engineering and Vehicle Technology Exchange (NEVTEX) Advanced Vehicle Technician Standards Committee (AVTSC) Page | 1 Northwest Engineering and Vehicle Technology Exchange direct current (DC) from one voltage level to another (higher to lower or lower to higher voltage). It is a type of electric power converter. Power levels range from very low (small batteries) to very high (high-voltage power transmission). A DC-DC converter can also be known as an Accessory Power Supply (APM) Boost Converter (DC-DC Converter for Fuel Cell) NSF / ATE Grant Award # 1700708 Northwest Engineering and Vehicle Technology Exchange (NEVTEX) Advanced Vehicle Technician Standards Committee (AVTSC) Page | 2 Northwest Engineering and Vehicle Technology Exchange Boost Converter (DC-DC DC-DC; A DC-DC converter used Converter) APM in a Fuel Cell system is utilized to Boost the voltage from the Fuel Cell Stack before transferring it to the input of the electric propulsion system Buck Converter A buck converter is a DC- to-DC power converter which steps down voltage from its input to its output. -

Network Theory

NETWORK THEORY LECTURE NOTES B.TECH EEE (II YEAR – II SEM) Department of Electrical and Electronics Engineering MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) Recognized under 2(f) and 12 (B) of UGC ACT 1956 (Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – ‘A’ Grade - ISO 9001:2015 Certified) Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India B.Tech (EEE) R-17 MALLA REDDY COLLEGE OF ENGINEERING AND TECHNOLOGY II Year B.Tech EEE-II Sem L T/P/D C 4 -/-/- 4 (R17A0209) NETWORK THEORY Objectives: 1. This course introduces the analysis of transients in electrical systems, to understand three phase circuits, to evaluate network parameters of given electrical network, to draw the locus diagrams and to know about the network functions 2. To prepare the students to have a basic knowledge in the analysis of Electric Networks UNIT-I D.C Transient Analysis: Transient response of R-L, R-C, R-L-C circuits (Series and parallel combinations) for D.C. excitations, Initial conditions, Solution using differential equation and Laplace transform method. UNIT - II A.C Transient Analysis: Transient response of R-L, R-C, R-L-C circuits (Series and parallel combinations) for sinusoidal excitations, Initial conditions, Solution using differential equation and Laplace transform method. UNIT - III Three Phase Circuits: Phase sequence, Star and delta connection, Relation between line and phase voltages and currents in balanced systems, Analysis of balanced and Unbalanced three phase circuits UNIT – IV Locus Diagrams: Series and Parallel combination of R-L, R-C and R-L-C circuits with variation of various parameters. -

A Variation on the Damped LC Circuit: Back-To-Back Diodes

Nonlinear Damping of the LC Circuit using Anti-parallel Diodes Edward H. Hellena) and Matthew J. Lanctotb) Department of Physics and Astronomy, University of North Carolina at Greensboro, Greensboro, NC 27402 Abstract We investigate a simple variation of the series RLC circuit in which anti-parallel diodes replace the resistor. This results in a damped harmonic oscillator with a nonlinear damping term that is maximal at zero current and decreases with an inverse current relation for currents far from zero. A set of nonlinear differential equations for the oscillator circuit is derived and integrated numerically for comparison with circuit measurements. The agreement is very good for both the transient and steady-state responses. Unlike the standard RLC circuit, the behavior of this circuit is amplitude dependent. In particular for the transient response the oscillator makes a transition from under-damped to over-damped behavior, and for the driven oscillator the resonance response becomes sharper and stronger as drive source amplitude increases. The equipment is inexpensive and common to upper level physics labs. Keywords: nonlinear oscillator; LC circuit; nonlinear damping; diode I. Introduction The series RLC circuit is a standard example of a damped harmonic oscillator-one of the most important dynamical systems. In this paper we investigate a simple variation of the 2 RLC circuit in which the resistor is replaced by two anti-parallel diodes. This oscillator circuit is fundamental in the sense that it is constructed from a small number of the most basic passive electrical components: inductor, capacitor, and diodes. The result is that oscillator characteristics that have no amplitude dependence for the standard RLC circuit have strong amplitude dependence for the oscillator presented here. -

Class-D LC Filter Design (Rev. B)

Application Report SLOA119B–April 2006–Revised February 2015 Class-D LC Filter Design Yang Boon Quek ABSTRACT An LC filter is critical in helping you reduce electromagnetic radiation (EMI) of Class-D amplifiers. In some Class-D amplifiers, you also need the LC filter to ensure high efficiency outputs. This application report presents the implementations and theories of LC filter design for Class-D audio amplifiers using the AD (Traditional) and BD Class-D modulation designs. Contents 1 LC Filters Implementation .................................................................................................. 3 1.1 Terminology ......................................................................................................... 4 1.2 Related Documentation ............................................................................................ 4 2 Frequency Response of LC Filters ........................................................................................ 5 3 Types of Class-D Modulation Techniques................................................................................ 7 3.1 AD (Traditional) Modulation ....................................................................................... 7 3.2 BD Modulation....................................................................................................... 8 3.3 1SPW and Ternary Modulation .................................................................................. 9 4 LC Output Filter for Bridged Amplifiers ................................................................................. -

Lesson 3: RLC Circuits & Resonance

Lesson 3: RLC circuits & resonance • Inductor, Inductance • Comparison of Inductance and Capacitance • Inductance in an AC signals •RL circuits • LC circuits: the electric “pendulum” • RLC series & parallel circuits • Resonance P. Piot, PHYS 375 – Spring 2008 Inductor dI V=L L dT VL r ⇒Z= =iωL r r ∂B • Start with Maxwell’s equation ∇× E = − I ∂t • Integrate over a surface S (bounded by contour C) and Magnetic use Stoke’s theorem: flux in Weber r r r r r r ∂B r ∂Φ ∫∫∇× E.dA = ∫ E.dl = − ∫∫ .dA = − S S∈C S ∂t ∂t • The voltage is thus ∂Φ V = −emf = L ∂t P. Piot, PHYS 375 – Spring 2008 Wihelm Weber (1804-1891) Inductor • Now need to find a relation between magnetic field generated by a loop and current flowing through the loop’s wire. Used Biot and Savart’s law: r µ r rˆ dB = 0 Idl × ⇒ B ∝ I 4π r 2 • Integrate over a surface S the magnetic flux is going to be of the form Φ ≡ LI Inductance measured • The voltage is thus in Henri (symbol H) ∂Φ dI V = = L L ∂t dt Joseph Henri (1797-1878) P. Piot, PHYS 375 – Spring 2008 Inductor • Case of loop made with an infinitely thin wire µ B = δl.I 4π • If the inductor is composed of n loop per meter then total B-field is µ B = nI 4π Increase magnetic • So inductance is permeability (e.g. use metallic core instead of air) µ µ Φ ≡ BA = AnI ⇒ L = An 4π 4π Increase number of wire per unit length increase L Area of the loop P.