Xeon Phi™ Processor X200 Product Family Datasheet, Volume One: Electrical

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Supplemental Information

ARTICLE Supplemental Information PEDIATRICS Volume 146, Number 3, September 2020 1 SUPPLEMANTAL FIGURE 3 Example individualized antibiotic prescribing feedback report used in the DART study. Amox, amoxicillin; Clav, clavulanate; Rx, prescription. 2 ARTICLE SUPPLEMANTAL FIGURE 4 aRR for antibiotic prescribing from ITT analyses of the DART primary and secondary outcomes by study phase. PEDIATRICS Volume 146, Number 3, September 2020 3 SUPPLEMANTAL TABLE 5 ICD-10 Codes Used To Define ARTI Visits Diagnosis Included Conditions ICD-10 Codesa AOM Acute serous, allergic, and H65.0n, H65.11n, H65.19n, H65.2n, nonsuppurative otitis media; chronic H65.3n, H65.41n, H65.49n, H65.9n, serous, mucoid, allergic, and H66.00n, H66.01n, H66.1n, H66.2n, nonsuppurative otitis media H66.3Xn, H66.4n, H66.9n, and/or H67.n Pharyngitis Acute pharyngitis and tonsillitis J02, J02.n, J03, J03.00, J03.8n, and/or J03.9n Sinusitis Acute maxillary, frontal, ethmoidal, J01.0n, J01.1n, J01.2n, J01.3n, J01.4n, sphenoidal, and pansinusitis J01.8n, and/or J01.9n Viral ARTIsb Common cold, upper respiratory tract J00, J06.n, J10.1, J11.1, J20.3-J20.9, infection, influenza, bronchitis, and J21.n, and/or J40 bronchiolitis Additional Central venous catheter infections, T80.2n, T88.0n, W50.3n, W53.n1Xn, bacterial infection after immunization, bites and W54.0XXn, W55.n1Xn, W56.n1Xn, infectionsc scratches, infections due to specific W58.n1Xn, W59.n1Xn, W61.n1xn, pathogens (eg, Salmonella), sexually Y04.1xxn, A01.0n, A01.n, A02.n, A03.n, transmitted diseases, neutropenia, A04.n, A18.0n, -

Library of Congress Classification

R MEDICINE (GENERAL) R Medicine (General) Periodicals. Societies. Serials 5 International periodicals and serials 10 Medical societies Including aims, scope, utility, etc. International societies 10.5.A3 General works 10.5.A5-Z Individual societies America English United States. Canada 11 Periodicals. Serials 15 Societies British West Indies. Belize. Guyana 18 Periodicals. Serials 20 Societies Spanish and Portuguese Latin America 21 Periodicals. Serials 25 Societies 27.A-Z Other, A-Z 27.F7 French Europe English 31 Periodicals. Serials 35 Societies Dutch 37 Periodicals. Serials 39 Societies French 41 Periodicals. Serials 45 Societies German 51 Periodicals. Serials 55 Societies Italian 61 Periodicals. Serials 65 Societies Spanish and Portuguese 71 Periodicals. Serials 75 Societies Scandinavian 81 Periodicals. Serials 85 Societies Slavic 91 Periodicals. Serials 95 Societies 96.A-Z Other European languages, A-Z 96.H8 Hungarian Asia 97 English 97.5.A-Z Other European languages, A-Z 97.7.A-Z Other languages, A-Z Africa 98 English 98.5.A-Z Other European languages, A-Z 98.7.A-Z Other languages, A-Z 1 R MEDICINE (GENERAL) R Periodicals. Societies. Serials -- Continued Australasia and Pacific islands 99 English 99.5.A-Z Other European languages, A-Z 99.7.A-Z Other languages, A-Z Indexes see Z6658+ (101) Yearbooks see R5+ 104 Calendars. Almanacs Cf. AY81.M4 American popular medical almanacs 106 Congresses 108 Medical laboratories, institutes, etc. Class here papers and proceedings For works about these organizations see R860+ Collected works (nonserial) Cf. R126+ Ancient Greek and Latin works 111 Several authors 114 Individual authors Communication in medicine Cf. -

Modification of Transition-Metal Redox by Interstitial Water In

Modification of Transition-Metal Redox by Interstitial Water in Hexacyanometallate Electrodes for Sodium-Ion Batteries Jinpeng Wu†, #, Jie Song‡, Kehua Dai※, #, Zengqing Zhuo§, #, L. Andrew Wray⊥, Gao Liu#, Zhi-xun Shen†, Rong Zeng*, ‖, Yuhao Lu*, ‡, Wanli Yang*, # †Geballe Laboratory for Advanced Materials, Stanford University, Stanford, California 94305, USA #Advanced Light Source, Lawrence Berkeley National Laboratory, Berkeley, California 94720, United States ‡Novasis Energies, Inc., Vancouver, Washington, 98683, United States ※School of Metallurgy, Northeastern University, Shenyang 110819, China §School of Advanced Materials, Peking University Shenzhen Graduate School, Shenzhen 518055, China ⊥Department of Physics, New York University, New York, New York 10003, United States ‖Department of Electrical Engineering, Tsinghua University, Beijing 100084, China ABSTRACT A Sodium-ion battery (SIB) solution is attractive for grid-scale electrical energy storage. Low-cost hexacyanometallate is a promising electrode material for SIBs because of its easy synthesis and open framework. Most hexacyanometallate- based SIBs work with aqueous electrolyte and interstitial water in the material has been found to strongly affect the electrochemical profile, but the mechanism remains elusive. Here we provide a comparative study of the transition-metal redox in hexacyanometallate electrodes with and without interstitial water based on soft X-ray absorption spectroscopy and theoretical calculations. We found distinct transition-metal redox sequences in hydrated and anhydrated NaxMnFe(CN)6·zH2O. The Fe and Mn redox in hydrated electrodes are separated and at different potentials, leading to two voltage plateaus. On the contrary, mixed Fe and Mn redox at the same potential range is found in the anhydrated system. This work reveals for the first time that transition-metal redox in batteries could be strongly affected by interstitial molecules that are seemingly spectators. -

Thierry Moreau

Compilation and Hardware Support for Approximate Acceleration Thierry Moreau, Adrian Sampson, Andre Baixo, Mark Wyse, Ben Ransford, Jacob Nelson, Hadi Esmaeilzadeh (Georgia Tech), Luis Ceze and Mark Oskin University of Washington [email protected] Theme: 2384.004 1 Thierry Moreau Approximate Computing Aims to exploit application resilience to trade-off quality for efficiency 2 Thierry Moreau Approximate Computing 3 Thierry Moreau Approximate Computing ✅ Accurate ✅ Approximate ❌ Expensive ✅ Cheap 4 Thierry Moreau 5 Thierry Moreau 6 Thierry Moreau 7 Thierry Moreau Neural Networks as Approximate Accelerators CPU Esmaeilzadeh et al. [MICRO 2012] 8 Thierry Moreau Neural Acceleration float foo (float a, float b) { AR F … NPUM P G return val; approximation acceleration } 9 Thierry Moreau Neural Acceleration compiler-support float foo (float a, float b) { AR F … NPUM P G return val; approximation acceleration } ACCEPT* *Sampson et. al [UW-TR] 10 Thierry Moreau Neural Acceleration compiler-support HW-support float foo (float a, float b) { AR F … NPUM P G return val; approximation acceleration } ACCEPT SNNAP* *Moreau et. al [HPCA2015] 11 Thierry Moreau Neural Acceleration compiler-support HW-support float foo (float a, float b) { AR F … NPUM P G return val; approximation acceleration } ACCEPT SNNAP 3.8x speedup and 2.8x efficiency - 10% error 12 Thierry Moreau Talk Outline Introduction Compiler Support with ACCEPT SNNAP Accelerator design Evaluation & Comparison with HLS 13 Thierry Moreau Compilation Overview code 1. Region detection annotation 14 Thierry Moreau Compilation Overview ACCEPT code region detection 1. Region detection & program annotation instrumentation 15 Thierry Moreau Compilation Overview ACCEPT code region detection 1. Region detection & program annotation instrumentation back prop. -

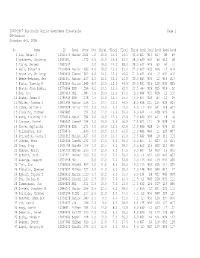

2006-2007 Wisconsin Junior Open/Open Crosstable Page 1 UW-Oshkosh November 4-5, 2006

2006-2007 Wisconsin Junior Open/Open Crosstable Page 1 UW-Oshkosh November 4-5, 2006 No. Name ID Team Rate Pts TBrk1 TBrk2 TBrk3 TBrk4 Rnd1 Rnd2 Rnd3 Rnd4 Rnd5 1 Luo, Brian J 12910173 Madisn 2024 5.0 16.0 15.0 54.0 32.0 W27 W13 W17 W9 W3 2 Mckinney, Christop 12934651 1772 4.5 16.0 14.5 52.0 28.0 W30 W33 W6 W10 D8 3 Yusim, Sergey 12852542 4.0 19.0 14.0 58.0 28.0 W12 W29 W5 W4 L1 4 Bell, Samuel W 21014944 Madisn 1663 4.0 15.0 13.0 51.0 22.0 W22 W35 W16 L3 W14 5 Brown Jr, Christop 12849430 GlenNi 1501 4.0 14.5 12.0 46.0 21.0 W31 W34 L3 W21 W16 6 Webne-Behrman, Ger 12901591 Madisn 1437 4.0 14.5 12.0 43.5 20.0 W43 W36 L2 W19 W13 7 Hintz, Timothy M 12752556 Marion 1545 4.0 13.5 12.0 44.5 20.0 W37 W19 L10 W33 W25 8 Bowen, John Armbru 12779264 USM 1596 4.0 13.5 11.5 42.0 22.5 -H- W26 W15 W14 D2 9 Her, Sou 12805616 MSL 1687 3.5 16.5 12.5 51.0 19.5 W44 W21 W18 L1 D10 10 Bowen, James H 12786949 USM 1278 3.5 14.0 12.5 45.0 15.5 W53 W49 W7 L2 D9 11 Miller, Joshua D 12871494 Marion 1516 3.5 13.5 10.0 44.5 18.0 W38 D15 L14 W24 W29 12 Dumke, Nathan C 12849428 Marion 1227 3.5 13.5 9.0 43.0 16.0 L3 W41 W34 D18 W27 13 Clausing, Michael 12864685 1254 3.0 17.0 10.0 50.0 16.0 W24 L1 W38 W20 L6 14 Wang, Xiaoming Tim 12976014 MadJf 1254 3.0 16.5 12.0 47.5 17.0 W40 W20 W11 L8 L4 15 Lancour, Daniel 12859342 JanesP 1158 3.0 16.0 9.5 46.5 17.5 W23 D11 L8 W28 D18 16 Ghose, Saptarshi 12870578 USM 1271 3.0 14.5 11.0 42.5 13.0 W45 W28 L4 W39 L5 17 Gallenberg, Bob 12779870 1436 3.0 13.5 10.0 41.5 11.0 W41 W46 L1 L25 W37 18 Petrashek, Casey D 12911815 Madisn 1427 3.0 13.0 -

Heater Element Specifications Bulletin Number 592

Technical Data Heater Element Specifications Bulletin Number 592 Topic Page Description 2 Heater Element Selection Procedure 2 Index to Heater Element Selection Tables 5 Heater Element Selection Tables 6 Additional Resources These documents contain additional information concerning related products from Rockwell Automation. Resource Description Industrial Automation Wiring and Grounding Guidelines, publication 1770-4.1 Provides general guidelines for installing a Rockwell Automation industrial system. Product Certifications website, http://www.ab.com Provides declarations of conformity, certificates, and other certification details. You can view or download publications at http://www.rockwellautomation.com/literature/. To order paper copies of technical documentation, contact your local Allen-Bradley distributor or Rockwell Automation sales representative. For Application on Bulletin 100/500/609/1200 Line Starters Heater Element Specifications Eutectic Alloy Overload Relay Heater Elements Type J — CLASS 10 Type P — CLASS 20 (Bul. 600 ONLY) Type W — CLASS 20 Type WL — CLASS 30 Note: Heater Element Type W/WL does not currently meet the material Type W Heater Elements restrictions related to EU ROHS Description The following is for motors rated for Continuous Duty: For motors with marked service factor of not less than 1.15, or Overload Relay Class Designation motors with a marked temperature rise not over +40 °C United States Industry Standards (NEMA ICS 2 Part 4) designate an (+104 °F), apply application rules 1 through 3. Apply application overload relay by a class number indicating the maximum time in rules 2 and 3 when the temperature difference does not exceed seconds at which it will trip when carrying a current equal to 600 +10 °C (+18 °F). -

K-12 Individual No. Name Team Gr Rate Pts Tbrk1 Tbrk2 Tbrk3 Tbrk4

K-12 Individual No. Name Team Gr Rate Pts TBrk1 TBrk2 TBrk3 TBrk4 Rnd1 Rnd2 Rnd3 Rnd4 Rnd5 Rnd6 1 Chakraborty, Dipro 11 2299 5.5 21 24 43 20.5 W27 W12 W5 W32 W8 D3 State Champion, AZ Denker Representative 2 Yim, Tony Sung BASISS 8 2135 5 20.5 23.5 38.5 17.5 W24 W10 D3 D16 W11 W9 3 Aletheia-Zomlefer, Soren CHANPR 11 1961 5 20 23 35.5 18.5 W25 W26 D2 W40 W15 D1 4 Desmarais, Nicholas Eduard NOTRED 10 1917 5 18 20 33 18 W39 W23 W18 L15 W10 W8 5 Wong, Kinsleigh Phillip CFHS 10 1992 4.5 20 20 24.5 15 -X- W17 L1 W26 D7 W15 6 Todd, Bryce BASISC 10 1923 4.5 17 19 26.5 14.5 W38 D18 L9 W23 W21 W16 7 Chaliki, Kalyan DSMTHS 9 1726 4.5 17 18.5 26 15 W46 L16 W28 W22 D5 W17 8 Li, Bohan UHS 9 2048 4 22 25 29 18 W30 W11 W45 W9 L1 L4 9 Mittal, Rohan CFHS 9 1916 4 19.5 20.5 23 17 W47 W22 W6 L8 W20 L2 10 Pennock, Joshua CFHS 10 1682 4 19 22 24 14 W31 L2 W25 W21 L4 W29 11 Aradhyula, Sumhith CFHS 9 1631 4 18 20 22 14 W41 L8 W38 W13 L2 W19 12 Johnston, Nicolas Godfrey CFHS 9 1803 4 18 19.5 21 13 W43 L1 W29 L17 W24 W20 13 Martis, Tyler BRHS 12 1787 4 17 18 21 13 W42 L15 W24 L11 W18 W22 14 Plumb, Justin Rodney GCLACA 10 1700 4 16 17 20 13 W51 L32 W19 L20 W28 W27 15 Martinez, Isaac GLPREP 10 2159 3.5 21.5 24.5 27.5 16 W28 W13 D16 W4 L3 L5 16 Chen, Derek H CFHS 10 1965 3.5 21 23.5 26 15.5 W35 W7 D15 D2 D17 L6 17 Woodson, Tyler GILBHS 1640 3.5 19 19 17.5 14 W50 L5 W30 W12 D16 L7 18 Cancio, Aiya CFHS 9 1469 3.5 18.5 20 17.5 12.5 W36 D6 L4 W46 L13 W25 AZ Girls' Invitational Representative 19 Folden, Kurt CHANPR 10 1207 3 14 18 12 10 L32 W50 L14 W31 W23 L11 20 Thornton, -

Office of Personnel Management (Opm)

Friday April 25, 1997 Part XXXVI Office of Personnel Management Semiannual Regulatory Agenda federal register 22499 VerDate 14-MAR-97 10:08 Apr 25, 1997 Jkt 173997 PO 00000 Frm 00001 Fmt 4717 Sfmt 4717 E:\FR\FM\ADV88.034 25ap34 22500 Federal Register / Vol. 62, No. 80 / Friday, April 25, 1997 / Unified Agenda OFFICE OF PERSONNEL MANAGEMENT (OPM) OPM OFFICE OF PERSONNEL SUMMARY: The following Office of binding obligation on the Office of MANAGEMENT Personnel Management (OPM) Personnel Management with regard to regulations are scheduled for any specific item on the agenda. 5 CFR Ch. I development or review from April 1, Additional regulatory action is not 1997, through March 31, 1998. This precluded. agenda carries out OPM's Semiannual Regulatory Agenda responsibilities to publish a semiannual FOR FURTHER INFORMATION CONTACT: AGENCY: Office of Personnel agenda under E.O. 12866 ``Regulatory Jacquline D. Carter, (202) 606-1973. Management. Planning and Review'' and the Regulatory Flexibility Act (5 U.S.C. Office of Personnel Management. ACTION: Semiannual regulatory agenda. chapter 6). This publication in the James B. King, Federal Register does not impose a Director. Prerule Stage Sequence Regulation Title Identifier Number Number 3646 Availability of Official Information ................................................................................................................................... 3206-AG92 Proposed Rule Stage Regulation Sequence Title Identifier Number Number 3647 Appointment of Noncitizens in the Excepted Service ................................................................................................... -

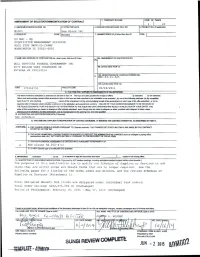

Modification No. 005 to Contract No. NRC-33-11-325

US NRC - Ho ACQUISITION MANAGEMENT DIVISION MAIL STOP 3WFN-05-C64MP WASHINGTON DC 20555-0001 DELL SERVICES FEDERAL GOVERNMENT INC 8270 WILLOW OAKS CORPORATE DR FATRFAX VA 220314514 The abow ma tered so- I ", Manerided m set fat in Ieto 141 The hour an da* cqilledf McWs of Ofrs -j isaexied. jis no exisixid Oilers rrujaeanolivedge MeOWfof Iftharrniernta prior to Viaehour arid dabespecifed in tife solofajon of -s aryunded , by one of Stefojowbig me~oda: (a) By owaripleligi itemr 8arid 15.arid raftmn __ __ copon of Mtewm~enhnun (b) By adwinoviedgtogiaoWdp of Viis anandelefit on each copy ofte o~w taibiiftied; or (c) By seper letter or tetegm whch Incudkes a ref• n o owe imiaon d nwKkTmnbem FAILURE OF YOUR ACKNOWLEDOGEMENT TO BE RECEIVED AT THE PLACE DESIGNATED FOR THE RECEIPT OF OFFERS PFRORTO THE HOUR AMD DATESPECIFIED MAY RESULT IN REJECTION OF YOUR OFFER Ifby vfte of tis antendyient you desi to dvage an offer saready ab e. wih dmwte May be nsde by elefgramor letter. Provided each telegramof lefter makes refernce S1edueolialimto andUdarnardmenl, 00 to received pqw so tu opefta h" &Wdasecifed- 12.ýACCOUINTING AND APPROPRIATION DATA (ff req~iad See Schedule I& THIlSITr ONLY APPLIES TO MOC1U1IATIOWOF CONTRACT1SOS. ITMOOIEZ lTEMCONTRACTM R NO. AS DOCRISMN InM 14. ChWCKO A- THIS CHANGE ORDER IS ISSUED PURSUANT T(Sp( sutojy)~ecify THE CHANGES SET FORTH IN ITEM 14 ARE MAE IN THE CONTRACT OROER NO. IN ITEM 10A. B.THE ABOVE NUMBERED CONTRACT/ORDER IS 1100011P* 7~1, EinUSTE01111dTRATI' CHANGES (&Midas dOites In pamwv ollt. AppmTonekn d3e, ef) SET FORTH IN ITEM 14. -

Policy & Governance Committee

AGENDA BOG Policy & Governance Committee Meeting Date: February 12, 2021 Location: Videoconference Chair: Kamron Graham Vice-Chair: Kate Denning Members: Gabriel Chase, Kate Denning, John Grant, Rob Milesnick, Curtis Peterson, Joe Piucci, David Rosen Staff Liaison: Helen M. Hierschbiel Charge: Develops and monitors the governing rules and policies relating to the structure and organization of the bar; ensures that all bar programs and services comply with organizational mandates and achieve desired outcomes. Identifies and brings emerging issues to the BOG for discussion and action. 2021 PGC Work Plan 1. Wellness Task Force Report. Review report and decide whether to pursue any Exhibit Action 10 recommendations. 2. Evidence-Based Decision-Making Policy. Review Futures Task Force recommendation regarding evidence-based decision-making To Be Posted Action 10 policy and consider whether to adopt the recommended policy. 3. HOD Authority. Discuss whether to pursue changes to limits of HOD authority either Exhibit Action 10 through amendments to HOD Rules or Bar Act. 4. OSB Bylaw Overhaul. Review draft of OSB bylaw overhaul, splitting between policies and Exhibit Discussion 20 bylaws. 5. Bar Sponsorship of Lawyer Referral Services. Review issue presented by Legal Ethics Exhibit Discussion 20 Committee. February 12, 2021 Policy & Governance Committee Agenda Page 2 6. Section Program Review. Review feedback Exhibit Discussion 20 regarding proposed changes to bylaws. 7. Approve minutes of January 8, 2021 meeting. Exhibit Action 1 2021 POLICY & GOVERNANCE WORK PLAN February 12, 2021 draft 2021 AREAS OF TO DO TASKS IN PROCESS (PGC) PGC TASKS DONE IN PROCESS (BOG) BOG TASKS FOCUS 1. Identify information needed 1. -

Hogan Lovells US LLP Columbia Square 555 Thirteenth Street, NW Washington, DC 20004 T +1 202 637 5600 F +1 202 637 5910

Hogan Lovells US LLP Columbia Square 555 Thirteenth Street, NW Washington, DC 20004 T +1 202 637 5600 F +1 202 637 5910 www.hoganlovells.com MEMORANDUM From: Gary Jay Kushner Joseph A. Levitt Leigh G. Barcham Date: November 12, 2018 Re: OMB Releases Fall 2018 Unified Agenda of Regulatory Actions The Office of Management and Budget (OMB) recently released the Fall 2018 Unified Agenda of Regulatory Actions, which outlines the rulemaking actions currently under development in each federal agency. This memorandum summarizes the major actions that may be of particular interest to the food industry that are being planned by the U.S. Food and Drug Administration (FDA) and the United States Department of Agriculture’s (USDA’s) Food Safety and Inspection Service (FSIS), Animal and Plant Health Inspection Service (APHIS), Food and Nutrition Service (FNS), and Agricultural Marketing Service (AMS). After highlighting the most significant priorities, we provide charts for each agency that provide additional details on their plans. More information can be found by clicking on the blue link next to each item, which will take you to a specific page about each agenda item on OMB’s website. We want to caution that the dates included in the Unified Agenda are not commitments to act on or by the date shown and simply indicate the agencies’ aspirations. Rather than focusing on projected dates, the Unified Agenda is a valuable tool to identify the substantive issues the agencies consider to be priorities for rulemaking. FDA’s current priorities include the following: FDA has completed the seven major rulemakings under the FDA Food Safety Modernization Act (FSMA) and the agency has turned its efforts to more discrete actions to fine tune the regulations. -

1St IRF Asia Regional Congress & Exhibition

1st IRF Asia Regional Congress & Exhibition Bali, Indonesia November 17–19 , 2014 For Professionals. By Professionals. "Building the Trans-Asia Highway" Bali’s Mandara toll road Executive Summary International Road Federation Better Roads. Better World. 1 International Road Federation | Washington, D.C. ogether with the Ministry of Public Works Indonesia, we chose the theme “Building the Trans-Asia Highway” to bring new emphasis to a visionary project Tthat traces its roots back to 1959. This Congress brought the region’s stakeholders together to identify new and innovative resources to bridge the current financing gap, while also sharing case studies, best practices and new technologies that can all contribute to making the Trans-Asia Highway a reality. This Congress was a direct result of the IRF’s strategic vision to become the world’s leading industry knowledge platform to help countries everywhere progress towards safer, cleaner, more resilient and better connected transportation systems. The Congress was also a reflection of Indonesia’s rising global stature. Already the largest economy in Southeast Asia, Indonesia aims to be one of world’s leading economies, an achievement that will require the continued development of not just its own transportation network, but also that of its neighbors. Thank you for joining us in Bali for this landmark regional event. H.E. Eng. Abdullah A. Al-Mogbel IRF Chairman Minister of Transport, Kingdom of Saudi Arabia Indonesia Hosts the Region’s Premier Transportation Meeting Indonesia was the proud host to the 1st IRF Asia Regional Congress & Exhibition, a regional gathering of more than 700 transportation professionals from 52 countries — including Ministers, senior national and local government officials, academics, civil society organizations and industry leaders.