Gate and Base Circuits and Protection

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Unit-1 Mphycc-7 Ujt

UNIT-1 MPHYCC-7 UJT The Unijunction Transistor or UJT for short, is another solid state three terminal device that can be used in gate pulse, timing circuits and trigger generator applications to switch and control either thyristors and triac’s for AC power control type applications. Like diodes, unijunction transistors are constructed from separate P-type and N-type semiconductor materials forming a single (hence its name Uni-Junction) PN-junction within the main conducting N-type channel of the device. Although the Unijunction Transistor has the name of a transistor, its switching characteristics are very different from those of a conventional bipolar or field effect transistor as it can not be used to amplify a signal but instead is used as a ON-OFF switching transistor. UJT’s have unidirectional conductivity and negative impedance characteristics acting more like a variable voltage divider during breakdown. Like N-channel FET’s, the UJT consists of a single solid piece of N-type semiconductor material forming the main current carrying channel with its two outer connections marked as Base 2 ( B2 ) and Base 1 ( B1 ). The third connection, confusingly marked as the Emitter ( E ) is located along the channel. The emitter terminal is represented by an arrow pointing from the P-type emitter to the N-type base. The Emitter rectifying p-n junction of the unijunction transistor is formed by fusing the P-type material into the N-type silicon channel. However, P-channel UJT’s with an N- type Emitter terminal are also available but these are little used. -

Thyristors.Pdf

THYRISTORS Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. Thyristors Thyristors are a class of semiconductor devices characterized by 4-layers of alternating p and n material. Four-layer devices act as either open or closed switches; for this reason, they are most frequently used in control applications. Some thyristors and their symbols are (a) 4-layer diode (b) SCR (c) Diac (d) Triac (e) SCS Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. The Four-Layer Diode The 4-layer diode (or Shockley diode) is a type of thyristor that acts something like an ordinary diode but conducts in the forward direction only after a certain anode to cathode voltage called the forward-breakover voltage is reached. The basic construction of a 4-layer diode and its schematic symbol are shown The 4-layer diode has two leads, labeled the anode (A) and the Anode (A) A cathode (K). p 1 n The symbol reminds you that it acts 2 p like a diode. It does not conduct 3 when it is reverse-biased. n Cathode (K) K Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. The Four-Layer Diode The concept of 4-layer devices is usually shown as an equivalent circuit of a pnp and an npn transistor. Ideally, these devices would not conduct, but when forward biased, if there is sufficient leakage current in the upper pnp device, it can act as base current to the lower npn device causing it to conduct and bringing both transistors into saturation. -

50 Simple L.E.D. Circuits

50 Simple L.E.D. Circuits R.N. SOAR r de Historie v/d Radi OTH'IEK 50 SIMPLE L.E.D. CIRCUITS by R. N. SOAR BABANI PRESS The Publishing Division of Babani Trading and Finance Co. Ltd. The Grampians Shepherds Bush Road London W6 7NI- England Although every care is taken with the preparation of this book, the publishers or author will not be responsible in any way for any errors that might occur. © 1977 BA BAN I PRESS I.S.B.N. 0 85934 043 4 First Published December 1977 Printed and Manufactured in Great Britain by C. Nicholls & Co. Ltd. f t* -i. • v /“ ..... tr> CONTENTS U.V.H.R* Circuit Page No. 1 LED Pilot Light......................................... 7 2 LED Stereo Beacon.................................... 8 3 Stereo Decoder Mono/Sterco Indicator . 9 4 Subminiature LED Torch........................... 10 5 Low Voltage Low Current Supply............ 11 6 Microlight Indicator .................................. 12 7 Ultra Low Current LED Switching Indicator 13 8 LED Stroboscope....................................... 14 9 12 Volt Car Circuit Tester........................... 15 10 Two Colour LED......................................... 16 11 12 Volt Car “Fuse Blown” Indicator.......... 17 12 LED Continuity Tester............................... 17 13 LED Current Overload Indicator.............. 18 14 LED Current Range Indicator................... 20 15 1.5 Volt LED “Zener”................. '............ 22 16 Extending Zener Voltage........................... 22 17 Four Voltage Regulated Supply................. 23 18 PsychaLEDic Display.................................. 24 .19 Dual Colour Display.................................... 25 20 Dual Signal Device....................................... 26 21 LED Triple Signalling.................................. 27 22 Sub-Miniature Light Source for Model Railways . 28 23 Portable Television Protection Circuit . 29 24 Improved Portable TV Protection Circuit 30 25 LED Battery Tester.............................. -

The Unijunction Transistor

ASE The Unijunction Transistor The unijunction transistor The unijunction transistor was one of the most attractive, simple and versatile semiconductor devices made available to electronic designers until discrete components were replaced by integrated circuits. The device was introduced in 1955 by General Electric. Here the article from Electronics, March 1955. In the article the device was referred to as a double base diode but soon later the name was changed to unijunction transistor or UJT UJT was a simple device, a silicon N-type bar with two ohmic contacts at both ends and a P-N junction about at two third of its length. The intermediate electrode is called emitter, while the two end contacts are referred to as B1 and B2 bases, B1 being the one farthest from the emitter. The construction of UJT and the related symbol are given in the figure below: Fig. 1 - Symbols used for UJT and internal construction of the device. The interbase resistance is somewhere from 5 and 10 kohms. B2 is normally biased at a positive voltage, Vbb, and B1 is grounded, the silicon bar acting as a voltage divider. No current can pass through the emitter until the P-N junction is reverse- biased. The conduction can take place only at an emitter voltage equal to the voltage existing on the voltage divider plus the direct drop on the junction, 0.67 volt at 25ºC. This value is defined by the intrinsic stand-off ratio, η, which is equivalent to the internal partition ratio. Fig. 2 - Equivalent circuit of UJT and influence of emitter current on Rb1 resistance. -

EC 8252 – ELECTRON DEVICES Department of ECE UNIT V – POWER & DISPLAY DEVICE

EC 8252 – ELECTRON DEVICES Department of ECE UNIT V – POWER & DISPLAY DEVICE UJT (UNIJUNCTION TRANSISTOR) UJT is a three terminal semiconductor switching device. As it has only one PN junction and three leads it is commonly NUTSHELL called as Unijunction Transistor. Three Terminal Basic Structure One PN junction It consists of a lightly doped N – type silicon bar with a heavily doped P – type material alloyed to its one side closer to B2 for producing single PN junction. The emitter leg is drawn at an angle vertical and the arrow indicates the direction of conventional current. Basic StructureCircuit Symbol Equivalent Circuit Characteristics of UJT: Interbase Resistance between B2 and B1of the silicon bar NUTSHELL is . With emitter terminal open, if voltage VBB is applied between the two bases, a voltage gradient is Voltage V1 reverse biased established along the N – type bar. Positive voltage VE Negative voltage VE The voltage drop across RB1 is Intrinsic Stand – off ratio, (typical value of η ranges from 0.56 to 0.75) 2020-2021 Jeppiaar Institute of Technology EC 8252 – ELECTRON DEVICES Department of ECE UNIT V – POWER & DISPLAY DEVICE The voltage V1 reverse biases the PN junction and emitter current is cut – off. But a small leakage current flows from B2 to emitter due to minority carriers. If a positive voltage VE is applied to emitter, the PN junction will remain reverse biased so long as VE < V1. If VE exceeds V1 by the cut – in voltage Vγ, the diode becomes forward biased. Under this condition, holes are injected into the N – type Bar. -

The Bipolar Junction Transistor (BJT)

The Bipolar Junction Transistor (BJT) Introduction he transistor, derived from transfer resistor, is a three terminal device whose resistance between two terminals is controlled by the third. The term bipolar reflects the fact that T there are two types of carriers, holes and electrons which form the currents in the transistor. If only one carrier is employed (electron or hole), it is considered a unipolar device like field effect transistor (FET). The transistor is constructed with three doped semiconductor regions separated by two pn junctions. The three regions are called Emitter (E), Base (B), and Collector (C). Physical representations of the two types of BJTs are shown in Figure (1–1). One type consists of two n -regions separated by a p-region (npn), and the other type consists of two p-regions separated by an n- region (pnp). Figure (1-1) Transistor Basic Structure The outer layers have widths much greater than the sandwiched p– or n–type layer. The doping of the sandwiched layer is also considerably less than that of the outer layers (typically, 10:1 or less). This lower doping level decreases the conductivity of the base (increases the resistance) due to the limited number of “free” carriers. Figure (1-2) shows the schematic symbols for the npn and pnp transistors 1 College of Electronics Engineering - Communication Engineering Dept. Figure (1-2) standard transistor symbol Transistor operation Objective: understanding the basic operation of the transistor and its naming In order for the transistor to operate properly as an amplifier, the two pn junctions must be correctly biased with external voltages. -

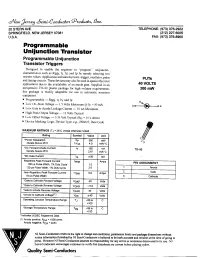

Programmable Unijunction Transistor

<^£mi-(2ondacto\ FELEPHONE: (973) 376-2922 20 STERN AVE. SPRINGFIELD, NEW JERSEY 07081 (212)227-6005 FAX: (973) 376-8960 U.S.A. Programmable Unijunction Transistor Programmable Unijunction Transistor Triggers Designed to enable the engineer to "program" unijunctioi characteristics such as RBB> T). IV an^ I? by merely selecting two resistor values. Application includes thyristor-trigger, oscillator, pulse PUTS and timing circuits. These devices may also be used in special thyristor applications due to the availability of an anode gate. Supplied in an 40 VOLTS inexpensive TO-92 plastic package for high-volume requirements, 300 mW this package is readily adaptable for use in automatic insertion equipment. • Programmable — RBB> *!> IV ar>d Ip • Low On-State Voltage — 1.5 Volts Maximum (2> IF = 50 mA AO- -OK • Low Gate to Anode Leakage Current — 10 nA Maximum • High Peak Output Voltage — 11 Volts Typical • Low Offset Voltage — 0.35 Volt Typical (Ro = 10 k ohms) • Device Marking: Logo, Device Type, e.g., 2N6027, Date Code MAXIMUM RATINGS (Tj = 25°C unless otherwise noted) Rating Symbol Value Unit "Power Dissipation PF 300 mW Derate Above 25°C 1/ejA 4.0 mW/'C *DC Forward Anode Current IT 150 mA TO-92 Derate Above 25°C 2.67 mA/°C *DC Gate Current IG ±50 mA Repetitive Peak Forward Current 'TRM Amps PIN ASSIGNMENT 100 us Pulse Width, 1% Duty Cycle 1.0 1 Anode •20 us Pulse Width, 1 % Duty Cycle 2.0 2 Gate Non-Repetitive Peak Forward Current 'TSM 5.0 Amps 10 us Pulse Width 3 Cathode 'Gate to Cathode Forward Voltage VGKF 40 Volts •Gate to Cathode -

![United States Patent [191 ' V[111 Patent Number: 4,829,290 Ford [45] Date of Patent: May 9, 1989](https://docslib.b-cdn.net/cover/1643/united-states-patent-191-v-111-patent-number-4-829-290-ford-45-date-of-patent-may-9-1989-3761643.webp)

United States Patent [191 ' V[111 Patent Number: 4,829,290 Ford [45] Date of Patent: May 9, 1989

United States Patent [191 ' v[111 Patent Number: 4,829,290 Ford [45] Date of Patent: May 9, 1989 [54] LOW VOLTAGE ALERT CIRCUIT Primary Examiner-—Joseph A. Orsino _ Assistant Examiner-Jeffery A. Hofsass [75] Inventor. Robert B. Ford, Tamarac, Fla. Attorney’ Agent, or Firm__Manin J. McKinley [73] Assignee: Motorola, Inc., Schaumburg, Ill. [21] Appl. No.: 140,520 [57] ABSTRACT [22] Filed: Jam 4, 1988 The ‘alert circuit includesla minimum number of ‘inex penslve dlscrete electronic components to provide a [51] . .......................... .; ..... .. GUBB 21/ 00 ?ashing alert when battery voltage drops below a pre_ """ 636g0/665g3;636%0/6%366_ determined trigger voltage. A single unijunction tran [ 320;“) ‘18. 354/72’ sistor circuit functions as a combination low voltage ’ ’ detector and oscillator to output periodic pulses to an [56] References Cited LED annunciator circuit when battery voltage is low. US. PATENT DOCUMENTS 3,810,144 5/1974 Clouse ........................... .. 340/663 X 4 Claims, 1 Drawing Sheet 21s 2283I 222 218 zozii a 220*: 208 j / 23o , 232 234 US. Patent May 9,1989 4,829,290 ‘ 104 112 108 1101... K 116< 105 -PRIOR ART FIGJ 4,829,290 1 2 understand how to adapt the exemplary embodiment to LOW VOLTAGE ALERT CIRCUIT their own design criteria. Referring to FIG. 2, a battery 202 is connected to ?rst BACKGROUND OF THE INVENTION and second input terminals 204 and 206. A 10K Ohm This invention pertains to low voltage detection cir 5 resistor 208 causes sufficient current to ?ow through cuits and, more particularly, to a combination low volt silicon diode 210 such that the forward voltage drop of age detection and alerting circuit that utilizes a relax diode 210 is approximately 0.6 volts. -

Unijunction Transistor

ELEC-SPD-S2 Credits: www.electronics-tutorials.ws 1/6 Home / Power Electronics / Unijunction Transistor Unijunction Transistor The UJT is a three-terminal, semiconductor device which exhibits negative resistance and switching characteristics for use as a relaxation oscillator in phase control applications The Unijunction Transistor or UJT for short, is another solid state three terminal device that can be used in gate pulse, timing circuits and trigger generator applications to switch and control either thyristors and triac’s for AC power control type applications. Like diodes, unijunction transistors are constructed from separate P-type and N-type semiconductor materials forming a single (hence its name Uni-Junction) PN-junction within the main conducting N-type channel of the device. Although the Unijunction Transistor has the name of a transistor, its switching characteristics are very different from those of a conventional bipolar or field effect transistor as it can not be used to amplify a signal but instead is used as a ON-OFF switching transistor. UJT’s have unidirectional conductivity and negative impedance characteristics acting more like a variable voltage divider during breakdown. Like N-channel FET’s, the UJT consists of a single solid piece of N-type semiconductor material forming the main current carrying channel with its two outer connections marked as Base 2 ( B2 ) and Base 1 ( B1 ). The third connection, confusingly marked as the Emitter ( E ) is located along the channel. The emitter terminal is / represented by an arrow pointing from the P-type emitter to the N-type base. The Emitter rectifying p-n junction of the unijunction transistor is formed by fusing the P-type material into the N-type silicon channel. -

Development of Pulse and Digital Circuits for Industrial Applications Elena Koleva1

Development of Pulse and Digital Circuits for Industrial Applications Elena Koleva1 Abstract – Have been developed in practice the main pulse and to the second ascending section of the volt – digital circuits, shapers, multivibrators, monostable ampere characteristic (p. 3). multivibrators, flip – flop, sawtooth generator, frequency Phototransistor VT1 opens up. dividers with the possibility of starting, stopping, control and maintaining galvanic decoupling between the control signals and outputs schemes for most developments. To build the circuits using different types of optocouplers and elements with negative resistance – tunnel diodes and unijunction transistors. Here are formulas for determining basic parameters of the circuits and developed methods for sizing of sawtooth and pulse generator. Keywords – Pulse and Digital Circuits, Optrons, Tunnel Diodes, Unijunction Transistors. I. DEVELOPMENT OF PULSE AND DIGITAL CIRCUITS WITH OPTOCOUPLERS AND TUNNEL DIODES The tunnel diode (TD) is an element with negative resistance (with N – shaped volt – ampere Fig. 1. Volt – ampere characteristic of TD characteristic). Other elements with a negative resistance in the volt – ampere characteristic are Gunn diode, avalanche Circuit of controllable oscillating multivibrators with TD transistor, unijunction transistor, dinistor, diak, thyristor, VD1 and phototransistor optocouplers O1 – Fig. 2, [3]. simistor and etc. [1]. Characteristic of TD is that it is low voltage and fast low – current element. For developments choosing TD type AI301Г (3I301Г) – Russia with the following parameters – Table 1: TABLE I Current in peak Imax = 10 mA Current in minimum Imin ≈ 1,25 mA Ratio Imax/ Imin = 8 Voltage in maximum Umax = 0,18 V Voltage in minimum Umin = 0,55 V Voltage nominal Uном = 0,8 V Current nominal Iном = 5 mA Switching time 50 ns Volt – ampere characteristic of TD is shown in Fig. -

United States Patent (19) 11 3,978,311 Toth (45) Aug

United States Patent (19) 11 3,978,311 Toth (45) Aug. 31, 1976 (54) VOLTAGE SENSOR CIRCUIT FOR AN ARC 3,258,596 6/1966 Green................................. 250/199 WELDING WIRE FEED CONTROL 3,488,586 11970 Watrous et al..................... 250/i99 w 3,604,884 9/197l Olsson .............................. 219/69 G 75 Inventor: Tibor Endre Toth, Florence, S.C. 3,794,841 2/1974 Consentino et al................. 250/99 73) Assignee: Union Carbide Corporation, New York, N.Y. Primary Examiner-J. V. Truhe Assistant Examiner-Clifford C. Shaw 22 Filed: Mar. 26, 1974 Attorney, Agent, or Firm-John R. Doherty (21) Appl. No.: 454,841 57 ABSTRACT 52 U.S. C. ............................. 219/131 F; 219/136 A sensor circuit coupled to an arc welding system and I5ll Int. Cl”............................................ B23K9/12 responsive to the arc welding voltage including an os (58) Field of Search. 219/131 F, 131 WR, 131 W, cillator and means for varying the frequency thereof in 219/135; 314/64; 250/199 response to the arc voltage, light emitting means re sponsive to the oscillator frequency, and detecting cir 56 References Cited cuit means responsive to the light emitting means for UNITED STATES PATENTS providing a DC voltage proportional to the arc voltage. 2,223,177 1 1/1940 Jones.................................... 3.14164 9. 2,636,102 4/1953 Lobosco.......................... 219/13 F 3 Claims, 2 Drawing Figures SENSOR CIRCUIT CONSTANT CURRENT O 8 AC/DC MOTOR CONTROL POWER SUPPLY O. O U.S. Patent Aug. 31, 1976 3,978,311 SENSOR CIRCUIT CONSTANT CURRENT o AC/DC POWER SUPPLYo O 3,978,311 1. -

A Controlled Negative-Resistance for Realization of Certain Network Functions

AN ABSTRACT OF THE THESIS OF JAMES DANIEL WAGNER for the M. S. in Electrical Engineering (Name) (Degree) (Major) Date thesis is presented Lay /y /7- Title A CONTROLLED NEGATIVE- RESISTANCE FOR REALIZATION OF CERTAIN NETWORK FUNCTIONS Abstract approved ajor professor A circuit which functions as a controlled negative- resistance is described and analyzed; the circuit contains two transistors, a break- down diode, and five resistors connected in a stable feedback config- uration. From the analysis a set of design equations is derived. An experimental circuit is described and a comparison between measured performance and design objectives is presented. Several network synthesis procedures are presented to provide background for experimental realizations using the controlled negative - resistance. The problem of biasing is examined for the synthesis techniques presented. Two experimental realizations, one providing gain and one pro- viding complex zeros of transmission, are described and performance is compared to theoretical specifications; in both cases the agreement is excellent. A CONTROLLED NEGATIVE -RESISTANCE FOR REALIZATION OF CERTAIN NETWORK FUNCTIONS by JAMES DANIEL WAGNER A THESIS submitted to OREGON STATE UNIVERSITY in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE June 1965 APPROVED: Pro scor of Elect, cal Engineering In Charge of Major ad of Depart e t :f i'ectrical Engineering Dean of Graduate School Date thesis is presented iY, /96r Typed by Lucinda M. Nyberg ACKNOWLEDGMENTS Appreciation is gratefully extended to the Department of Electri- cal Engineering of the School of Engineering, Oregon State University, and to Professor Leland C. Jensen for encouragement and assistance with this project.