Atari 2600 Programming for Newbies

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A History of Video Game Consoles Introduction the First Generation

A History of Video Game Consoles By Terry Amick – Gerald Long – James Schell – Gregory Shehan Introduction Today video games are a multibillion dollar industry. They are in practically all American households. They are a major driving force in electronic innovation and development. Though, you would hardly guess this from their modest beginning. The first video games were played on mainframe computers in the 1950s through the 1960s (Winter, n.d.). Arcade games would be the first glimpse for the general public of video games. Magnavox would produce the first home video game console featuring the popular arcade game Pong for the 1972 Christmas Season, released as Tele-Games Pong (Ellis, n.d.). The First Generation Magnavox Odyssey Rushed into production the original game did not even have a microprocessor. Games were selected by using toggle switches. At first sales were poor because people mistakenly believed you needed a Magnavox TV to play the game (GameSpy, n.d., para. 11). By 1975 annual sales had reached 300,000 units (Gamester81, 2012). Other manufacturers copied Pong and began producing their own game consoles, which promptly got them sued for copyright infringement (Barton, & Loguidice, n.d.). The Second Generation Atari 2600 Atari released the 2600 in 1977. Although not the first, the Atari 2600 popularized the use of a microprocessor and game cartridges in video game consoles. The original device had an 8-bit 1.19MHz 6507 microprocessor (“The Atari”, n.d.), two joy sticks, a paddle controller, and two game cartridges. Combat and Pac Man were included with the console. In 2007 the Atari 2600 was inducted into the National Toy Hall of Fame (“National Toy”, n.d.). -

Videogames in the Museum: Participation, Possibility and Play in Curating Meaningful Visitor Experiences

Videogames in the museum: participation, possibility and play in curating meaningful visitor experiences Gregor White Lynn Parker This paper was presented at AAH 2016 - 42nd Annual Conference & Book fair, University of Edinburgh, 7-9 April 2016 White, G. & Love, L. (2016) ‘Videogames in the museum: participation, possibility and play in curating meaningful visitor experiences’, Paper presented at Association of Art Historians 2016 Annual Conference and Bookfair, Edinburgh, United Kingdom, 7-9 April 2016. Videogames in the Museum: Participation, possibility and play in curating meaningful visitor experiences. Professor Gregor White Head of School of Arts, Media and Computer Games, Abertay University, Dundee, UK Email: [email protected] Lynn Parker Programme Leader, Computer Arts, Abertay University, Dundee, UK Email: [email protected] Keywords Videogames, games design, curators, museums, exhibition, agency, participation, rules, play, possibility space, co-creation, meaning-making Abstract In 2014 Videogames in the Museum [1] engaged with creative practitioners, games designers, curators and museums professionals to debate and explore the challenges of collecting and exhibiting videogames and games design. Discussions around authorship in games and games development, the transformative effect of the gallery on the cultural reception and significance of videogames led to the exploration of participatory modes and playful experiences that might more effectively expose the designer’s intent and enhance the nature of our experience as visitors and players. In proposing a participatory mode for the exhibition of videogames this article suggests an approach to exhibition and event design that attempts to resolve tensions between traditions of passive consumption of curated collections and active participation in meaning making using theoretical models from games analysis and criticism and the conceit of game and museum spaces as analogous rules based environments. -

Harmony Cartridge Online Manual

A new way to experience the Atari 2600. © Copyright 2009-2011 – AtariAge (atariage.com) Second printing Contents Introduction ____________________________________ 1 Getting Started with Harmony _______________________ 1 Harmony Firmware Upgrading ______________________ 3 Frequently Asked Questions ________________________ 5 Harmony File Extensions __________________________ 8 Harmony Technical Specifications ____________________ 9 Acknowledgments _______________________________ 9 Introduction The Harmony cartridge is a programmable add-on for the Atari 2600 console that allows you to load an entire library of games into a single cartridge and then select which title you want to play from a friendly, on-screen menu interface. It features an SD card interface, making it simple to access the large library of Atari 2600 software. The Harmony cartridge supports almost all of the titles that have been produced for the Atari 2600. It can also be used to run your own Atari 2600 game creations on a real console. The Harmony cartridge is flash-upgradeable, and will be updated to support future Atari 2600 developments. SD card slot Mini-B USB port Back edge of Harmony Cart This guide tells you how to make the most of your Harmony cartridge. It should be read thoroughly before the cartridge is used for the first time. Your Harmony cartridge will provide you with many years of Atari 2600 enjoyment. The following equipment is required to use the Harmony cartridge: 1) An Atari 2600, Atari 7800 or other Atari 2600-compatible console. 2) A Windows, Macintosh or Linux-based computer to transfer data onto the SD card. 3) An SD card adapter for your computer. 4) An SD or SDHC card up to 32GB capacity. -

Heroes of Warland in Madrid World Football Summit

PRESS RELEASE 24 September 2018 at 09:00 (EEST) Heroes of Warland in Madrid World Football Summit Nitro Games presents its upcoming game Heroes of Warland in World Football Summit this week in Madrid, Spain. “We consider Spain a very important market in the field of eSports. In WFS we’re presenting Heroes of Warland for Spanish speaking audience, as well as exploring opportunities related to competitive gaming and eSports on mobile.” says Jussi Tähtinen, CEO & Co-Founder, Nitro Games Oyj. The World Football Summit takes place in Teatro Goya, Madrid on September 24 – 25. WFS is the international event of the football industry, gathering 2300+ attendees and the most influential professionals from 80+ countries, as well as 160+ clubs and 100+ medias, in order to discuss the most relevant topics and to generate business opportunities. Several of these parties are also active in the field of eSports. Nitro Games is attending the event to showcase Heroes of Warland and Heroes & Superstars reality show. CEO Jussi Tähtinen is also a speaker at the event. Find out more about WFS: https://worldfootballsummit.com/en/ Heroes of Warland is now available in Google Play Open Beta in 139 countries. This means the game is available globally for early testers having Android devices, excluding China and few other countries. The game is featured in Google Play in Early Access category in all 139 countries. Heroes of Warland is a team-based competitive multiplayer game on mobile. With Heroes of Warland, Nitro Games is introducing hero-based shooter genre on mobile for the first time. -

Kaboom Atari Jaguar CD Homebrew | Ebay

Kaboom Atari Jaguar CD Homebrew | eBay http://www.ebay.com/itm/Kaboom-Atari-Jaguar-CD-homebrew/222218... Hi Bryan ! Daily Deals Gift Cards Sell Help & Contact My eBay 13 Shop by All Categories Search category Back to search results | Listed in category: Video Games & Consoles > Video Games Kaboom! Atari Jaguar CD homebrew 1 viewed per hour Item Like New | Add to watch list condition: Time left: 28d 23h 9/12, 9:15PM Seller information jeffreybonez2010 (205 ) 100% Positive feedback Price: US $29.99 Follow this seller See other items Best Offer: 3 watching Add to watch list Add to collection Tracked Longtime member Best offer available international Shipping Shipping: $19.09 International Priority Shipping to United Kingdom via the Global Shipping Program | See details Item location: Charlotte, North Carolina, United States Ships to: United States and many other countries | See details Import $0.00 (amount confirmed at checkout) Mouse over image to zoom charges: No additional import charges on delivery Delivery: Estimated between Wed. Aug. 24 and Sat. Sep. 3 Includes international tracking Payments: Credit Cards processed by PayPal Have one to sell? Get more time to pay. Apply Now | See Terms See details Any international shipping and import charges are paid in part to Pitney Bowes Inc. Learn More Returns: Seller does not offer returns. You are covered by the eBay Money Back Guarantee if you received an item that is not as described in the listing. Guarantee: | See details Get the item you ordered or get your money back. Covers your purchase price and original shipping. Description Shipping and payments Report item eBay item number: 222218487220 Seller assumes all responsibility for this listing. -

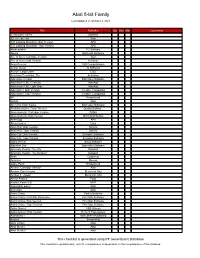

Atari 8-Bit Family

Atari 8-bit Family Last Updated on October 2, 2021 Title Publisher Qty Box Man Comments 221B Baker Street Datasoft 3D Tic-Tac-Toe Atari 747 Landing Simulator: Disk Version APX 747 Landing Simulator: Tape Version APX Abracadabra TG Software Abuse Softsmith Software Ace of Aces: Cartridge Version Atari Ace of Aces: Disk Version Accolade Acey-Deucey L&S Computerware Action Quest JV Software Action!: Large Label OSS Activision Decathlon, The Activision Adventure Creator Spinnaker Software Adventure II XE: Charcoal AtariAge Adventure II XE: Light Gray AtariAge Adventure!: Disk Version Creative Computing Adventure!: Tape Version Creative Computing AE Broderbund Airball Atari Alf in the Color Caves Spinnaker Software Ali Baba and the Forty Thieves Quality Software Alien Ambush: Cartridge Version DANA Alien Ambush: Disk Version Micro Distributors Alien Egg APX Alien Garden Epyx Alien Hell: Disk Version Syncro Alien Hell: Tape Version Syncro Alley Cat: Disk Version Synapse Software Alley Cat: Tape Version Synapse Software Alpha Shield Sirius Software Alphabet Zoo Spinnaker Software Alternate Reality: The City Datasoft Alternate Reality: The Dungeon Datasoft Ankh Datamost Anteater Romox Apple Panic Broderbund Archon: Cartridge Version Atari Archon: Disk Version Electronic Arts Archon II - Adept Electronic Arts Armor Assault Epyx Assault Force 3-D MPP Assembler Editor Atari Asteroids Atari Astro Chase Parker Brothers Astro Chase: First Star Rerelease First Star Software Astro Chase: Disk Version First Star Software Astro Chase: Tape Version First Star Software Astro-Grover CBS Games Astro-Grover: Disk Version Hi-Tech Expressions Astronomy I Main Street Publishing Asylum ScreenPlay Atari LOGO Atari Atari Music I Atari Atari Music II Atari This checklist is generated using RF Generation's Database This checklist is updated daily, and it's completeness is dependent on the completeness of the database. -

Openbsd Gaming Resource

OPENBSD GAMING RESOURCE A continually updated resource for playing video games on OpenBSD. Mr. Satterly Updated August 7, 2021 P11U17A3B8 III Title: OpenBSD Gaming Resource Author: Mr. Satterly Publisher: Mr. Satterly Date: Updated August 7, 2021 Copyright: Creative Commons Zero 1.0 Universal Email: [email protected] Website: https://MrSatterly.com/ Contents 1 Introduction1 2 Ways to play the games2 2.1 Base system........................ 2 2.2 Ports/Editors........................ 3 2.3 Ports/Emulators...................... 3 Arcade emulation..................... 4 Computer emulation................... 4 Game console emulation................. 4 Operating system emulation .............. 7 2.4 Ports/Games........................ 8 Game engines....................... 8 Interactive fiction..................... 9 2.5 Ports/Math......................... 10 2.6 Ports/Net.......................... 10 2.7 Ports/Shells ........................ 12 2.8 Ports/WWW ........................ 12 3 Notable games 14 3.1 Free games ........................ 14 A-I.............................. 14 J-R.............................. 22 S-Z.............................. 26 3.2 Non-free games...................... 31 4 Getting the games 33 4.1 Games............................ 33 5 Former ways to play games 37 6 What next? 38 Appendices 39 A Clones, models, and variants 39 Index 51 IV 1 Introduction I use this document to help organize my thoughts, files, and links on how to play games on OpenBSD. It helps me to remember what I have gone through while finding new games. The biggest reason to read or at least skim this document is because how can you search for something you do not know exists? I will show you ways to play games, what free and non-free games are available, and give links to help you get started on downloading them. -

How Actors Establish Generative Platforms by Instituting Control Points: the U.S

Paper to be presented at the DRUID Society Conference 2014, CBS, Copenhagen, June 16-18 How Actors Establish Generative Platforms By Instituting Control Points: The U.S. Video Game Industry Alexander Chekanov Esade Business School Business Network Dynamics [email protected] Joan Rodon Modol ESADE Business School Department of Information Systems, Research Group: Business [email protected] Abstract In our paper we examine how the proliferation and growth of a sector can be contingent on the set up of control points in a multi-platform industry through an historical overview of the U.S. home video game industry between 1976 and 1989. We address the critical issue on how do actors establish generative platforms by instituting a set of control points acceptable to others, providing evidence that an increased control can also feed extensive generativity. To achieve such purpose, we present an inductive study that illustrates how the U.S. home video game industry crashed in 1983, after the removal of architectural control points in the video games market, and how Nintendo introduced new architectural control points after the crash, describing the role of the control points in the recovery of the sector. Jelcodes:M10,O32 How Actors Establish Generative Platforms By Instituting Control Points: The U.S. Video Game Industry ABSTRACT In our paper we examine how the proliferation and growth of a sector can be contingent on the set up of control points in a multi-platform industry through an historical overview of the U.S. home video game industry between 1976 and 1989. We address the critical issue on how do actors establish generative platforms by instituting a set of control points acceptable to others, providing evidence that an increased control can also feed extensive generativity. -

The Introduction of Computer and Video Games in Museums – Experiences and Possibilities

The Introduction of Computer and Video Games in Museums – Experiences and Possibilities Tiia Naskali, Jaakko Suominen, and Petri Saarikoski University of Turku, Digital Culture, Degree Program of Cultural Production and Landscape Studies, Pori, Finland {tiia.naskali,jaakko.suominen,petri.saarikoski}@utu.fi Abstract. Computers and other digital devices have been used for gaming since the 1940s. However, the growth in popularity of commercial videogames has only recently been witnessed in museums. This paper creates an overview of how digital gaming devices have been introduced in museum exhibitions over the last fifteen years. The following discussion will give examples of exhibitions from different countries and provide answers to the following questions: Can digital games and gaming devices be used as promotional gimmicks for attracting new audiences to museums? How can mainframe computers be taken into account in digital game related exhibitions? How has the difference between cultural-historical and art museum contexts affected the methods for introducing digital games? Is there still room for general exhibitions of digital games or should one focus more on special theme exhibitions? How are museum professionals, researchers and computer hobbyists able to collaborate in exhibition projects? Keywords: Digital games, museums, exhibitions. 1 Introduction – Pulling in with Digital Games The popularity of digital games has increased during the last few decades. The playing of games plays an important role in many people’s lives, and the average age of players is, in many countries, almost 40 years-old. In Finland, for example, the average age of the digital game player was 37 years-old in 2011, while a total of 73 % of Finns played digital games. -

Parasites — Excavating the Spectravideo Compumate

ghosts ; replicants ; parasites — Excavating the Spectravideo CompuMate These are the notes I used for my final presentation in the summer Media Archaeology Class, alongside images I used as slides. As such, they’re quite provisional, and once I have some time to hammer them into more coherent thoughts, I’ll update this post accordingly! So this presentation is about articulating and beginning the work of theorizing what I’m provisionally calling “computational parasites.” This is provisional because I don’t particularly like the term myself but I figured it would be good to give it a shorthand so I don’t have to be overvague or verbose about these objects and practices throughout this presentation. As most of you know, I came to this class with a set of research questions about a particular hack of the SNES game Super Mario World, wherein a YouTube personality was able to basically terraform the console original into playing, at least in form although we can talk about content, the iPhone game Flappy Bird. This video playing behind me is that hack. This hack is evocative for me for the way it’s 1) really fucking weird, in terms of pushing hardware and software to their limits, and 2) begins to help me think through ideas of the lifecycle of software objects, to pilfer a phrase from a Ted Chiang novella, and how these lifecycles are caught up in infrastructures of nostalgia, supply chains, and different kinds of materiality. But as fate would have it, I haven’t spent that much time with this hack this week because I got entranced by a different, just as weird object: the Spectravideo CompuMate. -

A Page 1 CART TITLE MANUFACTURER LABEL RARITY Atari Text

A CART TITLE MANUFACTURER LABEL RARITY 3D Tic-Tac Toe Atari Text 2 3D Tic-Tac Toe Sears Text 3 Action Pak Atari 6 Adventure Sears Text 3 Adventure Sears Picture 4 Adventures of Tron INTV White 3 Adventures of Tron M Network Black 3 Air Raid MenAvision 10 Air Raiders INTV White 3 Air Raiders M Network Black 2 Air Wolf Unknown Taiwan Cooper ? Air-Sea Battle Atari Text #02 3 Air-Sea Battle Atari Picture 2 Airlock Data Age Standard 3 Alien 20th Century Fox Standard 4 Alien Xante 10 Alpha Beam with Ernie Atari Children's 4 Arcade Golf Sears Text 3 Arcade Pinball Sears Text 3 Arcade Pinball Sears Picture 3 Armor Ambush INTV White 4 Armor Ambush M Network Black 3 Artillery Duel Xonox Standard 5 Artillery Duel/Chuck Norris Superkicks Xonox Double Ender 5 Artillery Duel/Ghost Master Xonox Double Ender 5 Artillery Duel/Spike's Peak Xonox Double Ender 6 Assault Bomb Standard 9 Asterix Atari 10 Asteroids Atari Silver 3 Asteroids Sears Text “66 Games” 2 Asteroids Sears Picture 2 Astro War Unknown Taiwan Cooper ? Astroblast Telegames Silver 3 Atari Video Cube Atari Silver 7 Atlantis Imagic Text 2 Atlantis Imagic Picture – Day Scene 2 Atlantis Imagic Blue 4 Atlantis II Imagic Picture – Night Scene 10 Page 1 B CART TITLE MANUFACTURER LABEL RARITY Bachelor Party Mystique Standard 5 Bachelor Party/Gigolo Playaround Standard 5 Bachelorette Party/Burning Desire Playaround Standard 5 Back to School Pak Atari 6 Backgammon Atari Text 2 Backgammon Sears Text 3 Bank Heist 20th Century Fox Standard 5 Barnstorming Activision Standard 2 Baseball Sears Text 49-75108 -

The Intentions of International Tourists to Attend the 2016 Rio Summer Olympic and Paralympic Games: a Study of the Image of Rio De Janeiro and Brazil

Ann Appl Sport Sci 8(3): e798, 2020. http://www.aassjournal.com; e-ISSN: 2322–4479; p-ISSN: 2476–4981. 10.29252/aassjournal.798 ORIGINAL ARTICLE The Intentions of International Tourists to Attend the 2016 Rio Summer Olympic and Paralympic Games: A Study of the Image of Rio de Janeiro and Brazil Leonardo Jose Mataruna-Dos-Santos* College of Business Administration, American University in the Emirates, Dubai, UAE. Submitted 22 September 2019; Accepted in final form 27 February 2020. ABSTRACT Background. This paper investigates how hosting a mega sports event such as the 2016 Rio Games – Olympic and Paralympic influence the Rio de Janeiro and Brazil image’ like popular destinations among tourists. Objectives. The following hypotheses guided our research to identify the more positive image of Brazil as a tourism destination. Methods. A mixed research design combining both qualitative and quantitative approaches was used. Participants were recruited at the Technische Universität München and in the city center of Munich, Germany. The two dimensions (cognitive and affective) of the tourism destination image were considered to elaborate a questionnaire survey, which mixes both qualitative and quantitative methods. Results. The significant factors influencing the intentions of a person to attend the Games in Brazil are the positive portrayed image of the country and their sport interest. According to the multiple regression conducted, the only variables, which have influenced people’s intention to go to Brazil for the Olympics, were the image of the country as a tourism destination (β = 0.404, p < 0.05) and sports interests (β = 0.259, p < 0.05).