EK-VT278 Technical Description

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Digital Equipment: Corporation, Maynard, Massachusetts 01754 Digital Equipment Cor1poration • Maynard

TOPS .. 10 DOCUMENTATION DIRECTORY Order Number AA-0858C-TB April 1979 This document describes the manuals for the TOPS·10 Software Notebooks. This manual supersedes the TOPS·10 Documentation Directory, Order Number AA·0858B·TB. To order additional copies; of this document, contact the Software Distribution Center, Digital Equipment: Corporation, Maynard, Massachusetts 01754 digital equipment cor1poration • maynard. massachusetts First Printing, February, 1978 Upda ted, May, 1978 Updated, June, 1978 Updated, August, 1978 Revised, Nov~mber, 1978 Revised, April, 1979 The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document. The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. Digital Equipment Corporation assumes no responsibility for the use or reliability of its software on equipment that is not supplied by DIGITAL and its affiliated companies. copyright©l979 by Digital Equipment Corporation The postage-prepaid READER'S COMMENTS form on the last page of this document requests the user's critical evaluation to assist us in preparing future documentation. The following are trademarks of Digital Equipment Corporation: DIGITAL DECsystem-lO MASSBUS DEC DECSYSTEM-20 OMNIBUS PDP DEC tape OS/8 DECUS DIBOL PHA UNIBUS EDUSYSTEM RSTS COMPUTER LABS FLIP CHIP RSX COMTEX -

Cpu Identification Program. P?S Pal V08s Sat 11-Mar-17 Page 1

/ CPU IDENTIFICATION PROGRAM. P?S PAL V08S SAT 11-MAR-17 PAGE 1 1 1 / CPU IDENTIFICATION PROGRAM. 1 2 2 2 3 3 / LAST EDIT: 03-OCT-2016 CJL 3 4 4 4 5 5 / MUST BE ASSEMBLED WITH THE '/J' COMMAND-LINE SWITCH OFF IN P?S/8 PAL OR THE 5 6 6 / '/F' COMMAND-LINE SWITCH OFF IN OS/8 PAL8. 6 7 7 7 8 8 / THIS PROGRAM IDENTIFIES THE PARTICULAR MODEL OF PDP-8 THE PROGRAM IS RUNNING 8 9 9 / ON. THIS IS ACCOMPLISHED USING A SERIES OF TESTS FOR QUIRKS THAT APPLY TO THE 9 10 10 / VARIOUS MODELS. 10 11 11 11 12 12 / NOTE: MUCH OF THE CODE IN THIS PROGRAM WAS OBTAINED FROM THE KERMIT-12 SOURCE 12 13 13 / FILES; SOME MODIFICATIONS HAVE BEEN MADE THAT WILL EVENTUALLY BE APPLIED TO 13 14 14 / KERMIT-12 TO BETTER IDENTIFY THE COMPUTER. NOTE: KERMIT-12 USES A 14 15 15 / MODEL-DEPENDENT COMMAND PROMPT TO HELP ASSIST IN DETERMINING WHICH KERMIT IS 15 16 16 / CURRENTLY BEING ADDRESSED; IN CERTAIN CIRCUMSTANCES, TWO DIFFERENT SYSTEMS ARE 16 17 17 / IN USE. IT CAN SOMETIMES BE CONFUSING WHICH COMPUTER IS CURRENTLY IN EFFECT, 17 18 18 / THUS, USING MODEL-SPECIFIC PROMPTS CAN AID IN PREVENTING CONFUSION. AS 18 19 19 / CURRENTLY IMPLEMENTED AS OF THIS WRITING, KERMIT-12 CANNOT QUITE DISTINGUISH 19 20 20 / BETWEEN DECMATE SYSTEMS AND OTHER SYSTEMS BASED ON THE 6120 CHIP SUCH AS THE 20 21 21 / CPU-8 OR GIZMO. WHILE THIS ASPECT OF THE PROBLEM IS PURELY COSMETIC, 21 22 22 / KERMIT-12 HAS CONFIGURATION ISSUES WHEN RUN ON THESE PARTICULAR SYSTEMS. -

KTS-A Memory Management Control User's Guide Digital Equipment Corporation • Maynard, Massachusetts

--- KTS-A memory management control user's guide E K- KTOSA-U G-001 digital equipment corporation • maynard, massachusetts 1st Edition , July 1978 Copyright © 1978 by Digital Equipment Corporation The material in this manual is for informational purposes and is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual. Printed in U.S.A. This document was set on DIGITAL's DECset-8000 com puterized typesetting system. The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts: DIGITAL D ECsystem-10 MASSBUS DEC DECSYSTEM-20 OMNIBUS POP DIBOL OS/8 DECUS EDUSYSTEM RSTS UNI BUS VAX RSX VMS IAS CONTENTS Page CHAPTER 1 INTRODUCTION 1 . 1 SCOPE OF MANUAL ..................................................................................................................... 1-1 1.2 GENERAL DESCRI PTION ............................................................................................................. 1-1 1 .3 KT8-A SPECIFICATION S.............................................................................................................. 1-3 1.4 RELATED DOCUMENTS ............................................................................................................... 1-4 1 .5 SOFTWARE ..................................................................................................................................... 1-5 1.5.1 Diagnostic ............................................................................................................................. -

On the Cognitive Prerequisites of Learning Computer Programming

On the Cognitive Prerequisites of Learning Computer Programming Roy D. Pea D. Midian Kurland Technical Report No. 18 ON THE COGNITIVE PREREQUISITES OF LEARNING COMPUTER PROGRAMMING* Roy D. Pea and D. Midian Kurland Introduction Training in computer literacy of some form, much of which will consist of training in computer programming, is likely to involve $3 billion of the $14 billion to be spent on personal computers by 1986 (Harmon, 1983). Who will do the training? "hardware and software manu- facturers, management consultants, -retailers, independent computer instruction centers, corporations' in-house training programs, public and private schools and universities, and a variety of consultants1' (ibid.,- p. 27). To date, very little is known about what one needs to know in order to learn to program, and the ways in which edu- cators might provide optimal learning conditions. The ultimate suc- cess of these vast training programs in programming--especially toward the goal of providing a basic computer programming compe- tency for all individuals--will depend to a great degree on an ade- quate understanding of the developmental psychology of programming skills, a field currently in its infancy. In the absence of such a theory, training will continue, guided--or to express it more aptly, misguided--by the tacit Volk theories1' of programming development that until now have served as the underpinnings of programming instruction. Our paper begins to explore the complex agenda of issues, promise, and problems that building a developmental science of programming entails. Microcomputer Use in Schools The National Center for Education Statistics has recently released figures revealing that the use of micros in schools tripled from Fall 1980 to Spring 1983. -

DIBOL for Beginners Order No

DIBOL for Beginners Order No. AA-BI77 A-TK April 1984 Supersession: This is a new manual. Operating System: VAXNMS, CTS-300, RSTS/E, Professional, RSX-11 M-Plus, Micro/RSX, Professional CTS-300 Software Version: Applicable to all products containing DIBOL-83 . First Printing, April 1984 The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document. The software described in this document is furnished under a license and may only be used or copied in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software on equipment that is not supplied by DIGITAL or its affiliated companies. The specifications and drawings, herein, are the property of Digital Equipment Corporation and shall not be reproduced or copied or used in whole or in part as the basis for the manufacture or sale of items without written permission. Copyright © 1984 by Digital Equipment Corporation. All Rights Reserved The following are trademarks of Digital Equipment Corporation: CTI BUS MASSBUS RSTS DEC PDP RSX DECmate P/OS Tool Kit DECsystem-10 PRO/BASIC UNIBUS DECSYSTEM-20 Professional VAX DECUS PRO/FMS VMS DECwriter PRO/RMS VT DIBOL PROSE Work Processor mamDOma Rainbow CONTENTS Page PREFACE ............................................................................................. v INTRODUCTION ...................................................................... Introduction-1 CHAPTER 1 COMMUNICATING WITH YOUR COMPUTER ........................ 1-1 CHAPTER 2 HOW DATA IS STORED ..................................................... 2-1 Accessing Stored Data............................................................. 2-2 CHAPTER 3 HOW DATA IS PROCESSED ............................................... 3-1 The Basic Data Processing Cycle............................................. -

HP Powerpoint 2000 Dark Template

OpenVMS Strategy and Futures OpenVMS Division, Hewlett-Packard © 2006 Hewlett-Packard Development Company, L.P. The information contained herein is subject to change without notice Agenda • OpenVMS Today • OpenVMS Tomorrow • Integrity Update • Summary 2 20 October 2007 OpenVMS Today 3 20 October 2007 The OpenVMS Mission Statement The OpenVMS Division is committed to delivering the OpenVMS roadmaps on time and with outstanding quality. The capabilities that customers have come to rely on in OpenVMS - leadership clustering, high availability, excellent quality, exceptional security and “bullet-proof” operations - will continue to be delivered and enhanced by HP, ensuring product leadership now and in the future. 4 20 October 2007 OpenVMS Celebrating 29 years across 3 computer architectures • Differentiating product • Some key Customers attributes Vodafone Toys R Us − Availability: Disaster Tolerance Deutsche Borse Renault − Clustering: Scalable to 96 nodes, Ikea USPS up to 500 miles apart Verizon Wireless Fraport USAF Commerzbank − Security: System and Cluster Mayo Foundation Intel − Best TCO in class Indian Railways PKE − Strong Integration technology Korean Exchange HKJC Veterans Association Volvo • Core Markets • Market Profile − Finance: Capital Markets, Retail − #1 rated in Healthcare Banking, Wholesale Banking, − 90% of manufacturing of the world’s CPU − Telecommunications: Mobile chips Billing, SMS, Prepaid, HLR, Cable − 30%+ of mobile phones billed in the world & Satellite TV − Over 50% of the world’s SMS transactions − Healthcare: -

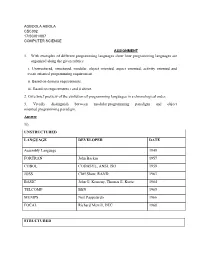

1. with Examples of Different Programming Languages Show How Programming Languages Are Organized Along the Given Rubrics: I

AGBOOLA ABIOLA CSC302 17/SCI01/007 COMPUTER SCIENCE ASSIGNMENT 1. With examples of different programming languages show how programming languages are organized along the given rubrics: i. Unstructured, structured, modular, object oriented, aspect oriented, activity oriented and event oriented programming requirement. ii. Based on domain requirements. iii. Based on requirements i and ii above. 2. Give brief preview of the evolution of programming languages in a chronological order. 3. Vividly distinguish between modular programming paradigm and object oriented programming paradigm. Answer 1i). UNSTRUCTURED LANGUAGE DEVELOPER DATE Assembly Language 1949 FORTRAN John Backus 1957 COBOL CODASYL, ANSI, ISO 1959 JOSS Cliff Shaw, RAND 1963 BASIC John G. Kemeny, Thomas E. Kurtz 1964 TELCOMP BBN 1965 MUMPS Neil Pappalardo 1966 FOCAL Richard Merrill, DEC 1968 STRUCTURED LANGUAGE DEVELOPER DATE ALGOL 58 Friedrich L. Bauer, and co. 1958 ALGOL 60 Backus, Bauer and co. 1960 ABC CWI 1980 Ada United States Department of Defence 1980 Accent R NIS 1980 Action! Optimized Systems Software 1983 Alef Phil Winterbottom 1992 DASL Sun Micro-systems Laboratories 1999-2003 MODULAR LANGUAGE DEVELOPER DATE ALGOL W Niklaus Wirth, Tony Hoare 1966 APL Larry Breed, Dick Lathwell and co. 1966 ALGOL 68 A. Van Wijngaarden and co. 1968 AMOS BASIC FranÇois Lionet anConstantin Stiropoulos 1990 Alice ML Saarland University 2000 Agda Ulf Norell;Catarina coquand(1.0) 2007 Arc Paul Graham, Robert Morris and co. 2008 Bosque Mark Marron 2019 OBJECT-ORIENTED LANGUAGE DEVELOPER DATE C* Thinking Machine 1987 Actor Charles Duff 1988 Aldor Thomas J. Watson Research Center 1990 Amiga E Wouter van Oortmerssen 1993 Action Script Macromedia 1998 BeanShell JCP 1999 AngelScript Andreas Jönsson 2003 Boo Rodrigo B. -

The Rise and Fall of Digital Equipment Corporation

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by Digital Commons @ Assumption College Digital Commons @ Assumption University Management, Marketing, and Organizational Management, Marketing, and Organizational Communication Department Faculty Works Communication Department 2019 Technology Change or Resistance to Changing Institutional Logics: The Rise and Fall of Digital Equipment Corporation Michael S. Lewis Assumption College, [email protected] Follow this and additional works at: https://digitalcommons.assumption.edu/business-faculty Part of the Business Commons Recommended Citation Lewis, M. S. (2019). Technology Change or Resistance to Changing Institutional Logics: The Rise and Fall of Digital Equipment Corporation. The Journal of Applied Behavioral Science . https://doi.org/10.1177/ 0021886318822305 This Article is brought to you for free and open access by the Management, Marketing, and Organizational Communication Department at Digital Commons @ Assumption University. It has been accepted for inclusion in Management, Marketing, and Organizational Communication Department Faculty Works by an authorized administrator of Digital Commons @ Assumption University. For more information, please contact [email protected]. 1 Technology Change or Resistance to Changing Institutional Logics: The Rise and Fall of Digital Equipment Corporation Michael S. Lewis Assistant Professor of Management Assumption College 500 Salisbury Street Worcester, MA 01609-1296 Telephone: 508-767-7372 Fax: 508-767-7252 [email protected] Abstract This article uses an institutional lens to analyze organizational failure. It does this through a historical case study of Digital Equipment Corporation, an innovator and market leader of minicomputers who faltered and eventually failed during the period of technological change brought on by the emergence of the personal computer. -

Declaser 2200 Printer Installation Guide

DEClaser 2200 Printer Installation Guide EK–D2200–IN–001 Digital Equipment Corporation Maynard, Massachusetts First Printing, June 1990 The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document. Any software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies. Restricted Rights: Use, duplication, or disclosure by the U.S. Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227–7013. © Digital Equipment Corporation 1990 All rights reserved. Printed in Japan. The Reader’s Comments form at the end of this document requests your critical evaluation to assist in preparing future documentation. The following are trademarks of Digital Equipment Corporation: BASIC Service, DECconnect, DECdirect, DEClaser, DECmailer, DECmate, DECserver, DECservice, DECstation, EDT, LN03, MicroVAX, PRO, Rainbow, VAX, VAX DOCUMENT, VAXmate, VAXstation, VAX/VMS, VMS, WPS-PLUS, VT, and the DIGITAL Logo. The following are third-party trademarks: BITSTREAM is a registered trademark of Bitstream, Inc. Centronics is a trademark of Centronics Data Computer Corporation. CG Times is a trademark of Compugraphic Corporation. CG Triumvirate is a trademark of Compugraphic Corporation. IBM is a registered trademark of International Business Machines Corporation. -

Openvms Debugger Manual

OpenVMS Debugger Manual Order Number: AA–QSBJD–TE April 2001 This manual explains the features of the OpenVMS Debugger for programmers in high-level languages and assembly language. Revision/Update Information: This manual supersedes the OpenVMS Debugger Manual, Version 7.2. Software Version: OpenVMS Alpha Version 7.3 OpenVMS VAX Version 7.3 Compaq Computer Corporation Houston, Texas © 2001 Compaq Computer Corporation Compaq, VAX, VMS, and the Compaq logo Registered in the U.S. Patent and Trademark Office. OpenVMS is a trademark of Compaq Information Technologies Group, L.P. in the United States and other countries. Microsoft, Windows, and Windows NT are trademarks of Microsoft Corporation in the United States and other countries. Intel is a trademark of Intel Corporation in the United States and other countries. Motif, Open Software Foundation, OSF/1, and UNIX are trademarks of The Open Group in the United States and other countries. All other product names mentioned herein may be the trademarks of their respective companies. Confidential computer software. Valid license from Compaq required for possession, use, or copying. Consistent with FAR 12.211 and 12.212, Commercial Computer Software, Computer Software Documentation, and Technical Data for Commercial Items are licensed to the U.S. Government under vendor’s standard commercial license. Compaq shall not be liable for technical or editorial errors or omissions contained herein. The information in this document is provided "as is" without warranty of any kind and is subject to change without notice. The warranties for Compaq products are set forth in the express limited warranty statements accompanying such products. -

Thesis May Never Have Been Completed

UvA-DARE (Digital Academic Repository) Digital Equipment Corporation (DEC): A case study of indecision, innovation and company failure Goodwin, D.T. Publication date 2016 Document Version Final published version Link to publication Citation for published version (APA): Goodwin, D. T. (2016). Digital Equipment Corporation (DEC): A case study of indecision, innovation and company failure. General rights It is not permitted to download or to forward/distribute the text or part of it without the consent of the author(s) and/or copyright holder(s), other than for strictly personal, individual use, unless the work is under an open content license (like Creative Commons). Disclaimer/Complaints regulations If you believe that digital publication of certain material infringes any of your rights or (privacy) interests, please let the Library know, stating your reasons. In case of a legitimate complaint, the Library will make the material inaccessible and/or remove it from the website. Please Ask the Library: https://uba.uva.nl/en/contact, or a letter to: Library of the University of Amsterdam, Secretariat, Singel 425, 1012 WP Amsterdam, The Netherlands. You will be contacted as soon as possible. UvA-DARE is a service provided by the library of the University of Amsterdam (https://dare.uva.nl) Download date:26 Sep 2021 Digital Equipment Corporation (DEC) (DEC) Corporation Digital Equipment David Thomas David Goodwin Digital Equipment Corporation (DEC): A Case Study of Indecision, Innovation and Company Failure David Thomas Goodwin Digital Equipment Corporation (DEC): A Case Study of Indecision, Innovation and Company Failure David Thomas Goodwin 1 Digital Equipment Corporation (DEC): A Case Study of Indecision, Innovation and Company Failure ACADEMISCH PROEFSCHRIFT ter verkrijging van de graad van doctor aan de Universiteit van Amsterdam op gezag van de Rector Magnificus prof. -

PDP-11 Systems and Options Catalog

Systems & Options Catalog October-December 1983 The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any error that may appear in this catalog. This Product Catalog was designed, produced, and typeset by Digital's Corporate Marketing Services using an in-house text-processing system. Correspondent, DATATRIEVE, DEC, DECmate, DECnet, DECmailer, DECstart, DECword, DECword/DP, DECwriter, Digital logo, FALCON, FMS-11, lAS, Internet, LA, Letterprinter 100, Letterwriter 1 00, MICRO/PDP-11 , MICRO/J-11 , MICRO/PDP-11, MICRO/T-11, MicroPower/Pascal, PACKETNET, PDP, P/OS, Professional 325 and 350, PROVUE, Q-bus, Rainbow 100, ReGIS, RSTS, RSX, RT-11 , UNIBUS, VAX, VMS, VT are trademarks of Digital Equipment Corporation. COPYRIGH"f©1983 DIGITAL EQUIPMENT CORPORATION New Products From DIGITAL MICRO/PDP-11-the performance of a minicomputer in a compact, economical microcomputer. Now there is Micro/RSX, especially designed for use on the MICRO/PDP-11. New Packaging for PDP-11/24s and PDP-11/44s- from boxes to building blocks to complete packaged sys tems. New Q-bus Mass Storage Packaging -Adds 10MB to the MICRO/PDP-11 -Adds removable floppies to Q-bus systems Table of Contents Introduction . Overview and How to Use . ii Ordering and Configuring Information. iv Supporting Products . viii Systems . ......... · 1-1 System Selection Chart . · 1-3 Q-bus System Chart. · 1-5 MICRO/PDP-11 Computer Models & Systems. · 1-8 PDP-11 /23-PLUS Computer Models & Systems. 1-12 UNIBUS System Chart.