Semiconductor Memory Timeline Notes [JK / DL 10-25-06] – Updated DL 11.8.06

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Semiconductor Industry Social Media Review

Revealed SOCIAL SUCCESS White Paper Who’s winning the social media battle in the semiconductor industry? Issue 2, September 3, 2014 The contents of this White Paper are protected by copyright and must not be reproduced without permission © 2014 Publitek Ltd. All rights reserved Who’s winning the social media battle in the semiconductor industry? Issue 2 SOCIAL SUCCESS Who’s winning the social media battle in the semiconductor industry? Report title OVERVIEW This time, in the interest of We’ve combined quantitative balance, we have decided to and qualitative measures to This report is an update to our include these companies - Intel, reach a ranking for each original white paper from channel. Cross-channel ranking Samsung, Sony, Toshiba, Nvidia led us to the overall index. September 2013. - as well as others, to again analyse the following channels: As before, we took a company’s Last time, we took the top individual “number semiconductor companies 1. Blogs score” (quantitative measure) (according to gross turnover - 2. Facebook for a channel, and multiplied main source: Wikipedia), of this by its “good practice score” 3. Google+ which five were ruled out due (qualitative measure). 4. LinkedIn to the diversity of their offering 5. Twitter The companies were ranked by and the difficulty of segmenting performance in each channel. 6. YouTube activity relating to An average was then taken of semiconductors. ! their positions in each to create the final table. !2 Who’s winning the social media battle in the semiconductor industry? Issue 2 Due to the instantaneous nature of social media, this time we decided to analyse a narrower time frame, and picked a single month - August 2014. -

IEEE Spectrum: 25 Microchip

IEEE Spectrum: 25 Microchips That Shook the World http://www.spectrum.ieee.org/print/8747 Sponsored By Select Font Size: A A A 25 Microchips That Shook the World By Brian R. Santo This is part of IEEE Spectrum 's Special Report: 25 Microchips That Shook the World . In microchip design, as in life, small things sometimes add up to big things. Dream up a clever microcircuit, get it sculpted in a sliver of silicon, and your little creation may unleash a technological revolution. It happened with the Intel 8088 microprocessor. And the Mostek MK4096 4-kilobit DRAM. And the Texas Instruments TMS32010 digital signal processor. Among the many great chips that have emerged from fabs during the half-century reign of the integrated circuit, a small group stands out. Their designs proved so cutting-edge, so out of the box, so ahead of their time, that we are left groping for more technology clichés to describe them. Suffice it to say that they gave us the technology that made our brief, otherwise tedious existence in this universe worth living. We’ve compiled here a list of 25 ICs that we think deserve the best spot on the mantelpiece of the house that Jack Kilby and Robert Noyce built. Some have become enduring objects of worship among the chiperati: the Signetics 555 timer, for example. Others, such as the Fairchild 741 operational amplifier, became textbook design examples. Some, like Microchip Technology’s PIC microcontrollers, have sold billions, and are still doing so. A precious few, like Toshiba’s flash memory, created whole new markets. -

Timeline of the Semiconductor Industry in South Portland

Timeline of the Semiconductor Industry in South Portland Note: Thank you to Kathy DiPhilippo, Executive Director/Curator of the South Portland Historical Society and Judith Borelli, Governmental Relations of Texas Inc. for providing some of the information for this timeline below. Fairchild Semiconductor 1962 Fairchild Semiconductor (a subsidiary of Fairchild Camera and Instrument Corp.) opened in the former Boland's auto building (present day Back in Motion) at 185 Ocean Street in June of 1962. They were there only temporarily, as the Western Avenue building was still being constructed. 1963 Fairchild Semiconductor moves to Western Avenue in February 1963. 1979 Fairchild Camera and Instrument Corp. is acquired/merged with Schlumberger, Ltd. (New York) for $363 million. 1987 Schlumberger, Ltd. sells its Fairchild Semiconductor Corp. subsidiary to National Semiconductor Corp. for $122 million. 1997 National Semiconductor sells the majority ownership interest in Fairchild Semiconductor to an investment group (made up of Fairchild managers, including Kirk Pond, and Citcorp Venture Capital Ltd.) for $550 million. Added Corporate Campus on Running Hill Road. 1999 In an initial public offering in August 1999, Fairchild Semiconductor International, Inc. becomes a publicly traded corporation on the New York Stock Exchange. 2016 Fairchild Semiconductor International, Inc. is acquired by ON Semiconductor for $2.4 billion. National Semiconductor 1987 National Semiconductor acquires Fairchild Semiconductor Corp. from Schlumberger, Ltd. for $122 million. 1995 National Semiconductor breaks ground on new 200mm factory in December 1995. 1996 National Semiconductor announces plans for a $600 million expansion of its facilities in South Portland; construction of a new wafer fabrication plant begins. 1997 Plant construction for 200mm factory completed and production starts. -

The Rise of the Flash Memory Market: Its Impact on Firm

The Rise of the Flash Web version: Memory Market: Its Impact July 2007 on Firm Behavior and Author: Global Semiconductor Falan Yinug1 Trade Patterns Abstract This article addresses three questions about the flash memory market. First, will the growth of the flash memory market be a short- or long-term phenomenon? Second, will the growth of the flash memory market prompt changes in firm behavior and industry structure? Third, what are the implications for global semiconductor trade patterns of flash memory market growth? The analysis concludes that flash memory market growth is a long-term phenomenon to which producers have responded in four distinct ways. It also concludes that the rise in flash memory demand has intensified current semiconductor trade patterns but has not shifted them fundamentally. 1 Falan Yinug ([email protected]) is a International Trade Analyst from the Office of Industries. His words are strictly his own and do not represent the opinions of the US International Trade Commission or of any of its Commissioners. 1 Introduction The past few years have witnessed rapid growth in a particular segment of the 2 semiconductor market known as flash memory. In each of the past five years, for example, flash memory market growth has either outpaced or equaled that 3 of the total integrated circuit (IC) market (McClean et al 2004-2007, section 5). One observer expects flash memory to have the third-strongest market growth rate over the next six years among all IC product categories (McClean et al 2007, 5-6). As a result, the flash memory share of the total IC market has increased from 5.5 percent in 2002, to 8.1 percent in 2005. -

MOSTEK 1980 CIRCUITS and SYSTEMS PRODUCT GUIDE Mostek Reserves the Right to Make Changes in Specifications at Any Time and Without Notice

MOSTEK 1980 CIRCUITS AND SYSTEMS PRODUCT GUIDE Mostek reserves the right to make changes in specifications at any time and without notice. The information furnished by Mostek in this publication is believedto be accurate and reliable. However, no responsibility is assumed by Mostek for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Mostek. The "PRELIMINARY" designation on a Mostek data sheet indicates that the product is not characterized. The specifications are subject to change, are based on design goals or preliminary part evaluation, and are not guaranteed. Mostek Corporation or an authorized sales representative should be consulted for current information before using this product. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights ofthird parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Mostek. Mostek reserves the right to make changes in specifications at anytime and without notice. PRINTED IN USA April 1980 Publication Number Trade Marks Registered® STD No 01009 Copyright © 1980 Mostek Corporation (All rights reserved) II ~~~~~~~;;;;' Table of Contents '~~~~~~;;;;; Table of Contents ................................................... 111 Numerical Index ...................................................VIII Alphabetical Index . ................................................. x Mostek Profile -

Microcomputers: NQS PUBLICATIONS Introduction to Features and Uses

of Commerce Computer Science National Bureau and Technology of Standards NBS Special Publication 500-110 Microcomputers: NQS PUBLICATIONS Introduction to Features and Uses QO IGf) .U57 500-110 NATIONAL BUREAU OF STANDARDS The National Bureau of Standards' was established by an act ot Congress on March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides; (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau's technical work is per- formed by the National Measurement Laboratory, the National Engineering Laboratory, and the Institute for Computer Sciences and Technology. THE NATIONAL MEASUREMENT LABORATORY provides the national system of physical and chemical and materials measurement; coordinates the system with measurement systems of other nations and furnishes essential services leading to accurate and uniform physical and chemical measurement throughout the Nation's scientific community, industry, and commerce; conducts materials research leading to improved methods of measurement, standards, and data on the properties of materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; develops, produces, and -

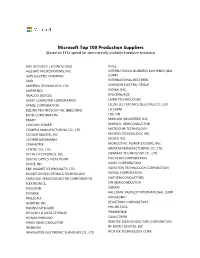

Microsoft Top 100 Production Suppliers (Based on FY14 Spend for Commercially Available Hardware Products)

Microsoft Top 100 Production Suppliers (Based on FY14 spend for commercially available hardware products) AAC ACOUSTIC TECHNOLOGIES INTEL ALLEGRO MICROSYSTEMS, INC. INTERNATIONAL BUSINESS MACHINES (IBM ALPS ELECTRIC COMPANY CORP.) AMD INTERNATIONAL RECTIFIER AMPEREX TECHNOLOGY, LTD. JOHNSON ELECTRIC GROUP AMPHENOL KIONIX, INC. ANALOG DEVICES KYOCERA/AVX ASKEY COMPUTER CORPORATION LAIRD TECHNOLOGIES ATMEL CORPORATION LELON ELECTRONICS (SUZHOU) CO., LTD BIZLINK TECHNOLOGY INC (BIZCONN) LG CHEM BOYD CORPORATION LITE-ON BRADY MARLOW INDUSTRIES, INC. CHICONY POWER MARVELL SEMICONDUCTOR COMPEQ MANUFACTURING CO., LTD. MICROCHIP TECHNOLOGY COOLER MASTER, INC. MICRON TECHNOLOGY, INC. COOPER BUSSMANN MOLEX, INC. CYMMETRIK MONOLITHIC POWER SYSTEMS, INC. CYNTEC CO., LTD. MURATA MANUFACTURING CO., LTD. DELTA ELECTRONICS, INC. NEWMAX TECHNOLOGY CO., LTD. DIGITAL OPTICS VISTA POINT NICHICON CORPORATION DIODE, INC. NIDEC CORPORATION E&E MAGNETICS PRODUCTS, LTD. NUVOTON TECHNOLOGY CORPORATION ELLINGTON ELECTRONICS TECHNOLOGY NVIDIA CORPORATION FAIRCHILD SEMICONDUCTOR CORPORATION NXP SEMICONDUCTORS FLEXTRONICS ON SEMICONDUCTOR FOXCONN OSRAM FOXLINK PALCONN, PALPILOT INTERNATIONAL CORP. FREESCALE PANASONIC GOERTEK, INC. PEGATRON CORPORATION HANNSTAR BOARD PHILIPS PLDS HITACHI-LG DATA STORAGE PRIMESENSE HONDA PRINTING QUALCOMM HYNIX SEMICONDUCTOR REALTEK SEMICONDUCTOR CORPORATION INFINEON RF MICRO DEVICES, INC. INNOVATOR ELECTRONIC SHENZHEN CO., LTD RICHTEK TECHNOLOGY CORP. ROHM CORPORATION SAMSUNG DISPLAY SAMSUNG ELECTRONICS SAMSUNG SDI SAMSUNG SEMICONDUCTOR SEAGATE SHEN ZHEN JIA AI MOTOR CO., LTD. SHENZHEN HORN AUDIO CO., LTD. SHINKO ELECTRIC INDUSTRIES CO., LTD. STARLITE PRINTER, LTD. STMICROELECTRONICS SUNG WEI SUNUNION ENVIRONMENTAL PACKAGING CO., LTD TDK TE CONNECTIVITY TEXAS INSTRUMENTS TOSHIBA TPK TOUCH SOLUTIONS, INC. UNIMICRON TECHNOLOGY CORP. UNIPLAS (SHANGHAI) CO., LTD. UNISTEEL UNIVERSAL ELECTRONICS INCORPORATED VOLEX WACOM CO., LTD. WELL SHIN TECHNOLOGY WINBOND WOLFSON MICROELECTRONICS, LTD. X-CON ELECTRONICS, LTD. YUE WAH CIRCUITS CO., LTD. -

Great Encounters That Led Me to the Invention of Flash Memory

Honda Foundation Report No. 174 Commemorative lecture at the 39th Honda Prize Award Ceremony on the 19th November 2018 Great Encounters That Led Me to the Invention of Flash Memory Dr. Fujio Masuoka Professor Emeritus, Tohoku University Representative’s Address : Dr. Koji Sakui Principal Scientist, Honda Research Institute Japan Co., Ltd. Dr. Fujio Masuoka Professor Emeritus, Tohoku University ■Date of Birth ■Major Awards Received (out of 16 awards) May 8th, 1943 1980: Invention Award, National Commendation for Invention, Japan Institute for Promoting Invention and Innovation ■Biography 1997: IEEE, The Morris N. Liebmann Memorial Award 1966: Graduated from Department of Electronic 2000: The Main Prize of Ichimura Industrial Award, the New Engineering, School of Engineering, Tohoku Technology Development Foundation University 2002: International Conference on Solid State Devices and 1971: Obtained a doctorate in engineering from Materials, SSDM Award Department of Electronic Engineering, Graduate 2005: The Economist Innovation Awards School of Engineering, Tohoku University 2007: Medal of Honor with the Purple Ribbon 1971: Joined Tokyo Shibaura Electric Co., Ltd. 2012: The Photographic Society of America (PSA), Progress Medal (currently Toshiba Corporation) 2013: USA Flash Memory Summit, Lifetime Achievement Award 1994: Resigned Toshiba Corporation and appointed as a 2013: Person of Cultural Merit professor of Graduate School of Information 2017: Orders of the Sacred Treasure, Gold and Silver Star Sciences, Tohoku University 1996: Transitioned to a professor of Research Institute Substitute Lecturer: Dr. Koji Sakui of Electrical Communication, Tohoku University 2005: Appointed as the director and chief technology Principal Scientist officer of Unisantis Electronics (Japan) Ltd. Honda Research Institute Japan Co., Ltd. 2007: Retired Tohoku University and appointed as a professor emeritus of the Tohoku University 2012: Changed the corporate name from Unisantis ■Biography Electronics (Japan) Ltd. -

A User-Oriented Family of Minicomputers

)BER 1974 iI © Copr. 1949-1998 Hewlett-Packard Co. A User-Oriented Family of Minicomputers HP's minicomputer section manager discusses the philosophy behind the design of this new computer series. by John M. Stedman WHAT DO MINICOMPUTER USERS want? In system application may require 128K words of main setting design objectives for HP's new 21 MX memory today, with the capability of expanding as Series minicomputers, we tried to make the objec additional needs arise. And it shouldn't be necessary tives conform as closely as possible to the answers to to trade off physical memory space for I/O controller this question, as we saw them. space. Minicomputer applications have broadened tre mendously in the last few years. One finds minicom puters today solving problems that only a few years Cover: The HP 21 MX Series ago would have required a large expensive computer is a family of advanced system or a dedicated system designed to solve one minicomputers featuring particular problem. In more and more cases a mini modular design, a choice of computer turns out to be the best solution to a problem. semiconductor memory systems, user-micropro- What Do Users Want? grammable processors, and In general, a minicomputer user wants the most customized instruction sets, cost-effective solution to his problem. He would like and a power system that has to have the solution as quickly as possible, and not be unusual immunity to substandard electrical con required to design special hardware to do the job. In ditions. The memory systems use the new 4K addition, he wants a solution closely matched to his RAMs, a few of which are shown here. -

Discrete Semiconductor Products Fairchild@50

Fairchild Oral History Panel: Discrete Semiconductor Products Fairchild@50 (Panel Session # 3) Participants: Jim Diller Bill Elder Uli Hegel Bill Kirkham Moderated by: George Wells Recorded: October 5, 2007 Mountain View, California CHM Reference number: X4208.2008 © 2007 Computer History Museum Fairchild Semiconductor: Discrete Products George Wells: My name's George Wells. I came to Fairchild in 1969, right in the midst of the Hogan's Heroes, shall we say, subculture, at the time. It was difficult to be in that environment as a bystander, as someone watching a play unfold. It was a difficult time, but we got through that. I came to San Rafael, Wilf asked me to get my ass up to San Rafael and turn it around or shut it down. So I was up in San Rafael for a while, and then I made my way through various different divisions, collecting about 15 of them by the time I was finished. I ended up as executive vice president, working for Wilf, and left the company about a year and a half after the Schlumberger debacle. That's it in a nutshell. Let me just turn over now to Uli Hegel, who was with Fairchild for 38 years, one of the longest serving members, I believe, in the room. Maybe the longest serving member. Uli, why don't you tell us what you did when you came, when you came and what jobs you had when you were there. Uli Hegel: I came to Fairchild in 1959, September 9, and hired into R&D as a forerunner to the preproduction days. -

Fairchild Singapore Story

The Fairchild Singapore Story 1968 - 1987 “Fairchild Singapore Pte Ltd started in 1968. In 1987, it was acquired by National Semiconductor and ceased to exist. The National Semiconductor site at Lower Delta was shutdown and operations were moved to the former Fairchild site at Lorong 3, Toa Payoh. This book is an attempt to weave the hundreds of individual stories from former Fairchild employees into a coherent whole.” 1 IMPORTANT NOTE This is a draft. The final may look significantly different. Your views are welcome on how we can do better. 2 CONTENTS WHAT THIS BOOK IS ABOUT FOREWORD ?? ACKNOWLEDGEMENTS INTRODUCTION How Fairchild Singapore Came About CHAPTER 1 The Managing Directors CHAPTER 2 Official Opening 1969 CHAPTER 3 1975: Official Opening of Factory Two CHAPTER 4 1977 - 79: Bruce’s Leadership CHAPTER 5 1979: A Schlumberger Company 3 CHAPTER 6 1986: Sold to Fujitsu CHAPTER 7 1987: Sold to National Semiconductor CHAPTER 8 Birth of the Semiconductor Industry in Singapore CHAPTER 9 Aerospace & Defence Division CHAPTER 10 Memory & High Speed Logic Division CHAPTER 11 Digital Integrated Circuit Division CHAPTER 12 Design Centre CHAPTER 13 The Ceramic Division CHAPTER 14 The Quality & Reliability Division CHAPTER 15 The Mil-Aero Division CHAPTER 16 The Standard Ceramic Division CHAPTER 17 The Plastic Leaded Chip Carrier Division 4 CHAPTER 18 Retrenchments CHAPTER 19 The Expats CHAPTER 20 Personnel Department CHAPTER 21 IT Group CHAPTER 22 Life After Fairchild APPENDICES _______________________ ?? INDEX 5 What this Book is About “Fairchild Singapore plant together with other multinational corporations in Singapore have allowed the country to move from Third World to First within one generation” ingapore’s first generation of leaders did what was good for the country. -

Fairchild Symbol Computer

Anecdotes Fairchild Symbol Computer Stanley Mazor IEEE, Sr. Member Editor: Anne Fitzpatrick In 1965, Gordon Moore of Fairchild Semiconductor As it happened, Gordon Moore’s R&D computer published what is known as Moore’s law: his observation development group wanted a practicing programmer to and prediction about the growing density of IC chips, and join their staff, so I transferred to R&D in 1966.13 Our the precursor to large-scale integration.1 Moore’s predic- project team developed a new language, Symbol, and the tions about LSI chips raised questions about how complex hardware for directly executing it. The Symbol computer chips would be designed and used.2–6 As the Fairchild overcame the data handling problems that I’d encoun- R&D director, he initiated several research projects tered with the sales order entry software. At the expense addressing the following LSI design and use issues: of extra hardware, the Symbol computer removed ‘‘artifacts’’—introduced to improve execution speed— N computer-aided design tools (CAD) for LSI chips of conventional computing languages. Undesirable N cellular logic chips using standard cells programming artifacts, for example, included static data N gate array logic chips types and type declaration. N packaging for LSI chips N semiconductor memory chips Computer design project N computer design with LSI chips One of Moore’s R&D groups, Digital Systems Research (see Figure 1) under the direction of Rex Rice, focused on As testimony to Moore’s vision, most of these Fairchild chip and system packaging. This group had developed projects subsequently spawned new industries and the original Dual In-line Package (DIP).