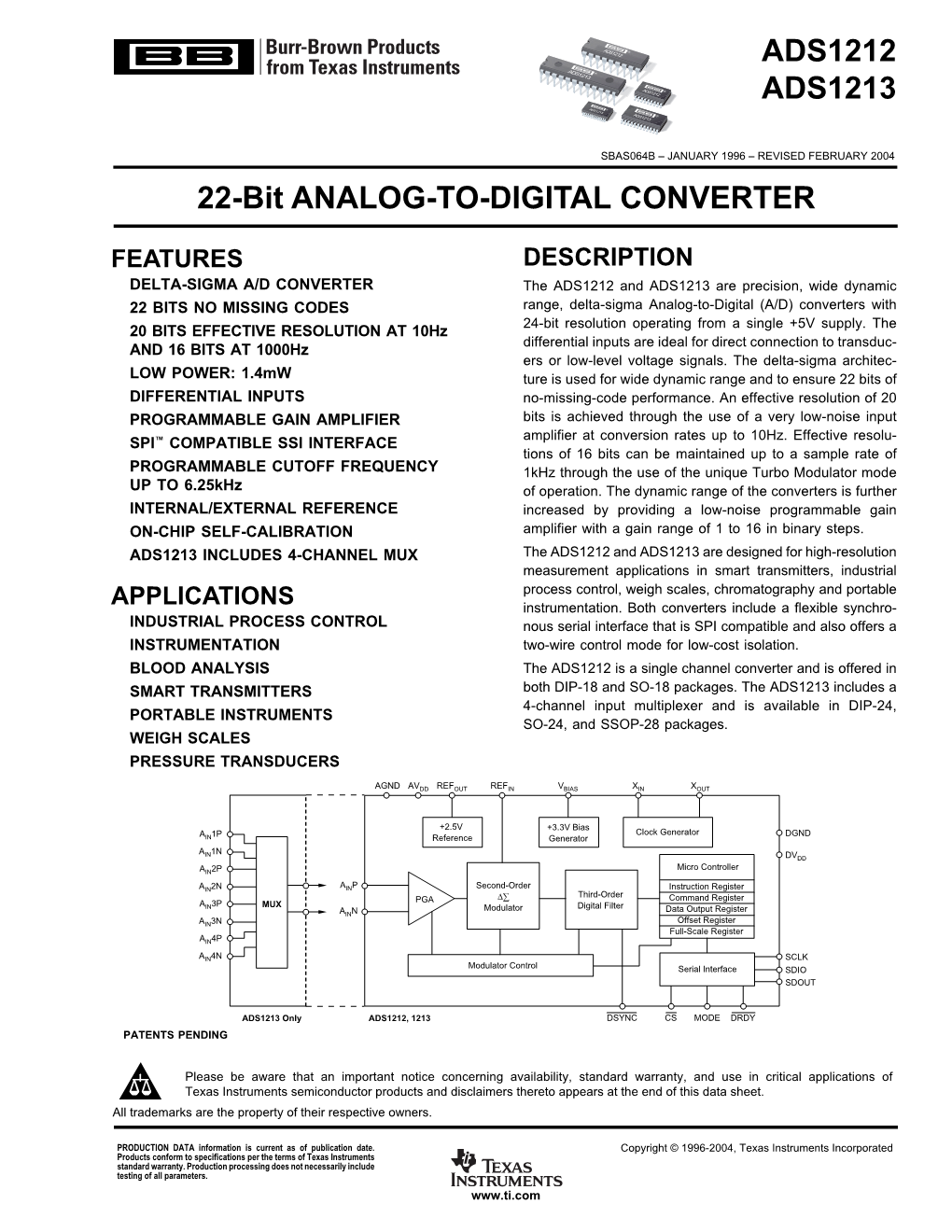

22-Bit Analog-To-Digital Converter Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Saddle Seat Division

NEW YORK STATE 4-H SADDLE SEAT DIVISION I. PERSONAL ATTIRE AND APPOINTMENTS A. Required 1. Approved protective helmet 2. Saddle suit of conservative colors or Kentucky jodhpurs with matching jacket (informal attire) 3. Day coats allowed in any class except equitation & showmanship at halter 4. Jodhpurs boots with a distinguishable heel 5. Tie 6. Shirt B. Optional 1. Gloves 2. Blunt rowelled or unrowelled spurs – must have strap 3. Whips C. Prohibited 1. Chaps 2. Rowelled spurs 3. Clip-on spurs II. TACK AND EQUIPMENT A. Required 1. Flat English type saddle 2. Full bridle or pelham, including cavesson, browband, throatlatch and appropriate curb chain 3. Triple fold leather, shaped leather or white web girth B. Optional 1. Saddle pad 2. Whips C. Prohibited 1. Chin straps or curb chains less than 1/2" in width 2. Forward seat English saddle 3. Western saddle 4. Breastplate 109 NYS 4-H Equine Show Rule Book NYS 4-H Saddle Seat Division 5. Dropped noseband 6. Kimberwicke 7. Martingale 8. Tie down 9. Protective boots 10. Draw reins, side reins, chambon, nose reins, gogue and other similar training devices. (This includes use for practice or warm-up.) 11. Bit converter D. Allowed in practice ring or warm-up 1. Running/working martingales/training forks 2. Leg wraps, splint boots 3. Bell boots III. CLASS DESCRIPTIONS Any equine (registered or grade) is eligible to compete in this division as long as all other 4-H requirements are met. Breed type is not a factor in judging. A. Saddle Seat Equitation - In equitation classes only the rider is being judged, therefore any equine that is suitable for this type of riding and which is capable of performing the required class routine is acceptable. -

NE 4-H Horse Show Bit Rules

New England 4-H Horse Show Bit Rules and Guidelines Basic guide to local, county, and state/regional 4-H Horse shows as well as for those classes in open shows limited to 4-H membership entry. This rules manual is for organizers, officials, exhibitors, parents and judges. Revised February 2020 These guidelines should be used in conjunction with the current New England 4-H Horse Show Rulebook. See rulebook for additional details involving bits and equipment for respective classes. Because the New England 4-H Horse Program is diverse in both its divisions and in the breeds that compete, it is difficult to generate a complete list of acceptable bits. Bits that are permitted by respective breed associations may be acceptable at the judge's discretion. A judge at his/her discretion can penalize a horse with non-conventional types of bits. Please understand that this supplement gives only examples of legal and u acceptable bits. In no way does it try to include every bit that is allowed or not allowed. If exhibitors have questions concerning a bit they wish to use, and that specific bit is not mentioned in the current rules or these guidelines, then exhibitors should ask the show stewards and/or the judge if the bit is acceptable for that show. Exhibitors should have alternative bits available so that they can make a change if it is determined by show officials that their preferred bit is unacceptable for that show. Each county, district or regional, and state show is officiated by different stewards and judges. -

Pennsylvania 4-H Horse Show Rule Book

Pennsylvania 4-H Horse Show Rule Book Revised 2020 Prepared by Bethany Bickel, Tammy Clark, Andrea Kocher, Amy Snover, Joe Stanco, Lew Trumble, Donna Zang, and with approval by The Pennsylvania 4-H Horse Program Development Committee and the State 4-H Office. This publication is made possible through Pennsylvania 4-H program fees. Penn State College of Agricultural Sciences research and extension programs are funded in part by Pennsylvania counties, the Commonwealth of Pennsylvania, and the U.S. Department of Agriculture. Where trade names appear, no discrimination is intended, and no endorsement by Penn State Extension is implied. Penn State encourages persons with disabilities to participate in its programs and activities. If you anticipate needing any type of accommodation or have questions about the physical access provided, please contact your local extension office in advance of your participation or visit. This publication is available in alternative media on request. The University is committed to equal access to programs, facilities, admission, and employment for all persons. It is the policy of the University to maintain an environment free of harassment and free of discrimination against any person because of age, race, color, ancestry, national origin, religion, creed, service in the uniformed services (as defined in state and federal law), veteran status, sex, sexual orientation, marital or family status, pregnancy, pregnancy-related conditions, physical or mental disability, gender, perceived gender, gender identity, genetic information or political ideas. Discriminatory conduct and harassment, as well as sexual misconduct and relationship violence, violates the dignity of individuals, impedes the realization of the University’s educational mission, and will not be tolerated. -

The Showfoto Handbook the Showfoto Handbook

The Showfoto Handbook The Showfoto Handbook 2 Contents 1 Introduction 13 1.1 Background . 13 1.1.1 About Showfoto . 13 1.1.2 Reporting Bugs . 13 1.1.3 Support . 13 1.1.4 Getting Involved . 13 1.2 Supported Image Formats . 14 1.2.1 Introduction . 14 1.2.2 Still Image Compression . 14 1.2.3 JPEG . 14 1.2.4 TIFF . 15 1.2.5 PNG . 15 1.2.6 PGF . 15 1.2.7 RAW . 15 2 The Showfoto sidebar 17 2.1 The Showfoto Right Sidebar . 17 2.1.1 Introduction to the Right Sidebar . 17 2.1.2 Properties . 17 2.1.3 Metadata . 18 2.1.3.1 EXIF Tags . 19 2.1.3.1.1 What is EXIF . 19 2.1.3.1.2 How to Use EXIF Viewer . 19 2.1.3.2 Makernote Tags . 20 2.1.3.2.1 What is Makernote . 20 2.1.3.2.2 How to Use Makernote Viewer . 20 2.1.3.3 IPTC Tags . 20 2.1.3.3.1 What is IPTC . 20 2.1.3.3.2 How to Use IPTC Viewer . 21 2.1.3.4 XMP Tags . 21 2.1.3.4.1 What is XMP . 21 2.1.3.4.2 How to Use XMP Viewer . 21 2.1.4 Colors . 21 The Showfoto Handbook 2.1.4.1 Histogram Viewer . 21 2.1.4.2 How To Use an Histogram . 23 2.1.5 Maps . 25 2.1.6 Captions . 26 2.1.6.1 Introduction . -

Friesian Division Must Be Members of IFSHA Or Pay to IFSHA a Non Member Fee for Each Competition in Which Competing

CHAPTER FR FRIESIAN AND PART BRED FRIESIAN SUBCHAPTER FR1 GENERAL QUALIFICATIONS FR101 Eligibility to Compete FR102 Falls FR103 Shoeing and Hoof Specifications FR104 Conformation for all horses SUBCHAPTER FR-2 IN-HAND FR105 Purebred Friesian FR106 Part Bred Friesian FR107 General FR108 Tack FR109 Attire FR110 Judging Criteria for In-Hand and Specialty In-Hand Classes FR111 Class Specifications for In-Hand and Specialty In-Hand classes FR112 Presentation for In-Hand Classes FR113 Get of Sire and Produce of Dam (Specialty In-Hand Classes) FR114 Friesian Baroque In-Hand FR115 Dressage and Sport Horse In-Hand FR116 Judging Criteria FR117 Class Specifications FR118 Championships SUBCHAPTER FR-3 PARK HORSE FR119 General FR120 Qualifying Gaits FR121 Tack FR122 Attire FR123 Judging Criteria SUBCHAPTER FR-4 ENGLISH PLEASURE SADDLE SEAT FR124 General FR125 Qualifying Gaits FR126 Tack FR127 Attire FR128 Judging Criteria SUBCHAPTER FR-5 COUNTRY ENGLISH PLEASURE- SADDLE SEAT FR129 General FR130 Tack FR131 Attire © USEF 2021 FR - 1 FR132 Qualifying Gaits FR133 Friesian Country English Pleasure Class Specifications SUBCHAPTER FR-6 ENGLISH PLEASURE—HUNT SEAT FR134 General FR135 Tack FR136 Attire FR137 Qualifying Gaits FR138 English Pleasure - Hunt Seat Class Specifications SUBCHAPTER FR-7 DRESSAGE FR139 General SUBCHAPTER FR-8 DRESSAGE HACK FR140 General FR141 Tack FR142 Attire FR143 Qualifying Gaits and Class Specifications SUBCHAPTER FR-9 DRESSAGE SUITABILITY FR144 General FR145 Tack FR146 Attire FR147 Qualifying Gaits and Class Specifications SUBCHAPTER -

Bit Guidelines for Use in 4-H Horse Shows

January 2020 Guidelines for Bits in Pennsylvania 4-H Horse Shows These guidelines should be used in conjunction with the current Pennsylvania 4-H Horse Show Rulebook and any available supplement. See rulebook for additional details involving bits and equipment for respective divisions and classes. Because the Pennsylvania 4-H Horse Program is diverse in both its divisions and in the breeds that compete, it is difficult to generate a complete list of acceptable bits. Bits that are permitted by respective breed associations may be acceptable at the judge’s discretion. A judge at his/her discretion can penalize a horse with non-conventional types of bits, nose bands or other equipment. If exhibitors have questions concerning a bit they wish to use, and that specific bit is not mentioned in the current rules or these guidelines, then exhibitors should ask the show stewards and/or the judge if the bit is acceptable for that show. Exhibitors should have alternative bits available so that they can make a change if it is determined by show officials that their preferred bit is unacceptable for that show. Each county, district or regional, and state show is officiated by different stewards and judges. Therefore, exhibitors must seek approval from show officials at each show before using the questionable bit. Members should consult with professionals in their riding discipline or contact the appropriate breed association for guidance in selecting a bit in order to find one that is both appropriate and acceptable for use in Pennsylvania 4-H shows. No horse or pony may be shown with their tongues tied down or with their mouths tied shut. -

Guidelines for Bits in New England 4-H Horse Shows (PDF)

These guidelines should be used in conjunction with the current New England 4-H Horse Show Rulebook. See rulebook for additional details involving bits and equipment for respective classes. Because the New England 4-H Horse Program is diverse in both its divisions and in the breeds that compete, it is difficult to generate a complete list of acceptable bits. Bits that are permitted by respective breed associations may be acceptable at the judge's discretion. A judge at his/her discretion can penalize a horse with non-conventional types of bits. Please understand that this supplement gives only examples of legal and u acceptable bits. In no way does it try to include every bit that is allowed or not allowed. If exhibitors have questions concerning a bit they wish to use, and that specific bit is not mentioned in the current rules or these guidelines, then exhibitors should ask the show stewards and/or the judge if the bit is acceptable for that show. Exhibitors should have alternative bits available so that they can make a change if it is determined by show officials that their preferred bit is unacceptable for that show. Each county, district or regional, and state show is officiated by different stewards and judges. Therefore, exhibitors must seek approval from show officials at each show before using the questionable bit. Members should consult with professionals in their riding discipline or contact the appropriate breed association for guidance in selecting a bit in order to find one that is both appropriate and acceptable for use in New England 4-H shows. -

New England 4-H Horse Show Rules and Guidelines

New England 4-H Horse Show Rules and Guidelines Basic guide to local, county, and state/regional 4-H Horse shows as well as for those classes in open shows limited to 4-H membership entry. This rules manual is for organizers, officials, exhibitors, parents and judges. Revised April 2016 All revisions of the New England 4-H Horse Show Rules and Guidelines Book is recommended by the Judges School/Rulebook subcommittee and then voted on by the full voting members of the New England 4-H Horse Program Committee. Membership may be found with the New England Co-operative Extension/4-H Offices, contact your local county extension office. If you are a person who will need an accommodation to participate please contact the event manager to discuss your needs. Requests for accommodations must be received 4 weeks prior to the event. Be it known that all updates are marked and to the best of our ability all spelling and grammar has been corrected. This does not discount however that some instances of omission may have occurred. If you note any item you feel is incorrectly entered please contact the state 4-H person in your location and have them contact us via email so that we can make a note for the next round of editing for this rulebook which will be in 2018. Original document prepared by: Cheryl LeFebvre, Secretary Robert Bartlett, Work study Student University of Vermont State 4-H Office Revisions 2009 Mary Fay, Administrative Assistant UVM Extension Revisions 2010 Sherri Thornton, Committee Chair Revisions 2011 NE Rulebook Committee Revisions -

Washington State 4-H Fair

WASHINGTON STATE 4-H FAIR WESTERN PERFORMANCE TACK CHECK Saddle – Standard Western saddle with horn If back cinch is used, must be attached to front cinch with connecting strap and adjusted close to horse If cinch has cinch pin, must be in latigo holes or removed No tapaderos (stirrup covers) Saddle Pad or Blanket or both Bridle – Any western bridle—includes bridles with throatlatches and split ear bridles Bit – snaffle or curb (maximum shank length 8 ½ inches) Curb strap – plain leather or chain, at least ½‖ wide and lie flat against jaw Split or romal reins Cavesson or noseband not allowed Optional Equipment Breast collar Spurs if worn—must be western Hobbles Lariet or riata Examples of tack NOT allowed: Mechanical Hackamore Double wire snaffle Draw reins Slip or gag bits Rolled leather chin straps Side Pull Tie Down Martingale Splint boots, bell boots, bandages, etc. SADDLESEAT PERFORMANCE TACK CHECK Saddle – Saddleseat type (may not be dressage, hunt type, all purpose or western) Bridle – Full double (curb and bridoon), Pelham or breed appropriate bit Optional: Breast Collar Saddlepad NOT ALLOWED: Martingales Tie Downs HUNTSEAT TACK CHECK Saddle –Hunt Type (may not be saddleseat type or western); All Purpose, Dressage Bridle – with cavesson Bit for hunt seat –snaffle , Pelham, kimberwick, full double, or any other English type of bit appropriate to the seat Optional: Breast Plate or Collar Saddle pad Whip or crop – may be no longer than 36‖ (48‖ for dressage) NOT ALLOWED for Hunt Seat: Side Pull Bit -

NYS 4H Horse Program Equine Show Rule Book

NEW YORK STATE 4-H HORSE PROGRAM “EQUINE SHOW” RULE BOOK Last Updated 2017 This rule book is prepared by the Cornell Cooperative Extension Office in the Department of Animal Science, 126 Morrison Hall, Cornell University, Ithaca, NY 14853 2 NYS 4-H Equine Show Rule Book TABLE OF CONTENTS Page I. INTRODUCTION NYS Equine Event Memo (s) and Policy 5 NYS 4-H General Equine Show Rules 11 II. SHOW DIVISION RULES Cross Divisional Classes Showmanship at Halter 19 Trail 29 Command 33 Costume 35 Western 37 Western Dressage 53 Gymkhana 67 Hunt Seat 79 Saddle Seat 89 Dressage 97 Driving 113 Miniature Equine 125 Drill and Parade 131 Draft Horse 147 Donkey/Mule 151 Mounted Games 157 Ranch Horse 171 3 NYS 4-H Equine Show Rule Book 4 NYS 4-H Equine Show Rule Book Department of Animal Science 126 Morrison Hall Ithaca, NY 14853 Telephone: 607‐255‐7712 E‐mail: [email protected] Website: http://4h.ansci.cornell.edu 2017 NYS 4-H HORSE PROGRAM A GREAT PROGRAM FOR YOUTH!!! 2016 was a GREAT year in the NYS 4-H Horse Program with FUN-FILLED educational programs that were held all year long for the youths involved!! The educational opportunities were once again this year - excellent and many!! Youths are involved in almost every county in the state through the Cornell Cooperative Extension system. Here’s to another great year in 2017! The NYS 4-H Horse Program is offered through the leadership of outstanding Extension staff in each county. *THANK YOU* to each of them for their continued support of this very valuable youth education program! The Cornell Cooperative Extension system, in every county and across the state, relies heavily on volunteers to provide these excellent educational programs. -

Circuit Design for Realization of a 16 Bit 1MS/S Successive Approximation Register Analog-To-Digital Converter

Circuit Design for Realization of a 16 bit 1MS/s Successive Approximation Register Analog-to-Digital Converter by Cody Brenneman A Thesis Submitted to the Faculty of the WORCESTER POLYTECHNIC INSTITUTE in partial fulfillment of the requirements for the Degree of Master of Science in Electrical and Computer Engineering by May 2010 APPROVED: Professor John McNeill, Major Advisor Professor Stephen Bitar Professor Andrew Klein Abstract As the use of digital systems continues to grow, there is an increasing need to con- vert analog information into the digital domain. Successive Approximation Register (SAR) analog-to-digital converters are used extensively in this regard due to their high resolution, small die area, and moderate conversion speeds. However, capacitor mismatch within the SAR converter is a limiting factor in its accuracy and resolution. Without some form of calibration, a SAR converter can only reasonably achieve an accuracy of 10 bits. The Split-ADC technique is a digital, deterministic, background self-calibration algorithm that can be applied to the SAR converter. This thesis describes the circuit design and physical implementation of a novel 16-bit 1MS/s SAR analog-to-digital converter for use with the Split-ADC calibration algorithm. The system was designed using the Jazz 0:18µm CMOS process, successfully operates at 1MS/s, and consumes a die area of 1:2mm2. The calibration algorithm was applied, showing an improvement in the overall accuracy of the converter. iii Acknowledgements It has been a great honor to work under Professor McNeill for the past three years. He has simultaneously helped me progress greatly in my knowledge of analog circuit design, while helping me realize how little I yet actually know. -

Al Andalusian/Lusitano Division

CHAPTER AL ANDALUSIAN/LUSITANO DIVISION SUBCHAPTER AL-1 GENERAL QUALIFICATIONS AL 100 General AL101 Eligibility to Compete AL102 Breed Standards AL103 Shoeing SUBCHAPTER AL-2 HALTER CLASSES AL104 General AL105 Conduct and Specifications AL106 Championships AL107 Get of Sire and Produce of Dam AL108 Gold Medal Movement Award AL109 Cobra of Mares SUBCHAPTER AL-3 PERFORMANCE CLASSES AL110 General SUBCHAPTER AL-4 BEST MOVEMENT AL111 General AL112 Appointments AL113 Qualifying Gaits AL114 Best Movement Class Specifications SUBCHAPTER AL-5 ENGLISH PLEASURE – FORMAL SADDLE HORSE AL115 General AL116 Appointments AL117 Qualifying Gaits AL118 English Pleasure Formal Saddle Horse Class Specifications SUBCHAPTER AL-6 ENGLISH PLEASURE - SADDLE SEAT HORSE AL119 General AL120 Appointments AL121 Qualifying Gaits AL122 English Pleasure – Saddle Seat Class Specifications SUBCHAPTER AL-7 ENGLISH PLEASURE COUNTRY AL123 General AL124 Appointments AL125 Qualifying Gaits AL126 English Pleasure Country Class Specifications SUBCHAPTER AL-8 ENGLISH PLEASURE – HUNT SEAT AL127 General AL128 Appointments © USEF 2021 AL - 1 AL129 Qualifying Gaits AL130 English Pleasure –Hunt Seat Class Specifications SUBCHAPTER AL-9 ENGLISH PLEASURE – DRESSAGE SUITABILITY AL131 General AL132 Appointments AL133 Qualifying Gaits AL134 Dressage Suitability Class Specifications Subchapter AL -10 DRESSAGE HACK AL135 General AL136 Appointments AL137 Qualifying Gaits AL138 Dressage Hack Class Specifications Subchapter AL - 11 English Pleasure-Pro Am AL139 General AL140 Appointments AL141