Chapter 2 Fundamentals of Sampled Data Systems

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Mathematical Basics of Bandlimited Sampling and Aliasing

Signal Processing Mathematical basics of bandlimited sampling and aliasing Modern applications often require that we sample analog signals, convert them to digital form, perform operations on them, and reconstruct them as analog signals. The important question is how to sample and reconstruct an analog signal while preserving the full information of the original. By Vladimir Vitchev o begin, we are concerned exclusively The limits of integration for Equation 5 T about bandlimited signals. The reasons are specified only for one period. That isn’t a are both mathematical and physical, as we problem when dealing with the delta func- discuss later. A signal is said to be band- Furthermore, note that the asterisk in Equa- tion, but to give rigor to the above expres- limited if the amplitude of its spectrum goes tion 3 denotes convolution, not multiplica- sions, note that substitutions can be made: to zero for all frequencies beyond some thresh- tion. Since we know the spectrum of the The integral can be replaced with a Fourier old called the cutoff frequency. For one such original signal G(f), we need find only the integral from minus infinity to infinity, and signal (g(t) in Figure 1), the spectrum is zero Fourier transform of the train of impulses. To the periodic train of delta functions can be for frequencies above a. In that case, the do so we recognize that the train of impulses replaced with a single delta function, which is value a is also the bandwidth (BW) for this is a periodic function and can, therefore, be the basis for the periodic signal. -

Efficient Supersampling Antialiasing for High-Performance Architectures

Efficient Supersampling Antialiasing for High-Performance Architectures TR91-023 April, 1991 Steven Molnar The University of North Carolina at Chapel Hill Department of Computer Science CB#3175, Sitterson Hall Chapel Hill, NC 27599-3175 This work was supported by DARPA/ISTO Order No. 6090, NSF Grant No. DCI- 8601152 and IBM. UNC is an Equa.l Opportunity/Affirmative Action Institution. EFFICIENT SUPERSAMPLING ANTIALIASING FOR HIGH PERFORMANCE ARCHITECTURES Steven Molnar Department of Computer Science University of North Carolina Chapel Hill, NC 27599-3175 Abstract Techniques are presented for increasing the efficiency of supersampling antialiasing in high-performance graphics architectures. The traditional approach is to sample each pixel with multiple, regularly spaced or jittered samples, and to blend the sample values into a final value using a weighted average [FUCH85][DEER88][MAMM89][HAEB90]. This paper describes a new type of antialiasing kernel that is optimized for the constraints of hardware systems and produces higher quality images with fewer sample points than traditional methods. The central idea is to compute a Poisson-disk distribution of sample points for a small region of the screen (typically pixel-sized, or the size of a few pixels). Sample points are then assigned to pixels so that the density of samples points (rather than weights) for each pixel approximates a Gaussian (or other) reconstruction filter as closely as possible. The result is a supersampling kernel that implements importance sampling with Poisson-disk-distributed samples. The method incurs no additional run-time expense over standard weighted-average supersampling methods, supports successive-refinement, and can be implemented on any high-performance system that point samples accurately and has sufficient frame-buffer storage for two color buffers. -

Digital Signals

Technical Information Digital Signals 1 1 bit t Part 1 Fundamentals Technical Information Part 1: Fundamentals Part 2: Self-operated Regulators Part 3: Control Valves Part 4: Communication Part 5: Building Automation Part 6: Process Automation Should you have any further questions or suggestions, please do not hesitate to contact us: SAMSON AG Phone (+49 69) 4 00 94 67 V74 / Schulung Telefax (+49 69) 4 00 97 16 Weismüllerstraße 3 E-Mail: [email protected] D-60314 Frankfurt Internet: http://www.samson.de Part 1 ⋅ L150EN Digital Signals Range of values and discretization . 5 Bits and bytes in hexadecimal notation. 7 Digital encoding of information. 8 Advantages of digital signal processing . 10 High interference immunity. 10 Short-time and permanent storage . 11 Flexible processing . 11 Various transmission options . 11 Transmission of digital signals . 12 Bit-parallel transmission. 12 Bit-serial transmission . 12 Appendix A1: Additional Literature. 14 99/12 ⋅ SAMSON AG CONTENTS 3 Fundamentals ⋅ Digital Signals V74/ DKE ⋅ SAMSON AG 4 Part 1 ⋅ L150EN Digital Signals In electronic signal and information processing and transmission, digital technology is increasingly being used because, in various applications, digi- tal signal transmission has many advantages over analog signal transmis- sion. Numerous and very successful applications of digital technology include the continuously growing number of PCs, the communication net- work ISDN as well as the increasing use of digital control stations (Direct Di- gital Control: DDC). Unlike analog technology which uses continuous signals, digital technology continuous or encodes the information into discrete signal states (Fig. 1). When only two discrete signals states are assigned per digital signal, these signals are termed binary si- gnals. -

NTGAN: Learning Blind Image Denoising Without Clean Reference

RUI ZHAO, DANIEL P.K. LUN, KIN-MAN LAM: NTGAN 1 NTGAN: Learning Blind Image Denoising without Clean Reference Rui Zhao Department of Electronic and [email protected] Information Engineering, Daniel P.K. Lun The Hong Kong Polytechnic University, [email protected] Hong Kong, China Kin-Man Lam [email protected] Abstract Recent studies on learning-based image denoising have achieved promising perfor- mance on various noise reduction tasks. Most of these deep denoisers are trained ei- ther under the supervision of clean references, or unsupervised on synthetic noise. The assumption with the synthetic noise leads to poor generalization when facing real pho- tographs. To address this issue, we propose a novel deep unsupervised image-denoising method by regarding the noise reduction task as a special case of the noise transference task. Learning noise transference enables the network to acquire the denoising ability by only observing the corrupted samples. The results on real-world denoising benchmarks demonstrate that our proposed method achieves state-of-the-art performance on remov- ing realistic noises, making it a potential solution to practical noise reduction problems. 1 Introduction Convolutional neural networks (CNNs) have been widely studied over the past decade in various computer vision applications, including image classification [13], object detection [29], and image restoration [35]. In spite of high effectiveness, CNN models always require a large-scale dataset with reliable reference for training. However, in terms of low-level vision tasks, such as image denoising and image super-resolution, the reliable reference data is generally hard to access, which makes these tasks more challenging and difficult. -

High-Quality Self-Supervised Deep Image Denoising

High-Quality Self-Supervised Deep Image Denoising Samuli Laine Tero Karras Jaakko Lehtinen Timo Aila NVIDIA∗ NVIDIA NVIDIA, Aalto University NVIDIA Abstract We describe a novel method for training high-quality image denoising models based on unorganized collections of corrupted images. The training does not need access to clean reference images, or explicit pairs of corrupted images, and can thus be applied in situations where such data is unacceptably expensive or im- possible to acquire. We build on a recent technique that removes the need for reference data by employing networks with a “blind spot” in the receptive field, and significantly improve two key aspects: image quality and training efficiency. Our result quality is on par with state-of-the-art neural network denoisers in the case of i.i.d. additive Gaussian noise, and not far behind with Poisson and impulse noise. We also successfully handle cases where parameters of the noise model are variable and/or unknown in both training and evaluation data. 1 Introduction Denoising, the removal of noise from images, is a major application of deep learning. Several architectures have been proposed for general-purpose image restoration tasks, e.g., U-Nets [23], hierarchical residual networks [20], and residual dense networks [31]. Traditionally, the models are trained in a supervised fashion with corrupted images as inputs and clean images as targets, so that the network learns to remove the corruption. Lehtinen et al. [17] introduced NOISE2NOISE training, where pairs of corrupted images are used as training data. They observe that when certain statistical conditions are met, a network faced with the impossible task of mapping corrupted images to corrupted images learns, loosely speaking, to output the “average” image. -

Super-Sampling Anti-Aliasing Analyzed

Super-sampling Anti-aliasing Analyzed Kristof Beets Dave Barron Beyond3D [email protected] Abstract - This paper examines two varieties of super-sample anti-aliasing: Rotated Grid Super- Sampling (RGSS) and Ordered Grid Super-Sampling (OGSS). RGSS employs a sub-sampling grid that is rotated around the standard horizontal and vertical offset axes used in OGSS by (typically) 20 to 30°. RGSS is seen to have one basic advantage over OGSS: More effective anti-aliasing near the horizontal and vertical axes, where the human eye can most easily detect screen aliasing (jaggies). This advantage also permits the use of fewer sub-samples to achieve approximately the same visual effect as OGSS. In addition, this paper examines the fill-rate, memory, and bandwidth usage of both anti-aliasing techniques. Super-sampling anti-aliasing is found to be a costly process that inevitably reduces graphics processing performance, typically by a substantial margin. However, anti-aliasing’s posi- tive impact on image quality is significant and is seen to be very important to an improved gaming experience and worth the performance cost. What is Aliasing? digital medium like a CD. This translates to graphics in that a sample represents a specific moment as well as a Computers have always strived to achieve a higher-level specific area. A pixel represents each area and a frame of quality in graphics, with the goal in mind of eventu- represents each moment. ally being able to create an accurate representation of reality. Of course, to achieve reality itself is impossible, At our current level of consumer technology, it simply as reality is infinitely detailed. -

Saddle Seat Division

NEW YORK STATE 4-H SADDLE SEAT DIVISION I. PERSONAL ATTIRE AND APPOINTMENTS A. Required 1. Approved protective helmet 2. Saddle suit of conservative colors or Kentucky jodhpurs with matching jacket (informal attire) 3. Day coats allowed in any class except equitation & showmanship at halter 4. Jodhpurs boots with a distinguishable heel 5. Tie 6. Shirt B. Optional 1. Gloves 2. Blunt rowelled or unrowelled spurs – must have strap 3. Whips C. Prohibited 1. Chaps 2. Rowelled spurs 3. Clip-on spurs II. TACK AND EQUIPMENT A. Required 1. Flat English type saddle 2. Full bridle or pelham, including cavesson, browband, throatlatch and appropriate curb chain 3. Triple fold leather, shaped leather or white web girth B. Optional 1. Saddle pad 2. Whips C. Prohibited 1. Chin straps or curb chains less than 1/2" in width 2. Forward seat English saddle 3. Western saddle 4. Breastplate 109 NYS 4-H Equine Show Rule Book NYS 4-H Saddle Seat Division 5. Dropped noseband 6. Kimberwicke 7. Martingale 8. Tie down 9. Protective boots 10. Draw reins, side reins, chambon, nose reins, gogue and other similar training devices. (This includes use for practice or warm-up.) 11. Bit converter D. Allowed in practice ring or warm-up 1. Running/working martingales/training forks 2. Leg wraps, splint boots 3. Bell boots III. CLASS DESCRIPTIONS Any equine (registered or grade) is eligible to compete in this division as long as all other 4-H requirements are met. Breed type is not a factor in judging. A. Saddle Seat Equitation - In equitation classes only the rider is being judged, therefore any equine that is suitable for this type of riding and which is capable of performing the required class routine is acceptable. -

Chapter 2 Data Representation in Computer Systems 2.1 Introduction

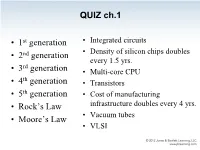

QUIZ ch.1 • 1st generation • Integrated circuits • 2nd generation • Density of silicon chips doubles every 1.5 yrs. rd • 3 generation • Multi-core CPU th • 4 generation • Transistors • 5th generation • Cost of manufacturing • Rock’s Law infrastructure doubles every 4 yrs. • Vacuum tubes • Moore’s Law • VLSI QUIZ ch.1 The highest # of transistors in a CPU commercially available today is about: • 100 million • 500 million • 1 billion • 2 billion • 2.5 billion • 5 billion QUIZ ch.1 The highest # of transistors in a CPU commercially available today is about: • 100 million • 500 million “As of 2012, the highest transistor count in a commercially available CPU is over 2.5 • 1 billion billion transistors, in Intel's 10-core Xeon • 2 billion Westmere-EX. • 2.5 billion Xilinx currently holds the "world-record" for an FPGA containing 6.8 billion transistors.” Source: Wikipedia – Transistor_count Chapter 2 Data Representation in Computer Systems 2.1 Introduction • A bit is the most basic unit of information in a computer. – It is a state of “on” or “off” in a digital circuit. – Sometimes these states are “high” or “low” voltage instead of “on” or “off..” • A byte is a group of eight bits. – A byte is the smallest possible addressable unit of computer storage. – The term, “addressable,” means that a particular byte can be retrieved according to its location in memory. 5 2.1 Introduction A word is a contiguous group of bytes. – Words can be any number of bits or bytes. – Word sizes of 16, 32, or 64 bits are most common. – Intel: 16 bits = 1 word, 32 bits = double word, 64 bits = quad word – In a word-addressable system, a word is the smallest addressable unit of storage. -

Learning Deep Image Priors for Blind Image Denoising

Learning Deep Image Priors for Blind Image Denoising Xianxu Hou 1 Hongming Luo 1 Jingxin Liu 1 Bolei Xu 1 Ke Sun 2 Yuanhao Gong 1 Bozhi Liu 1 Guoping Qiu 1,3 1 College of Information Engineering and Guangdong Key Lab for Intelligent Information Processing, Shenzhen University, China 2 School of Computer Science, The University of Nottingham Ningbo China 3 School of Computer Science, The University of Nottingham, UK Abstract ods comes from the effective image prior modeling over the input images [5, 14, 20]. State of the art model-based meth- Image denoising is the process of removing noise from ods such as BM3D [12] and WNNM [20] can be further noisy images, which is an image domain transferring task, extended to remove unknown noises. However, there are a i.e., from a single or several noise level domains to a photo- few drawbacks of these methods. First, these methods usu- realistic domain. In this paper, we propose an effective im- ally involve a complex and time-consuming optimization age denoising method by learning two image priors from process in the testing stage. Second, the image priors em- the perspective of domain alignment. We tackle the domain ployed in most of these approaches are hand-crafted, such alignment on two levels. 1) the feature-level prior is to learn as nonlocal self-similarity and gradients, which are mainly domain-invariant features for corrupted images with differ- based on the internal information of the input image without ent level noise; 2) the pixel-level prior is used to push the any external information. -

Efficient Multidimensional Sampling

EUROGRAPHICS 2002 / G. Drettakis and H.-P. Seidel Volume 21 (2002 ), Number 3 (Guest Editors) Efficient Multidimensional Sampling Thomas Kollig and Alexander Keller Department of Computer Science, Kaiserslautern University, Germany Abstract Image synthesis often requires the Monte Carlo estimation of integrals. Based on a generalized con- cept of stratification we present an efficient sampling scheme that consistently outperforms previous techniques. This is achieved by assembling sampling patterns that are stratified in the sense of jittered sampling and N-rooks sampling at the same time. The faster convergence and improved anti-aliasing are demonstrated by numerical experiments. Categories and Subject Descriptors (according to ACM CCS): G.3 [Probability and Statistics]: Prob- abilistic Algorithms (including Monte Carlo); I.3.2 [Computer Graphics]: Picture/Image Generation; I.3.7 [Computer Graphics]: Three-Dimensional Graphics and Realism. 1. Introduction general concept of stratification than just joining jit- tered and Latin hypercube sampling. Since our sam- Many rendering tasks are given in integral form and ples are highly correlated and satisfy a minimum dis- usually the integrands are discontinuous and of high tance property, noise artifacts are attenuated much 22 dimension, too. Since the Monte Carlo method is in- more efficiently and anti-aliasing is improved. dependent of dimension and applicable to all square- integrable functions, it has proven to be a practical tool for numerical integration. It relies on the point 2. Monte Carlo Integration sampling paradigm and such on sample placement. In- The Monte Carlo method of integration estimates the creasing the uniformity of the samples is crucial for integral of a square-integrable function f over the s- the efficiency of the stochastic method and the level dimensional unit cube by of noise contained in the rendered images. -

Chapter 1 Computers and Digital Basics Computer Concepts 2014 1 Your Assignment…

Chapter 1 Computers and Digital Basics Computer Concepts 2014 1 Your assignment… Prepare an answer for your assigned question. Use Chapter 1 in the book and this PowerPoint to procure information. Prepare a PowerPoint presentation to: 1. Show your answer and additional information/facts – make sure you understand and can explain your answer. Provide as must information and detail as possible. Add graphics to enhance. 2. Where in the book did you find your information? Include the page number. 3. What more do you need to find out to help you better understand this question? Be prepared to share your information with the class. Chapter 1: Computers and Digital Basics 2 1 The Digital Revolution The digital revolution is an ongoing process of social, political, and economic change brought about by digital technology, such as computers and the Internet The technology driving the digital revolution is based on digital electronics and the idea that electrical signals can represent data, such as numbers, words, pictures, and music Chapter 1: Computers and Digital Basics 6 1 The Digital Revolution Digitization is the process of converting text, numbers, sound, photos, and video into data that can be processed by digital devices The digital revolution has evolved through four phases, beginning with big, expensive, standalone computers, and progressing to today’s digital world in which small, inexpensive digital devices are everywhere Chapter 1: Computers and Digital Basics 7 1 The Digital Revolution Chapter 1: Computers and Digital Basics -

Data Representation in Computer Systems

© Jones & Bartlett Learning, LLC © Jones & Bartlett Learning, LLC NOT FOR SALE OR DISTRIBUTION NOT FOR SALE OR DISTRIBUTION There are 10 kinds of people in the world—those who understand binary and those who don’t. © Jones & Bartlett Learning, LLC © Jones—Anonymous & Bartlett Learning, LLC NOT FOR SALE OR DISTRIBUTION NOT FOR SALE OR DISTRIBUTION © Jones & Bartlett Learning, LLC © Jones & Bartlett Learning, LLC NOT FOR SALE OR DISTRIBUTION NOT FOR SALE OR DISTRIBUTION CHAPTER Data Representation © Jones & Bartlett Learning, LLC © Jones & Bartlett Learning, LLC NOT FOR SALE 2OR DISTRIBUTIONin ComputerNOT FOR Systems SALE OR DISTRIBUTION © Jones & Bartlett Learning, LLC © Jones & Bartlett Learning, LLC NOT FOR SALE OR DISTRIBUTION NOT FOR SALE OR DISTRIBUTION 2.1 INTRODUCTION he organization of any computer depends considerably on how it represents T numbers, characters, and control information. The converse is also true: Stan- © Jones & Bartlettdards Learning, and conventions LLC established over the years© Jones have determined& Bartlett certain Learning, aspects LLC of computer organization. This chapter describes the various ways in which com- NOT FOR SALE putersOR DISTRIBUTION can store and manipulate numbers andNOT characters. FOR SALE The ideas OR presented DISTRIBUTION in the following sections form the basis for understanding the organization and func- tion of all types of digital systems. The most basic unit of information in a digital computer is called a bit, which is a contraction of binary digit. In the concrete sense, a bit is nothing more than © Jones & Bartlett Learning, aLLC state of “on” or “off ” (or “high”© Jones and “low”)& Bartlett within Learning, a computer LLCcircuit. In 1964, NOT FOR SALE OR DISTRIBUTIONthe designers of the IBM System/360NOT FOR mainframe SALE OR computer DISTRIBUTION established a conven- tion of using groups of 8 bits as the basic unit of addressable computer storage.