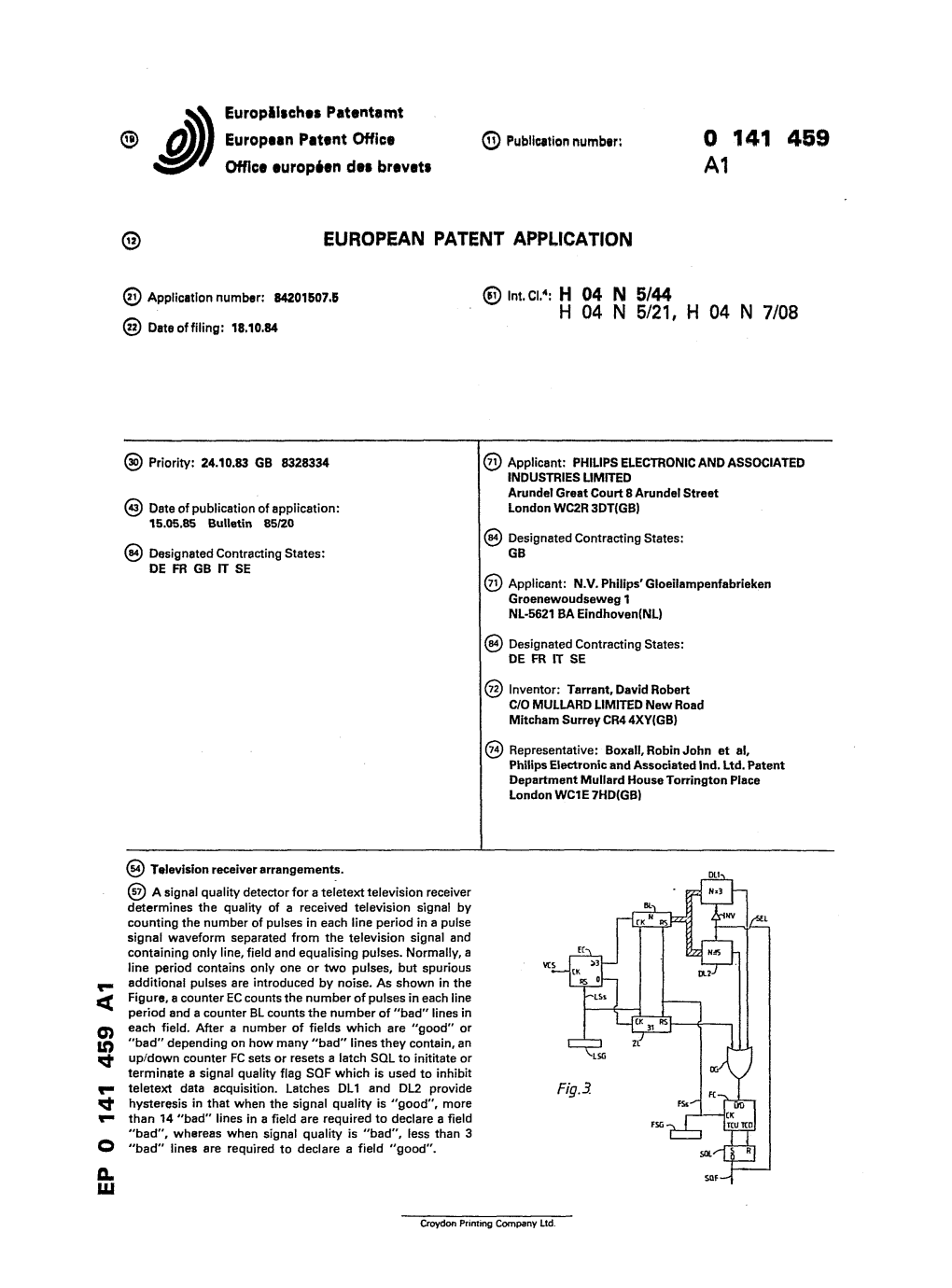

Television Receiver Arrangements

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Application of Closed Circuit Television for Traffic Surveillance in Texas

APPLICATION OF CLOSED CIRCUIT TELEVISION FOR TRAFFIC SURVEILLANCE IN TEXAS by William R. McCasland Research Engineer Texas Transportation Institute and Raymond G. Biggs Engineering Technician Texas Highway Department Research Report Number 139-11 Freeway Control and Information Systems Research Study Number 2-8-69-139 Sponsored by The Texas Highway Department In Cooperation with the U.S. Department of Transportation Federal Highway Administration TEXAS TRANSPORTATION INSTITUTE Texas A&M University College Station, Texas August 1971 ABSTRACT Closed circuit television (CCTV) has been used for surveillance of traffic and transportation facilities for many years. However, the num ber of operating systems are few bec,ause their effectiveness as a long term surveillance system has been suspect due to the inclusion of human observers in the surveillance loop. The use of CCTV for short intensive observations necessary to research and traffic studies has been success ful. The accelerating development of area wide traffic surveillance, control, and communications systems for urban areas will increase the interest in the use of CCTV as part of the surveillance system. There are four operating CCTV systems in Texas that are used for traffic sur veillance. Each system has different design and operating characteris tics. DISCLAIMER The opinions, findings, and conclusions expressed ,or implied in this report are those of the research agency and not necessarily those of the Texas Highway Department or the Federal Highway Administration. SUMMARY There are four closed circuit television systems in Texas that are designed and operated for traffic surveillance. Each system has different design and operating characteristics to satisfy the surveillance require ments. -

A~'? ~1 I0 4 THRU) (ACCESSION NUMBER)

SATELLITES PROGRAM ON APPLICATION OF COMMUNICATIONS TO EDUCATIONAL DEVELOPMENT WASHINGTON UNIVERSITY May, 1971 Report No. T-71/2 STILL-PICTURE TELEVISION (SPTV) TRANSMISSION Gulab Sharma A~'? ~1 i0 4 THRU) (ACCESSION NUMBER) O~ l _(PAGES) Z3 (NASACRORM"ORADNUMBE REPRODUCED BY- NATIONAL TECHNICAL INFORMATION SERVICE K U S DEPARTMENT OFCOMMERCE SPRINGFIELD, VA. 22161 / MISSOURI 63130 WASHINGTON UNIVCRSITY / SAINT LOUIS PROGRAM ON APPLICATION OF COMMUNICATIONS SATELLITES TO EDUCATIONAL DEVELOPMENT WASHINGTON UNIVERSITY Report No T-71/2 May, 1971 STILL-PICTURE TELEVISION (SPTV) TRANSMISSION Gulab Sharma I This research is supported by the National Aeronautics and Space Administration under Grant No Y/NGL-26-08-054 and it does not necessarily represent the views of either the research team as a whole or NASA WASHINGTON UNIVERSITY SEVER INSTITUTE OF TECHNOLOGY ABSTRACT STILL-PICTURE TELEVISION TRANSMISSION by Gulab Sharma ADVISOR: Professor D.L. Snyder June, 1971 Saint Louis, Missouri To produce a diversity of program material in a limited frequency spectrum, various multichannel, continuous-audio still-video, television transmission-systems, compatible to the existing systems, have been suggested and investigated. In this report, we categorize and describe these alternative systems and identify some of the system parameters and con straints. The issues explored are: the number of still picture channels that can be realized in a limited spectrum, the interrelation of various parameters with system con straints, and general system considerations. iii Preceding page blank TABLE OF CONTENTS No. Page 1. Introduction.....................................1 1.1 Main Objective and Scope ................... 2 1.2 Television Broadcast Standards ............. 3 1.3 System Performance Objectives .............. 4 1.4 Subjective Picture Quality ................ -

Inventing Television: Transnational Networks of Co-Operation and Rivalry, 1870-1936

Inventing Television: Transnational Networks of Co-operation and Rivalry, 1870-1936 A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy In the faculty of Life Sciences 2011 Paul Marshall Table of contents List of figures .............................................................................................................. 7 Chapter 2 .............................................................................................................. 7 Chapter 3 .............................................................................................................. 7 Chapter 4 .............................................................................................................. 8 Chapter 5 .............................................................................................................. 8 Chapter 6 .............................................................................................................. 9 List of tables ................................................................................................................ 9 Chapter 1 .............................................................................................................. 9 Chapter 2 .............................................................................................................. 9 Chapter 6 .............................................................................................................. 9 Abstract .................................................................................................................... -

Municipal Ripoff: the Unconstitutionality of Cable Television Franchise Fees and Access Support Payments

Catholic University Law Review Volume 35 Issue 3 Spring 1986 Article 3 1986 Municipal Ripoff: The Unconstitutionality of Cable Television Franchise Fees and Access Support Payments David J. Saylor Follow this and additional works at: https://scholarship.law.edu/lawreview Recommended Citation David J. Saylor, Municipal Ripoff: The Unconstitutionality of Cable Television Franchise Fees and Access Support Payments, 35 Cath. U. L. Rev. 671 (1986). Available at: https://scholarship.law.edu/lawreview/vol35/iss3/3 This Comments is brought to you for free and open access by CUA Law Scholarship Repository. It has been accepted for inclusion in Catholic University Law Review by an authorized editor of CUA Law Scholarship Repository. For more information, please contact [email protected]. COMMENTARY MUNICIPAL RIPOFF: THE UNCONSTITUTIONALITY OF CABLE TELEVISION FRANCHISE FEES AND ACCESS SUPPORT PAYMENTS David J. Saylor * I. AN INTRODUCTORY PARADE OF HORRIBLES Imagine the outcry if the Federal Communications Commission (FCC) announced that henceforth all television and radio licenses would be auc- tioned off to the highest bidder for each license term. The political justifica- tion for such a development could be quite straightforward: Uncle Sam needs the money to help reduce the national debt and save government pro- grams from the clutches of Gramm-Rudman.' The purported legal ration- ale for this radical departure from current practice would be that the public, i.e., the federal government, owns the air space and is entitled to get fair market value for renting the airwaves to broadcasters. Or, consider this frightening scenario. Suppose the mayor and city coun- cil of Washington, D.C. -

Newnes Guide to Television & Video Technology.Pdf

Newnes Guide to Television and Video Technology Newnes Guide to Television and Video Technology Third edition Eugene Trundle, TMIEEIE, MRTS, MISTC OXFORD AUCKLAND BOSTON JOHANNESBURG MELBOURNE NEW DELHI Newnes An imprint of Butterworth-Heinemann Linacre House, Jordan Hill, Oxford OX2 8DP 225 Wildwood Avenue, Woburn, MA 01801-2041 A division of Reed Educational and Professional Publishing Ltd A member of the Reed Elsevier plc group First published 1988 Second edition 1996 Third edition 2001 # Eugene Trundle 1988, 1996, 2001 All rightsreserved.No part of thispublication may be reproduced in any material form (including photocopying or storing in any medium by electronic means and whether or not transiently or incidentally to some other use of this publication) without the written permission of the copyright holder except in accordance with the provisions of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, England W1P 9HE. Applications for the copyright holder's written permission to reproduce any part of thispublication shouldbe addressed to the publishers. British Library Cataloguing in Publication Data A catalogue record for thisbook isavailable from the BritishLibrary. ISBN 0 7506 48104 Typset by Keyword Typesetting Services Ltd, Wallington, Surrey Printed and bound in Great Britain by MPG BooksLtd, Bodmin, Cornwall Contents Preface to third edition vii 1 Basic television 1 2 Light and colour 15 3 Reading and writing in three colours21 -

F\\.E RECEIVED

Before the OR\G\N~\.. PBDDAL COJIIIU)IZCATZOliS COJQ(ZSSZON •••hinqton, D.C. 20554 f\\.E In the Matter of ) ) Amendment of the Commission's Rules ) to Establish New Personal Communications ) Services ) File No. PP 27 ) To: The Commission ) RECEIVED SEP lO ,"', FEDERAL co"lJUNlC OFFICE OF TH~SET10NS COMMISS/(W I; CRETARY PURTBER SUPPLBKBBT TO RBQOBST POR PIOllBBR'S PREPERElICE up SIUlI OV,UTQLY REPORT Dennis R. Patrick President and Chief Executive Officer Lisa A. Hook Chief Operating Officer Time Warner Telecommunications 1776 Eye Street, N.W. Washington, D.C. 20006 (202) 331-7478 rac'd uf~--- UstA b' September 30, 1992 TABLB OF CONTBHTS SUMMARY i I. INTRODUCTION. ....................................... .. 1 II. SUMMARY OF PREVIOUS EXPERIMENTAL WORK 3 A. Fall 1991 3 B. Winter 1992 4 C. Spring 1992 5 1. Propagation Tests 5 2. Remote Antenna Systems 6 3. Digital Transport Carrier Tests 8 III. SUMMARY OF EXPERIMENTAL WORK CONDUCTED THIS QUARTER ... 10 A. Propagation Tests 10 1. Time Delay Measurements 10 2. Path Loss Measurements 12 B. PCS/Cable Integration Studies 13 1. Remote Antenna Tests 14 2. Tests of Digital Transport Carrier Circuits. 16 a. 1850 MHz Demonstration 17 b. First Pacific Network System Integration 18 c. Wireless Office Experiments 19 IV. CONCLUSIONS........................................... 21 Summary Time Warner Telecommunications, a division of Time Warner Entertainment, L.P. has been an industry leader ln defining Personal Communications Services ("PCS"), in working with the Executive Branch and Congress on the exciting possibilities for PCS in the U.S., and in defining the technologies critical to the launch of our domestic PCS industry. -

Channel Allocation Into a (Analog) Spectrum of One Or More (60) Provisional Application No

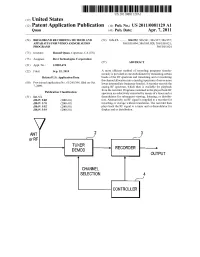

US 20110081129A1 (19) United States (12) Patent Application Publication (10) Pub. No.: US 2011/0081129 A1 Quan (43) Pub. Date: Apr. 7, 2011 (54) BROADBAND RECORDING METHOD AND (52) U.S. Cl. ......... 386/252: 386/341; 386/337:386/357; APPARATUS FOR VIDEO AND/OR AUDIO 386/E05.004; 386/E05.028; 386/E05.021; PROGRAMS 386/EO5.024 (75) Inventor: Ronald Quan, Cupertino, CA (US) (73) Assignee: Rovi Technologies Corporation (57) ABSTRACT (21) Appl. No.: 12/882,474 (22) Filed: Sep.15, 2010 A more efficient method of recording programs simulta neously is provided in one embodiment by translating certain Related U.S. Application Data bands of the RF spectrum and translating and or reordering the channel allocation into a (analog) spectrum of one or more (60) Provisional application No. 61/249,394, filed on Oct. lower intermediate frequency band(s). A recorder records the 7, 2009. analog RF spectrum, which then is available for playback from the recorder. Programs contained in the played back RF Publication Classification spectrum are selectively extracted by means of a tuner and or (51) Int. Cl. demodulator for Subsequent viewing, listening, or distribu H04N 9/80 (2006.01) tion. Alternatively, an RF signal is supplied to a recorder for H04N 5/76 (2006.01) recording or storage without translation. The recorder then H04N 5/92 (2006.01) plays back the RF signal to a tuner and or demodulator for H04N 5/93 (2006.01) display and or distribution. ANT or RF RECORDER OUTPUT CHANNEL SELECTION CONTROLLER Patent Application Publication Apr. 7, 2011 Sheet 1 of 9 US 2011/0081129 A1 ANT 2 3 or RF RECORDER OUTPUT CHANNEL SELECTION CONTROLLER F.G. -

The Brighter Side of Television: Delivery of Information in the Vbi

THE BRIGHTER SIDE OF TELEVISION: DELIVERY OF INFORMATION IN THE VBI Eric Rayman and William C. Schneck* ABSTRACT information over-the-air in the vertical blanking interval ( "VBI") of the This article will attempt to describe television signal. the VBI to (and by) non-engineers, discuss some of the issues raised by the FCC's The Federal Communications rulemaking and copsider, in light of WGN Commission has authorized TV broadcast v. United Video , the effect of the stations to transmit teletext in copyr1ght laws on VBI teletext. connection with their regular television transmissions. On May 20, 1983, following over a year of public debate and comment, the FCC released a Report and Order which Television watching is undergoing established technical standards and some fundamental changes. Cable, regulator¥ policies to govern broadcast satellite distribution and home video teletext. recorders have, all had an effect on the use of the old TV set. Now a new More recently, the FCC has proposed technology, teletext, has arrived which, that television stations be permitted to while not yet fully developed, could employ their VBI's for various other data change the meaning of "watching transmission services, such as ~aging television". services, in addition to teletext. The Commission is currently considering public Teletext is a system for displaying comments on this proposal. information text and graphics on a television set in response to user TELETEXT IS INTERACTIVE, BUT NOT TWO-WAY commands. It delivers instantly access to news and sports information, entertainment First, a statement of what teletext guides, financial listings, emergency is not: it is not videotex. -

H04 Electric Communication Technique

H04B H04 ELECTRIC COMMUNICATION TECHNIQUE Note This class covers electrical communication systems with propagation paths employing beams of corpuscular radiation, acoustic waves or electromagnetic waves, e.g. radio or optical communication. [4] XXXX H04B H04B XXXX H04B TRANSMISSION (transmission systems for measured values, control or similar signals G08C; speech analysis or synthesis G10L; coding, decoding or code conversion, in general H03M; broadcast communication H04H; multiplex systems H04J; secret communication H04K; transmission of digital information H04L) [4] Note This subclass covers the transmission of information-carrying signals, the transmission being independent of the nature of the information, and includes monitoring and testing arrangements and the suppression and limitation of noise and interference. Subclass Index DETAILS...................................................................................... 1/00 SYSTEMS NOT CHARACTERISED BY THE SYSTEMS CHARACTERISED BY THE MEDIUM USED FOR TRANSMISSION ................................14/00 MEDIUM USED FOR TRANSMISSION SUPPRESSION OR LIMITATION OF NOISE Using conductors ....................................................... 3/00 OR INTERFERENCE ................................................................15/00 Using free-space propagation...................... 5/00 to 11/00 MONITORING, TESTING ........................................................17/00 Others....................................................................... 13/00 1 / 00 Details of transmission -

Newnes Guide to Television and Video Technology Newnes Guide to Television and Video Technology

Newnes Guide to Television and Video Technology Newnes Guide to Television and Video Technology Third edition Eugene Trundle, TMIEEIE, MRTS, MISTC OXFORD AUCKLAND BOSTON JOHANNESBURG MELBOURNE NEW DELHI Newnes An imprint of Butterworth-Heinemann Linacre House, Jordan Hill, Oxford OX2 8DP 225 Wildwood Avenue, Woburn, MA 01801-2041 A division of Reed Educational and Professional Publishing Ltd A member of the Reed Elsevier plc group First published 1988 Second edition 1996 Third edition 2001 # Eugene Trundle 1988, 1996, 2001 All rightsreserved.No part of thispublication may be reproduced in any material form (including photocopying or storing in any medium by electronic means and whether or not transiently or incidentally to some other use of this publication) without the written permission of the copyright holder except in accordance with the provisions of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, England W1P 9HE. Applications for the copyright holder's written permission to reproduce any part of thispublication shouldbe addressed to the publishers. British Library Cataloguing in Publication Data A catalogue record for thisbook isavailable from the BritishLibrary. ISBN 0 7506 48104 Typset by Keyword Typesetting Services Ltd, Wallington, Surrey Printed and bound in Great Britain by MPG BooksLtd, Bodmin, Cornwall Contents Preface to third edition vii 1 Basic television 1 2 Light and colour 15 3 Reading and writing in three colours21 -

United States Patent (19) 11) 4,287,530 Gay Et Al

United States Patent (19) 11) 4,287,530 Gay et al. (45) Sep. 1, 1981 54 DEMODULATOR SYSTEM INCLUDING A nance information signals from the frequency modu TUNABLE DISCRIMINATOR SUITABLE lated Secam RF subcarrier frequencies without the FOR USE IN A SECAM TELEVISION necessity for precise and stable tuned circuits. The de RECEIVER modulating system includes a single discriminator hav 75 Inventors: Michael J. Gay, Chancy; Johannes A. ing an electronically tunable center frequency, a Gutmann, Geneva, both of remodulator, for producing a reference frequency am Switzerland plitude modulated by the chrominance information (73) Assignee: Motorola Inc., Schaumburg, Ill. signals which are supplied to a commutator as known, and a feedback circuit coupled between the discrimina 21 Appl. No.: 148,347 tor and remodulator. The discriminator is selectively 22 Filed: May 9, 1980 tuned to a reference center frequency during each pic ture line clamp period to produce a zero level output 51) Int. Cl. ............................................... H04N 9/50 signal. During the chrominance information portion of I52) U.S. Cl. ...................................................... 358/23 each line, the center frequency of the discriminator is 58) Field of Search ............................. 358/23; 329/50 alternately offset by first and second control signals to 56 References Cited center frequencies coinciding with the two reference U.S. PATENT DOCUMENTS frequencies to produce a zero output level whenever the Secam signals are at the respective RF subcarrier 3,806,632 4/1974 Okada .................................... 358/23 frequencies. The feedback circuit ensures that the zero 4,232,268 ll/1980 Hinn ....................................... 358/23 output levels obtained during the information carrying Primary Examiner-Richard Murray portion of each line is identical with the zero output Attorney, Agent, or Firm-Michael D. -

Cable Television in the Commonwealth of Pennsylvania Analysis and Recommendations, November 1979

COMMONWEALTH OF PENNSYLVANIA LOCAL GOVERNMENT COMMISSION MEMBERS SENATE POST OFFICE MEMBERS MAIH CAPITOL BUILDING SENA TOR H. CRAIG LEWIS REPRESENTATIVE MARVIN D. WEIDNER FEASTERVILLE HARRISBURG, PA. 17110 TELFORD SENATOR QUENTIN R. ORLANDO 717-787-6211 REPRESENTATIVE A. CARVILLE FOSTER, JR. ERIE SEVEN VALLEYS 717-787-7680 SENATOR J. BARRY STOUT REPRESENTATIVE JOSEPH LEVI II BENTLEYVILLE OIL CITY Executive Director SENATOR JOHN STAUFFER VIRGIL F. PUSKARICH REPRESENTATIVE A. J. DeMEDIO PHOENIXVlLLE DONORA SENATOR J. DOYLE CORMAN, JR. REPRESENTATIVE LESTER K. FRYER eaLEFONTE BOYERTOWN CABLE TELEVISION IN THE COMMONWEALTH OF PENNSYLVANIA: ANALYSIS AND RECOMMENDATIONS November, 1979 The findings and recommendations in this study are a result of research conducted by the authors and do not reflect the opinions of the Members of the Local Government Commission or the Pennsylvania General Assembly. The research for this report has covered a period of approximately one year and the information presented is as current as possible in view of the constant modification in Federal regulations. The authors wish to acknowledge the assistance of the following individuals, among others, for their comments and input relative to this study -- Sharon A. Briley, Barbara Lukens, Sandra Mancuso, Elizabeth B. Green, and John P. Cleary. Special thanks to Richard E. Campbell, Director of the Legislative Data Processing Center, for his help in developing a computer program for the tabulation of questionnaires used in the survey of municipalities. Michael P. Gasbarre M~f'.l.1~~ Mark A. Zyw(lrl.J TABLE OF CONTENTS CHAPTER I Introduction Characteristics of Television Signals and Cable Television ........... 1 Description of a Cable Television System .•.•••••....•......•........