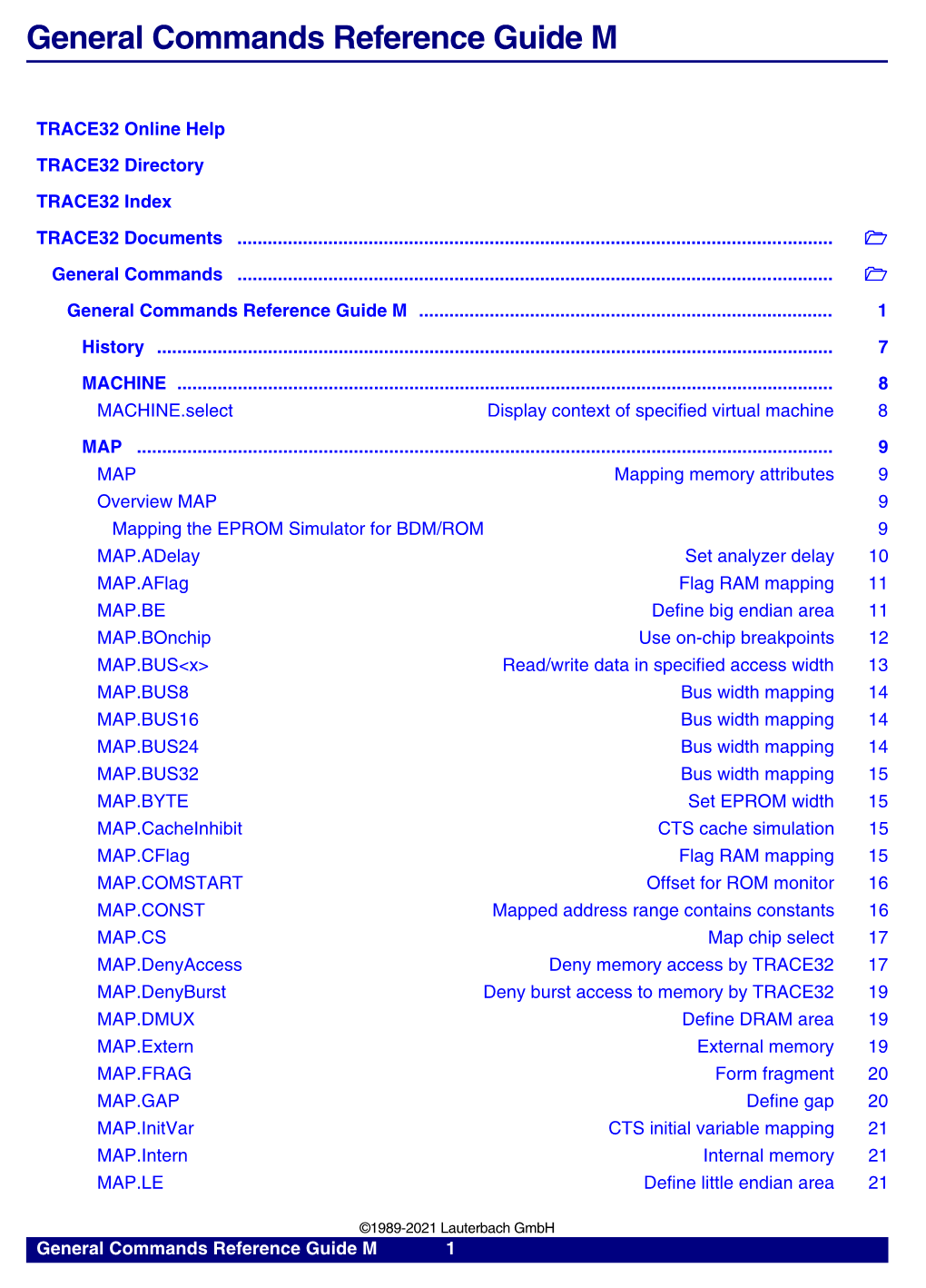

General Commands Reference Guide M

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Memory Protection at Option

Memory Protection at Option Application-Tailored Memory Safety in Safety-Critical Embedded Systems – Speicherschutz nach Wahl Auf die Anwendung zugeschnittene Speichersicherheit in sicherheitskritischen eingebetteten Systemen Der Technischen Fakultät der Universität Erlangen-Nürnberg zur Erlangung des Grades Doktor-Ingenieur vorgelegt von Michael Stilkerich Erlangen — 2012 Als Dissertation genehmigt von der Technischen Fakultät Universität Erlangen-Nürnberg Tag der Einreichung: 09.07.2012 Tag der Promotion: 30.11.2012 Dekan: Prof. Dr.-Ing. Marion Merklein Berichterstatter: Prof. Dr.-Ing. Wolfgang Schröder-Preikschat Prof. Dr. Michael Philippsen Abstract With the increasing capabilities and resources available on microcontrollers, there is a trend in the embedded industry to integrate multiple software functions on a single system to save cost, size, weight, and power. The integration raises new requirements, thereunder the need for spatial isolation, which is commonly established by using a memory protection unit (MPU) that can constrain access to the physical address space to a fixed set of address regions. MPU-based protection is limited in terms of available hardware, flexibility, granularity and ease of use. Software-based memory protection can provide an alternative or complement MPU-based protection, but has found little attention in the embedded domain. In this thesis, I evaluate qualitative and quantitative advantages and limitations of MPU-based memory protection and software-based protection based on a multi-JVM. I developed a framework composed of the AUTOSAR OS-like operating system CiAO and KESO, a Java implementation for deeply embedded systems. The framework allows choosing from no memory protection, MPU-based protection, software-based protection, and a combination of the two. -

The Central Processing Unit(CPU). the Brain of Any Computer System Is the CPU

Computer Fundamentals 1'stage Lec. (8 ) College of Computer Technology Dept.Information Networks The central processing unit(CPU). The brain of any computer system is the CPU. It controls the functioning of the other units and process the data. The CPU is sometimes called the processor, or in the personal computer field called “microprocessor”. It is a single integrated circuit that contains all the electronics needed to execute a program. The processor calculates (add, multiplies and so on), performs logical operations (compares numbers and make decisions), and controls the transfer of data among devices. The processor acts as the controller of all actions or services provided by the system. Processor actions are synchronized to its clock input. A clock signal consists of clock cycles. The time to complete a clock cycle is called the clock period. Normally, we use the clock frequency, which is the inverse of the clock period, to specify the clock. The clock frequency is measured in Hertz, which represents one cycle/second. Hertz is abbreviated as Hz. Usually, we use mega Hertz (MHz) and giga Hertz (GHz) as in 1.8 GHz Pentium. The processor can be thought of as executing the following cycle forever: 1. Fetch an instruction from the memory, 2. Decode the instruction (i.e., determine the instruction type), 3. Execute the instruction (i.e., perform the action specified by the instruction). Execution of an instruction involves fetching any required operands, performing the specified operation, and writing the results back. This process is often referred to as the fetch- execute cycle, or simply the execution cycle. -

Symbian OS Platform Security Model

THE SYMBIAN OS BECAME FULLY OPEN sourced in February 2010, which opens even BO LI, ELENA RESHETOVA, AND T U O M A S A U R A more possibilities for application develop- ers to understand and analyze its security Symbian OS solution. We present a short introduction to the software features of Symbian plat- platform form security: three trust tiers, capability model, data caging, and the Symbian signed security model process. We also try to compare the security Bo Li is a second-year student in the master’s solution with the classical design principles program in security and mobile computing in this area, as well as briefly discuss gen- at Aalto University, Finland. He got his bach- elor’s degree in communications engineering eral design challenges and potential weak- in 2008 from Fudan University, China. nesses. [email protected] Elena Reshetova is a senior security engineer Introduction at Nokia, as well as a postgraduate student at Aalto University. She is interested in With the development of mobile devices and mo- various research areas related to platform bile computers, more and more people rely strongly security, security aspects of networking, and on them. People use mobile devices and mobile cryptography. computers to arrange their schedules, contact each [email protected] other, process emails, and share rich media con- tent. People believe it is safe to do so because it Tuomas Aura is a professor at Aalto Uni- versity, Finland. His research interests are feels secure just knowing it is “right there with security and privacy in communications you” [8]. -

The Microarchitecture of a Low Power Register File

The Microarchitecture of a Low Power Register File Nam Sung Kim and Trevor Mudge Advanced Computer Architecture Lab The University of Michigan 1301 Beal Ave., Ann Arbor, MI 48109-2122 {kimns, tnm}@eecs.umich.edu ABSTRACT Alpha 21464, the 512-entry 16-read and 8-write (16-r/8-w) ports register file consumed more power and was larger than The access time, energy and area of the register file are often the 64 KB primary caches. To reduce the cycle time impact, it critical to overall performance in wide-issue microprocessors, was implemented as two 8-r/8-w split register files [9], see because these terms grow superlinearly with the number of read Figure 1. Figure 1-(a) shows the 16-r/8-w file implemented and write ports that are required to support wide-issue. This paper directly as a monolithic structure. Figure 1-(b) shows it presents two techniques to reduce the number of ports of a register implemented as the two 8-r/8-w register files. The monolithic file intended for a wide-issue microprocessor without hardly any register file design is slow because each memory cell in the impact on IPC. Our results show that it is possible to replace a register file has to drive a large number of bit-lines. In register file with 16 read and 8 write ports, intended for an eight- contrast, the split register file is fast, but duplicates the issue processor, with a register file with just 8 read and 8 write contents of the register file in two memory arrays, resulting in ports so that the impact on IPC is a few percent. -

System Design for a Computational-RAM Logic-In-Memory Parailel-Processing Machine

System Design for a Computational-RAM Logic-In-Memory ParaIlel-Processing Machine Peter M. Nyasulu, B .Sc., M.Eng. A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Doctor of Philosophy Ottaw a-Carleton Ins titute for Eleceical and Computer Engineering, Department of Electronics, Faculty of Engineering, Carleton University, Ottawa, Ontario, Canada May, 1999 O Peter M. Nyasulu, 1999 National Library Biôiiothkque nationale du Canada Acquisitions and Acquisitions et Bibliographie Services services bibliographiques 39S Weiiington Street 395. nie WeUingtm OnawaON KlAW Ottawa ON K1A ON4 Canada Canada The author has granted a non- L'auteur a accordé une licence non exclusive licence allowing the exclusive permettant à la National Library of Canada to Bibliothèque nationale du Canada de reproduce, ban, distribute or seU reproduire, prêter, distribuer ou copies of this thesis in microform, vendre des copies de cette thèse sous paper or electronic formats. la forme de microficbe/nlm, de reproduction sur papier ou sur format électronique. The author retains ownership of the L'auteur conserve la propriété du copyright in this thesis. Neither the droit d'auteur qui protège cette thèse. thesis nor substantial extracts fkom it Ni la thèse ni des extraits substantiels may be printed or otherwise de celle-ci ne doivent être imprimés reproduced without the author's ou autrement reproduits sans son permission. autorisation. Abstract Integrating several 1-bit processing elements at the sense amplifiers of a standard RAM improves the performance of massively-paralle1 applications because of the inherent parallelism and high data bandwidth inside the memory chip. -

Historical Perspective and Further Reading 162.E1

2.21 Historical Perspective and Further Reading 162.e1 2.21 Historical Perspective and Further Reading Th is section surveys the history of in struction set architectures over time, and we give a short history of programming languages and compilers. ISAs include accumulator architectures, general-purpose register architectures, stack architectures, and a brief history of ARMv7 and the x86. We also review the controversial subjects of high-level-language computer architectures and reduced instruction set computer architectures. Th e history of programming languages includes Fortran, Lisp, Algol, C, Cobol, Pascal, Simula, Smalltalk, C+ + , and Java, and the history of compilers includes the key milestones and the pioneers who achieved them. Accumulator Architectures Hardware was precious in the earliest stored-program computers. Consequently, computer pioneers could not aff ord the number of registers found in today’s architectures. In fact, these architectures had a single register for arithmetic instructions. Since all operations would accumulate in one register, it was called the accumulator , and this style of instruction set is given the same name. For example, accumulator Archaic EDSAC in 1949 had a single accumulator. term for register. On-line Th e three-operand format of RISC-V suggests that a single register is at least two use of it as a synonym for registers shy of our needs. Having the accumulator as both a source operand and “register” is a fairly reliable indication that the user the destination of the operation fi lls part of the shortfall, but it still leaves us one has been around quite a operand short. Th at fi nal operand is found in memory. -

Motorola 68000 Opcodes

Motorola 68000 CPU Opcodes Mnemonic Size Single Effective Address Operation Word Data Mnemonic Size Single Effective Address Operation Word Data Addressing Mode Format M Xn ORI to CCR B 0 0 0 0 0 0 0 0 0 0 1 1 1 1 0 0 B I RTE 0 1 0 0 1 1 1 0 0 1 1 1 0 0 1 1 Data register Dn 0 0 0 reg ORI to SR W 0 0 0 0 0 0 0 0 0 1 1 1 1 1 0 0 W I RTS 0 1 0 0 1 1 1 0 0 1 1 1 0 1 0 1 Address register An 0 0 1 reg ORI B W L 0 0 0 0 0 0 0 0 S M Xn I TRAPV 0 1 0 0 1 1 1 0 0 1 1 1 0 1 1 0 Address (An) 0 1 0 reg ANDI to CCR B 0 0 0 0 0 0 1 0 0 0 1 1 1 1 0 0 B I RTR 0 1 0 0 1 1 1 0 0 1 1 1 0 1 1 1 Address with Postincrement (An)+ 0 1 1 reg ANDI to SR W 0 0 0 0 0 0 1 0 0 1 1 1 1 1 0 0 W I JSR 0 1 0 0 1 1 1 0 1 0 M Xn Address with Predecrement -(An) 1 0 0 reg ANDI B W L 0 0 0 0 0 0 1 0 S M Xn I JMP 0 1 0 0 1 1 1 0 1 1 M Xn Address with Displacement (d16, An) 1 0 1 reg SUBI B W L 0 0 0 0 0 1 0 0 S M Xn I MOVEM W L 0 1 0 0 1 D 0 0 1 S M Xn W M Address with Index (d8, An, Xn) 1 1 0 reg ADDI B W L 0 0 0 0 0 1 1 0 S M Xn I LEA L 0 1 0 0 An 1 1 1 M Xn Program Counter with Displacement (d16, PC) 1 1 1 0 1 0 EORI to CCR B 0 0 0 0 1 0 1 0 0 0 1 1 1 1 0 0 B I CHK W 0 1 0 0 Dn 1 1 0 M Xn Program Counter with Index (d8, PC, Xn) 1 1 1 0 1 1 EORI to SR W 0 0 0 0 1 0 1 0 0 1 1 1 1 1 0 0 W I ADDQ B W L 0 1 0 1 Data 0 S M Xn Absolute Short (xxx).W 1 1 1 0 0 0 EORI B W L 0 0 0 0 1 0 1 0 S M Xn I SUBQ B W L 0 1 0 1 Data 1 S M Xn Absolute Long (xxx).L 1 1 1 0 0 1 CMPI B W L 0 0 0 0 1 1 0 0 S M Xn I Scc B 0 1 0 1 Condition 1 1 M Xn Immediate #imm 1 1 1 1 0 0 BTST B L 0 0 0 0 1 0 0 -

Computer Architectures

Computer Architectures Motorola 68000, 683xx a ColdFire – CISC CPU Principles Demonstrated Czech Technical University in Prague, Faculty of Electrical Engineering AE0B36APO Computer Architectures Ver.1.10 1 Original Desktop/Workstation 680X0 Feature 68000 'EC000 68010 68020 68030 68040 68060 Data bus 16 8/16 16 8/16/32 8/16/32 32 32 Addr bus 23 23 23 32 32 32 32 Misaligned Addr - - - Yes Yes Yes Yes Virtual memory - - Yes Yes Yes Yes Yes Instruct Cache - - 3 256 256 4096 8192 Data Cache - - - - 256 4096 8192 Memory manager 68451 or 68851 68851 Yes Yes Yes ATC entries - - - - 22 64/64 64/64 FPU interface - - - 68881 or 68882 Internal FPU built-in FPU - - - - - Yes Yes Burst Memory - - - - Yes Yes Yes Bus Cycle type asynchronous both synchronous Data Bus Sizing - - - Yes Yes use 68150 Power (watts) 1.2 0.13-0.26 0.13 1.75 2.6 4-6 3.9-4.9 at frequency of 8.0 8-16 8 16-25 16-50 25-40 50-66 MIPS/kDhryst. 1.2/2.1 2.5/4.3 6.5/11 14/23 35/60 100/300 Transistors 68k 84k 190k 273k 1,170k 2,500k Introduction 1979 1982 1984 1987 1991 1994 AE0B36APO Computer Architectures 2 M68xxx/CPU32/ColdFire – Basic Registers Set 31 16 15 8 7 0 User programming D0 D1 model registers D2 D3 DATA REGISTERS D4 D5 D6 D7 16 15 0 A0 A1 A2 A3 ADDRESS REGISTERS A4 A5 A6 16 15 0 A7 (USP) USER STACK POINTER 0 PC PROGRAM COUNTER 15 8 7 0 0 CCR CONDITION CODE REGISTER 31 16 15 0 A7# (SSP) SUPERVISOR STACK Supervisor/system POINTER 15 8 7 0 programing model (CCR) SR STATUS REGISTER 31 0 basic registers VBR VECTOR BASE REGISTER 31 3 2 0 SFC ALTERNATE FUNCTION DFC CODE REGISTERS AE0B36APO Computer Architectures 3 Status Register – Conditional Code Part USER BYTE SYSTEM BYTE (CONDITION CODE REGISTER) 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 T1 T0 S 0 0 I2 I1 I0 0 0 0 X N Z V C TRACE INTERRUPT EXTEND ENABLE PRIORITY MASK NEGATIVE SUPERVISOR/USER ZERO STATE OVERFLOW CARRY ● N – negative .. -

Variable-Length Encoding (VLE) Extension Programming Interface Manual

UM0438 User manual Variable-Length Encoding (VLE) extension programming interface manual Introduction This user manual defines a programming model for use with the variable-length encoding (VLE) instruction set extension. Three types of programming interfaces are described herein: ■ An application binary interface (ABI) defining low-level coding conventions ■ An assembly language interface ■ A simplified mnemonic assembly language interface July 2007 Rev 1 1/50 www.st.com Contents UM0438 Contents Preface . 7 About this book . 7 Audience. 7 Organization . 7 Suggested reading . 7 Related documentation. 8 General information . 8 Conventions . 8 Terminology conventions . 9 Acronyms and abbreviations. 9 1 Overview . 11 1.1 Application Binary Interface (ABI) . 11 1.2 Assembly language interface . 11 1.3 Simplified mnemonics assembly language interface . 11 2 Application Binary Interface (ABI) . 12 2.1 Instruction and data representation . 12 2.2 Executable and Linking Format (ELF) object files . 12 2.2.1 VLE information section . 13 2.2.2 VLE identification . 14 2.2.3 Relocation types . 15 3 Instruction set . 20 Appendix A Simplified mnemonics for VLE instructions . 22 A.1 Overview . 22 A.2 Subtract simplified mnemonics . 22 A.2.1 Subtract immediate. 22 A.2.2 Subtract . 23 A.3 Rotate and shift simplified mnemonics . 23 A.3.1 Operations on words. 24 A.4 Branch instruction simplified mnemonics . 24 2/50 UM0438 Contents A.4.1 Key facts about simplified branch mnemonics . 26 A.4.2 Eliminating the BO32 and BO16 operands. 26 A.4.3 The BI32 and BI16 operand—CR Bit and field representations . 27 A.4.4 BI32 and BI16 operand instruction encoding . -

1.1.2. Register File

國 立 交 通 大 學 資訊科學與工程研究所 碩 士 論 文 同步多執行緒架構中可彈性切割與可延展的暫存 器檔案設計之研究 Design of a Flexibly Splittable and Stretchable Register File for SMT Architectures 研 究 生:鐘立傑 指導教授:單智君 教授 中 華 民 國 九 十 六 年 八 月 I II III IV 同步多執行緒架構中可彈性切割與可延展的暫存 器檔案設計之研究 學生:鐘立傑 指導教授:單智君 博士 國立交通大學資訊科學與工程研究所 碩士班 摘 要 如何利用最少的硬體資源來支援同步多執行緒是一個很重要的研究議題,暫存 器檔案(Register file)在微處理器晶片面積中佔有顯著的比例。而且為了支援同步多 執行緒,每一個執行緒享有自己的一份暫存器檔案,這樣的設計會增加晶片的面積。 在本篇論文中,我們提出了一份可彈性切割與可延展的暫存器檔案設計,在這 個設計裡:1.我們可以在需要的時候彈性切割一份暫存器檔案給兩個執行緒來同時 使用,2.適當的延伸暫存器檔案的大小來增加兩個執行緒共用的機會。 藉由我們設計可以得到的益處有:1.增加硬體資源的使用率,2. 減少對於記憶 體的存取以及 3.提升系統的效能。此外我們設計概念可以任意的滿足不同的應用程 式的需求。 V Design of a Flexibly Splittable and Stretchable Register File for SMT Architectures Student:Li-Jie Jhing Advisor:Dr, Jean Jyh-Jiun Shann Institute of Computer Science and Engineering National Chiao-Tung University Abstract How to support simultaneous multithreading (SMT) with minimum resource hence becomes a critical research issue. The register file in a microprocessor typically occupies a significant portion of the chip area, and in order to support SMT, each thread will have a copy of register file. That will increase the area overhead. In this thesis, we propose a register file design techniques that can 1. Split a copy of physical register file flexibly into two independent register sets when required, simultaneously operable for two independent threads. 2. Stretch the size of the physical register file arbitrarily, to increase probability of sharing by two threads. Benefits of these designs are: 1. Increased hardware resource utilization. 2. Reduced memory -

A Minimal Powerpc™ Boot Sequence for Executing Compiled C Programs

Order Number: AN1809/D Rev. 0, 3/2000 Semiconductor Products Sector Application Note A Minimal PowerPCª Boot Sequence for Executing Compiled C Programs PowerPC Systems Architecture & Performance [email protected] This document describes the procedures necessary to successfully initialize a PowerPC processor and begin executing programs compiled using the PowerPC embedded application interface (EABI). The items discussed in this document have been tested for MPC603eª, MPC750, and MPC7400 microprocessors. The methods and source code presented in this document may work unmodiÞed on similar PowerPC platforms as well. This document contains the following topics: ¥ Part I, ÒOverview,Ó provides an overview of the conditions and exceptions for the procedures described in this document. ¥ Part II, ÒPowerPC Processor Initialization,Ó provides information on the general setup of the processor registers, caches, and MMU. ¥ Part III, ÒPowerPC EABI Compliance,Ó discusses aspects of the EABI that apply directly to preparing to jump into a compiled C program. ¥ Part IV, ÒSample Boot Sequence,Ó describes the basic operation of the boot sequence and the many options of conÞguration, explains in detail a sample conÞgurable boot and how the code may be modiÞed for use in different environments, and discusses the compilation procedure using the supporting GNU build environment. ¥ Part V, ÒSource Files,Ó contains the complete source code for the Þles ppcinit.S, ppcinit.h, reg_defs.h, ld.script, and MakeÞle. This document contains information on a new product under development by Motorola. Motorola reserves the right to change or discontinue this product without notice. © Motorola, Inc., 2000. All rights reserved. Overview Part I Overview The procedures discussed in this document perform only the minimum amount of work necessary to execute a user program. -

Symbian Foundation Press Conference

Symbian Foundation Press conference M/C – Merran Wrigley Exciting Internet experiences for the aspirations of billions 2 © 2008 Symbian Foundation Mobile software set free Symbian Foundation Kai Öistämö Executive Vice President, Nokia Shared vision for an unparalleled open mobile software platform 4 © 2008 Symbian Foundation That unites Symbian OS, S60, UIQ and MOAP(S) 5 © 2008 Symbian Foundation Creating the most proven, open, complete mobile software platform 6 © 2008 Symbian Foundation With over 200 million devices already shipped 7 © 2008 Symbian Foundation For free. 8 © 2008 Symbian Foundation Creating one platform, royalty-free Foundation Differentiated Member experience MOAP(S) 9 © 2008 Symbian Foundation Creating one platform, royalty-free Foundation Differentiated Member experience Symbian Foundation Platform Applications suite Runtimes UI framework Middleware Operating system Tools & SDK 10 © 2008 Symbian Foundation The first step to our goal • Acquiring Symbian Ltd • Closing expected in Q4 2008 • Symbian Ltd to be part of Nokia • Nokia will contribute Symbian OS and S60 to Symbian Foundation 11 © 2008 Symbian Foundation Fulfilling the Symbian mission Symbian Foundation Nigel Clifford CEO, Symbian Symbian Ltd Mission To become the most widely used software platform on the planet 13 © 2008 Symbian Foundation The leading global open platform 12% Symbian Linux 11% Microsoft RIM 60% Apple 11% Other Source Canalys – Cumulative 4% 12 month period to Q1 2008 2% 14 © 2008 Symbian Foundation The choice for the top vendors Samsung MOTO