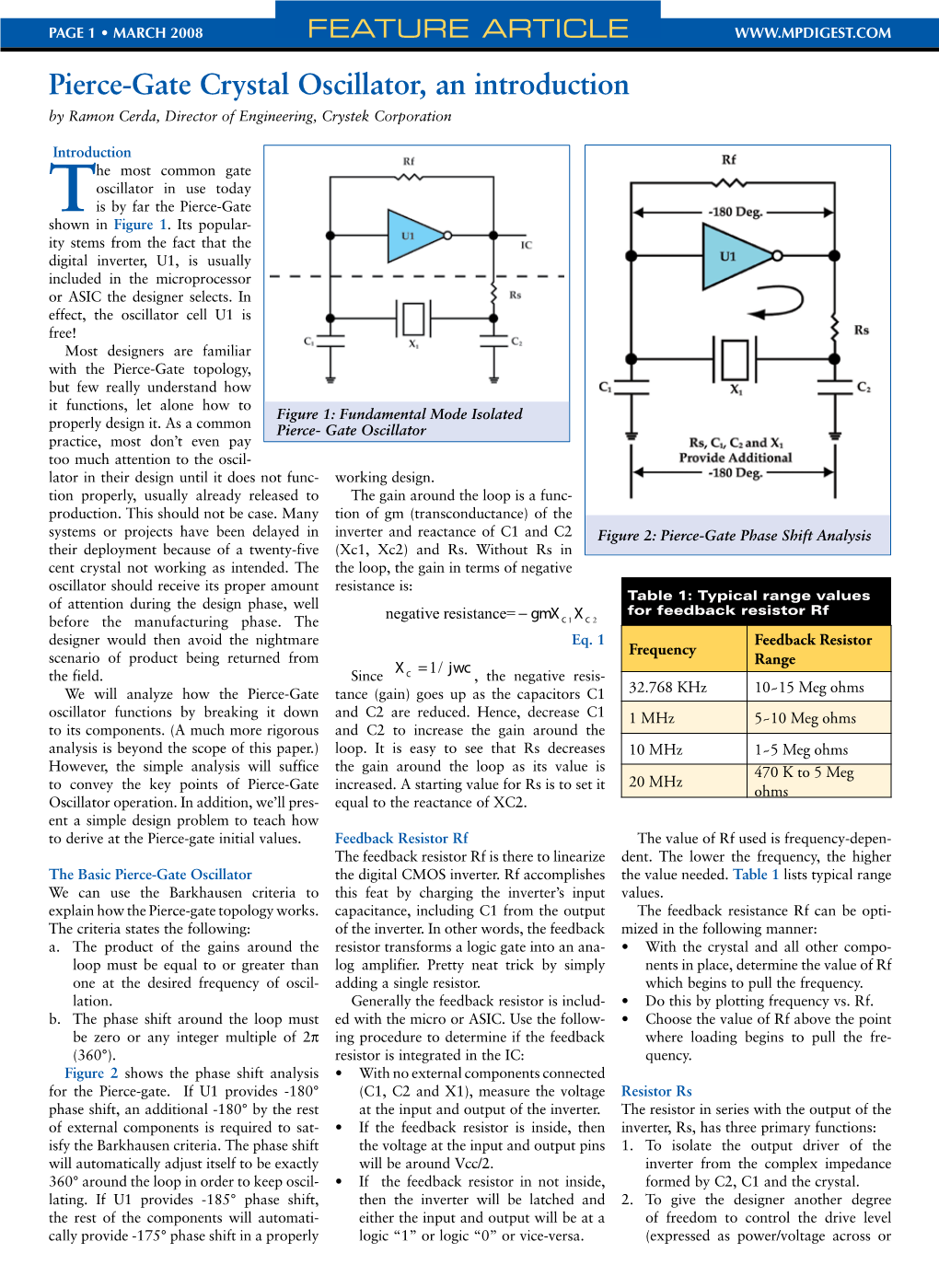

Pierce-Gate Crystal Oscillator, an Introduction by Ramon Cerda, Director of Engineering, Crystek Corporation

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Crystal Oscillators 1

Crystal oscillators 1. Objectives The aim of the exercise is to get acquainted with issues concerning the generation of waveforms (including sinewaves) in the basic structures of crystal generators. In addition, the exercise aims to familiarize with surface mount technique SMT (Surface Mount Technology/ Technics or SMD – Surface mounting Devices). 2. Components and instrumentation. In the exercise, it is possible to test quartz generators operating in the three simplest and most popular system structures: • Colpitts-Pierce quartz generator with bipolar transistor, • quartz generator implemented on TTL gates, • quartz generator implemented on CMOS inverters 2.1. Colpittsa-Pierce’s oscillator with bipolar transistor. The Colpitts-Pierce quartz generator system working in parallel resonance is shown in Fig. 1. + UCC Rb C2 XT C1 Re UWY Fig. 1. Colpittsa-Pierce oscillator with BJT. Using, in the system, quartz resonators with resonance values up to several tens of MHz, the elements C1, Re in the generator system can be selected according to the graph shown in Fig.2. RezystorRe [Ohm] Frequency [MHz] Fig. 2. Selection of C1 and Re elements in the Colpitts-Pierce oscillator 2.2. Quartz oscillator implemented using TTL digital IC Fig. 3 presents a diagram of a quartz oscillator implemented using NAND gates in TTL technology. The oscillator works in series resonance. In this system, while maintaining the same resistance values, quartz resonators with a frequency from a few to 10 MHz can be used. 560 1k8 220 220 UWY XT Fig. 3. Cristal oscillator with serial resonance implemented with NAND gates in TTL technology In the laboratory exercise, it is proposed to implement the system using TTL series 74LS00 (pins of the IC are shown in in Fig.4). -

Analysis of BJT Colpitts Oscillators - Empirical and Mathematical Methods for Predicting Behavior Nicholas Jon Stave Marquette University

Marquette University e-Publications@Marquette Master's Theses (2009 -) Dissertations, Theses, and Professional Projects Analysis of BJT Colpitts Oscillators - Empirical and Mathematical Methods for Predicting Behavior Nicholas Jon Stave Marquette University Recommended Citation Stave, Nicholas Jon, "Analysis of BJT Colpitts sO cillators - Empirical and Mathematical Methods for Predicting Behavior" (2019). Master's Theses (2009 -). 554. https://epublications.marquette.edu/theses_open/554 ANALYSIS OF BJT COLPITTS OSCILLATORS – EMPIRICAL AND MATHEMATICAL METHODS FOR PREDICTING BEHAVIOR by Nicholas J. Stave, B.Sc. A Thesis submitted to the Faculty of the Graduate School, Marquette University, in Partial Fulfillment of the Requirements for the Degree of Master of Science Milwaukee, Wisconsin August 2019 ABSTRACT ANALYSIS OF BJT COLPITTS OSCILLATORS – EMPIRICAL AND MATHEMATICAL METHODS FOR PREDICTING BEHAVIOR Nicholas J. Stave, B.Sc. Marquette University, 2019 Oscillator circuits perform two fundamental roles in wireless communication – the local oscillator for frequency shifting and the voltage-controlled oscillator for modulation and detection. The Colpitts oscillator is a common topology used for these applications. Because the oscillator must function as a component of a larger system, the ability to predict and control its output characteristics is necessary. Textbooks treating the circuit often omit analysis of output voltage amplitude and output resistance and the literature on the topic often focuses on gigahertz-frequency chip-based applications. Without extensive component and parasitics information, it is often difficult to make simulation software predictions agree with experimental oscillator results. The oscillator studied in this thesis is the bipolar junction Colpitts oscillator in the common-base configuration and the analysis is primarily experimental. The characteristics considered are output voltage amplitude, output resistance, and sinusoidal purity of the waveform. -

Spectrum Analyzer Circuits 062-1055-00

Circuit Concepts BOOKS IN THIS SERIES: Circuit Concepts Power Supply Circuits 062-0888-01 Oscilloscope Cathode-Ray Tubes 062-0852-01 Storage Cathode-Ray Tubes and Circuits 062-0861-01 Television Waveform Processing Circuits 062-0955-00 Digital Concepts 062-1030-00 Spectrum Analyzer Circuits 062-1055-00 Oscilloscope Trigger Circuits 062-1056-00 Sweep Generator Circuits 062-1098-00 Measurement Concepts Information Display Concepts 062-1005-00 Semiconductor Devices 062-1009-00 Television System Measurements 062-1064-00 Spectrum Analyzer Measurements 062-1070-00 Engine Analysis 062-1074-00 Automated Testing Systems 062-1106-00 SPECTRUM ANALYZER CIRCUITS BY MORRIS ENGELSON Significant Contributions by GORDON LONG WILL MARSH CIRCUIT CONCEPTS FIRST EDITION, SECOND PRINTING, AUGUST 1969 062-1055-00 ©TEKTRONIX, INC.; 1969 BEAVERTON, OREGON 97005 ALL RIGHTS RESERVED CONTENTS 1 BACKGROUND MATERIAL 1 2 COMPONENTS AND SUBASSEMBLIES 23 3 FILTERS 55 4 AMPLI FI'ERS 83 5 MIXERS 99 6 OSCILLATORS 121 7 RF ATTENNATORS 157 BIBLIOGRAPHY 171 INDEX 175 1 BACKGROUND MATERIAL Many spectrum analyzer circuits are based on principles with which most engineers may not be familiar. It is the purpose of this chapter to review some of this specialized background material. This review is not intended to be either complete or rigorous. Those desiring a more complete discussion are referred to the basic references and the bibliography. TRANSMISSION LINES* At low frequencies the basic circuit elements are lumped. At higher frequencies, however, where the size of circuit elements is comparable to a wavelength, lumped elements can not be used easily, if at all. This accounts for the extensive use of distributed circuits at higher frequencies. -

AN826 Crystal Oscillator Basics and Crystal Selection for Rfpic™ And

AN826 Crystal Oscillator Basics and Crystal Selection for rfPICTM and PICmicro® Devices • What temperature stability is needed? Author: Steven Bible Microchip Technology Inc. • What temperature range will be required? • Which enclosure (holder) do you desire? INTRODUCTION • What load capacitance (CL) do you require? • What shunt capacitance (C ) do you require? Oscillators are an important component of radio fre- 0 quency (RF) and digital devices. Today, product design • Is pullability required? engineers often do not find themselves designing oscil- • What motional capacitance (C1) do you require? lators because the oscillator circuitry is provided on the • What Equivalent Series Resistance (ESR) is device. However, the circuitry is not complete. Selec- required? tion of the crystal and external capacitors have been • What drive level is required? left to the product design engineer. If the incorrect crys- To the uninitiated, these are overwhelming questions. tal and external capacitors are selected, it can lead to a What effect do these specifications have on the opera- product that does not operate properly, fails prema- tion of the oscillator? What do they mean? It becomes turely, or will not operate over the intended temperature apparent to the product design engineer that the only range. For product success it is important that the way to answer these questions is to understand how an designer understand how an oscillator operates in oscillator works. order to select the correct crystal. This Application Note will not make you into an oscilla- Selection of a crystal appears deceivingly simple. Take tor designer. It will only explain the operation of an for example the case of a microcontroller. -

AN-400 a Study of the Crystal Oscillator for CMOS-COPS

AN-400 A Study Of The Crystal Oscillator For CMOS-COPS Literature Number: SNOA676 A Study of the Crystal Oscillator for CMOS-COPS AN-400 National Semiconductor A Study of the Crystal Application Note 400 Oscillator for Abdul Aleaf August 1986 CMOS-COPSTM INTRODUCTION TABLE I The most important characteristic of CMOS-COPS is its low A. Crystal oscillator vs. external squarewave COP410C power consumption. This low power feature does not exist change in current consumption as a function of frequen- in TTL and NMOS systems which require the selection of cy and voltage, chip held in reset, CKI is d4. low power IC's and external components to reduce power I e total power supply current drain (at VCC). consumption. Crystal The optimization of external components helps decrease the power consumption of CMOS-COPS based systems Inst. cyc. V f ImA even more. CC ckI time A major contributor to power consumption is the crystal os- 2.4V 32 kHz 125 ms 8.5 cillator circuitry. m Table I presents experimentally observed data which com- 5.0V 32 kHz 125 s83 pares the current drain of a crystal oscillator vs. an external 2.4V 1 MHz 4 ms 199 squarewave clock source. 5.0V 1 MHz 4 ms 360 The main purpose of this application note is to provide ex- perimentally observed phenomena and discuss the selec- External Squarewave tion of suitable oscillator circuits that cover the frequency Inst. cyc. range of the CMOS-COPS. V f I CC ckI time Table I clearly shows that an unoptimized crystal oscillator draws more current than an external squarewave clock. -

Crystals Load Capacitance Calculation And

Load Capacitance PRINTED: 12/21/2012 TYPICAL OSCILLATOR CIRCUIT OSC CELL OSC CELL = oscillator circuit integrated into any IC. Rf = feedback resistor, sometimes integrated in IC or is required as external resistor Rf CLOCK SIGNAL Cg = capacitance of oscillator input for IC internal use Cd = capacitance of oscillator output Rd = Phase shift resistor, necessary at lower frequencies to meet oscillation condition that phase shift all the way around the oscillator loop need to add up to 360°. Y1 = Quartz crystal unit C1 and C1 = external load capacitors. CPCB1 and CPCB2 = stray capacitances of PCB traces Cg Cd The total LOAD CAPACITANCE of the oscillator circuit is the sum of all capacitances. OSC IN OSC OUT consisting of: 1. The two external capacitors (here called C1 and C2) 2. The IC input and output capacitances (here called Cg and Cd) 3. The stray capacitances of PCB traces (here called CPCB1 and CPCB2) CPCB1 Rd Commonly being only the values of the external capacitors known so that a correct calculation of the actual load capacitance is not possible. SIGNAL OUTPUT OPTIONALCLOCK In such case we use simlified formula to calculate the load capacitance as: C1 C2 CL C TOTAL C1 C2 STRAY CPCB2 Here C1 and C2 are the external capacitors in the cricuit, values should be known. Cstray is summarized value for IC input and output capacitance and the PCB traces. Y1 Cstray in a 3.3VDC circuit is often 3~4pF. C1 C2 Cstray in a 5.0VDC circuit often 5~7pF. However, we have also seen circuits that had large deviation from these values. -

MEMS) Technology

Microchip Oscillators and Clocks Using Microelectromechanical Systems (MEMS) Technology Author: John Clark and Graham Mostyn The next milestone will be next-generation MEMS res- Microchip Technology Inc. onators that achieve very low phase noise for high-end communication systems. Microchip acquired MEMS timing technology through OVERVIEW the purchases of Discera and Micrel in 2015. Since Dis- For decades, oscillators and clocks have relied on cera shipped its first production oscillators in 2008, quartz crystals for the creation of a stable frequency almost 100 million devices have been manufactured reference. Crystals perform very well for many applica- and sold. tions. However, microelectromechanical systems This paper describes the benefits of a MEMS-based (MEMS) technology, replacing quartz crystals with solution, the resonator technology, and the design of MEMS resonators, entered the marketplace ten years the final product. ago and is rapidly maturing. MEMS-based timing devices offer high reliability KEY FUNCTIONALITY (including AEC-Q100 certification for automotive use), extended operating temperatures, small size, and low Microchip’s MEMS-based oscillators and clocks offer power consumption. Video surveillance, automotive benefits over traditional quartz solutions (Figure 1). ADAS, general industrial applications, and data trans- These include stable frequency, small size, high reli- mission to 10 Gbps are prime areas of usage today. ability, flexibility, many programmable features, fast guaranteed start-up, and high integration. FIGURE 1: Benefits of Microchip MEMS-Based Oscillators and Clocks. 2017 Microchip Technology Inc. DS00002344A-page 1 MICROCHIP RESONATOR quency of the beam and minimize vibrational energy TECHNOLOGY loss to the substrate. This, in turn, maximizes its quality factor and frequency selectivity. -

Sinusoidal and Non- Sinusoidal Oscillators

CHAPTER65 Learning Objectives ➣ What is an Oscillator? SINUSOIDAL ➣ Classification of Oscillators ➣ Damped and Undamped AND NON- Oscillations ➣ Oscillatory Circuit ➣ Essentials of a Feedback LC SINUSOIDAL Oscillator ➣ Tuned Base Oscillator ➣ Tuned Collector Oscillator OSCILLATORS ➣ Hartley Oscillator ➣ FET Hartley Oscillator ➣ Colpitts Oscillator ➣ Clapp Oscillator ➣ FET Colpitts Oscillator ➣ Crystal Controlled Oscillator ➣ Transistor Pierce Cystal Oscillator ➣ FET Pierce Oscillator ➣ Phase Shift Principle ➣ RC Phase Shift Oscillator ➣ Wien Bridge Oscillator ➣ Pulse Definitions ➣ Basic Requirements of a Sawtooth Generator ➣ UJT Sawtooth Generator ➣ Multivibrators (MV) ➣ Astable Multivibrator An oscillator is an electronic device used for ➣ Bistable Multivibrator (BMV) the purpose of generating a signal. Oscillators ➣ Schmitt Trigger are found in computers, wireless receivers ➣ Transistor Blocking Oscillator and transmitters, and audiofrequency equipment particularly music synthesizers 2408 Electrical Technology 65.1. What is an Oscillator ? An electronic oscillator may be defined in any one of the following four ways : 1. It is a circuit which converts dc energy into ac energy at a very high frequency; 2. It is an electronic source of alternating cur- rent or voltage having sine, square or sawtooth or pulse shapes; 3. It is a circuit which generates an ac output signal without requiring any externally ap- Oscillator plied input signal; 4. It is an unstable amplifier. These definitions exclude electromechanical alternators producing 50 Hz ac power or other devices which convert mechanical or heat energy into electric energy. 65.2. Comparison Between an Amplifier and an Oscillator As discussed in Chapter-10, an amplifier produces an output signal whose waveform is similar to the input signal but whose power level is generally high. -

P020190719536109927550.Pdf

Integrated Circuits and Systems Series Editor Anantha Chandrakasan, Massachusetts Institute of Technology Cambridge, Massachusetts For other titles published in this series, go to www.springer.com/series/7236 Eric Vittoz Low-Power Crystal and MEMS Oscillators The Experience of Watch Developments Eric Vittoz Ecole Polytechnique Fédérale de Lausanne (EPFL) 1015 Lausanne Switzerland [email protected] ISSN 1558-9412 ISBN 978-90-481-9394-3 e-ISBN 978-90-481-9395-0 DOI 10.1007/978-90-481-9395-0 Springer Dordrecht Heidelberg London New York Library of Congress Control Number: 2010930852 © Springer Science+Business Media B.V. 2010 No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Cover design: Spi Publisher Services Printed on acid-free paper Springer is part of Springer Science+Business Media (www.springer.com) To my wife Monique Contents Preface ...................................................... xi Symbols ..................................................... xiii 1 Introduction ............................................. 1 1.1 Applications of Quartz Crystal Oscillators. ................ 1 1.2 HistoricalNotes ...................................... 2 1.3 TheBookStructure................................... -

Microcontroller Oscillator Circuit Design Considerations by Cathy Cox and Clay Merritt

Freescale Semiconduct or, Inc... 2 CrystalOscillatorTheory 1 Introduction By CathyCoxandClayMerritt Considerations Microcontroller OscillatorCircuitDesign can beexpected,asignificantamountofpowerisrequiredtokeepanamplifierinlinearmode. digital NANDgateasananalogamplifierisnotlogical,butthishowoscillatorcircuitfunctions.As The voltageincreasesuntiltheNANDgateamplifiersaturates.Atfirstglance,thoughtofusinga energized, theloopgainmustbegreaterthanonewhilevoltageatXTALgrowsovermultiplecycles. overall loopgainequaltooneandanphaseshiftthatisintegermultipleof360 stabilize thefrequencyandsupply180 sists oftwoparts:aninvertingamplifierthatsuppliesavoltagegainand180 The Pierce-typeoscillatorcircuitshownin pitfalls. document istodevelopasystematicapproachgoodoscillatordesignandpointoutsomecommon ing crystalandmicrocontrollerfunctionswithoutthehelpofmatingspecifications.Theobjectivethis timing overawidetemperaturerangeusecrystaloscillator.PCBdesignershavethetaskofintegrat- The heartbeatofeverymicrocontrollerdesignistheoscillatorcircuit.Mostdesignsthatdemandprecise cy selectivefeedbackpath.ThecrystalcombinedwithC 1. 2.The M68HC11oscillatorcircuitpinsarelabeledXTALand EXTAL. forpowerconservation. STOP isaninternallygeneratedsignalthatdisablestheoscillator circuit EXTAL Cx STOP Figure 1PierceOscillator 2 ° phaseshiftfeedbackpath.Insteadystate,thiscircuithasan 1 Figure 1 Rf Y1 isusedonmostmicrocontrollers.Thiscircuitcon- x andC y formatunedPInetworkthattendsto XTAL Cy 2 ° phaseshiftandafrequen- Order thisdocument byAN1706/D ° . Uponbeing Freescale Semiconductor, -

CIRCUIT IDEAS for DESIGNERS Ultra Low Voltage Crystal Oscillator

Category: FET CIRCUIT IDEAS FOR DESIGNERS Schematic no. fet_11121.0 Ultra Low Voltage Crystal Oscillator Circuit using Active Loads Description This is an ultra low-voltage crystal oscillator circuit using EPAD MOSFETs with active load and output buffer. This circuit is similar to a standard crystal oscillator circuit used in 5V circuits. However, at low operating voltages, the values of the resistors and the impedance of the inverter MOSFET are selected to optimize oscillation stability and minimize power consumption. An active load device using a depletion mode EPAD MOSFET such as an ALD114804 replaces a passive resistor load at the inverter. Using appropriate component values, a crystal oscillator circuit can be configured to operate in the range of supply voltages from V+ = 5V to V+ = 0.5V, with crystal frequencies ranging from 1 MHz to 16 MHz. The active load reduces the contrast in the corresponding power consumption at different supply voltages. At V+= 5V the power consumed by the oscillator circuit is 346 µW whereas at V+= 0.5V, the same circuit consumes a mere 32 µW while oscillating at the same selected crystal frequency. At higher crystal frequencies in excess of 4 MHz, a dual EPAD MOSFET can be connected in parallel to provide more low voltage drive current necessary. Recommended Components EPAD MOSFETs: M1, M3 ALD110800 (either single or dual MOSFET connected in parallel); Active Load: M2 ½ ALD114904 CL1=10pF; CL2 = 22pF; RF= 5.6MOhm; RL= 6 Ohm; ROUT = 2.4KOhm Other Related Circuit Ideas Schematic no. fet_11120.0 Ultra Low Voltage Micropower Crystal Oscillator Circuit 2005 Advanced Linear Devices, Inc. -

EURO QUARTZ TECHNICAL NOTES Crystal Theory Page 1 of 8

EURO QUARTZ TECHNICAL NOTES Crystal Theory Page 1 of 8 Introduction The Crystal Equivalent Circuit If you are an engineer mainly working with digital devices these notes In the crystal equivalent circuit above, L1, C1 and R1 are the crystal should reacquaint you with a little analogue theory. The treatment is motional parameters and C0 is the capacitance between the crystal non-mathematical, concentrating on practical aspects of circuit design. electrodes, together with capacitances due to its mounting and lead- out arrangement. The current flowing into a load at B as a result of a Various oscillator designs are illustrated that with a little constant-voltage source of variable frequency applied at A is plotted experimentation may be easily modified to suit your requirements. If below. you prefer a more ‘in-depth’ treatment of the subject, the appendix contains formulae and a list of further reading. At low frequencies, the impedance of the motional arm of the crystal is extremely high and current rises with increasing frequency due solely to Series or Parallel? the decreasing reactance of C0. A frequency fr is reached where L1 is resonant with C1, and at which the current rises dramatically, being It can often be confusing as to whether a particular circuit arrangement limited only by RL and crystal motional resistance R1 in series. At only requires a parallel or series resonant crystal. To help clarify this point, it slightly higher frequencies the motional arm exhibits an increasing net is useful to consider both the crystal equivalent circuit and the method inductive reactance, which resonates with C0 at fa, causing the current by which crystal manufacturers calibrate crystal products.