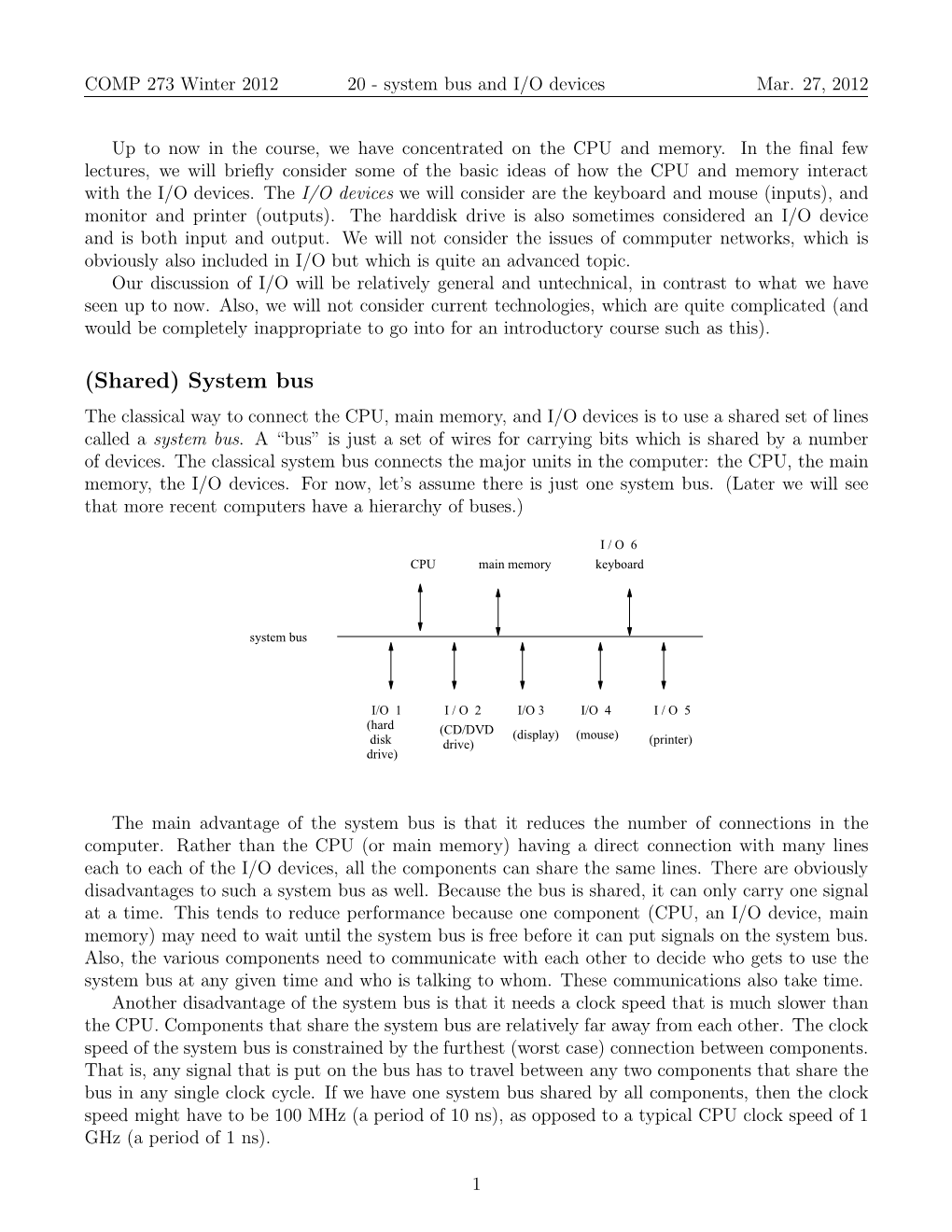

(Shared) System Bus the Classical Way to Connect the CPU, Main Memory, and I/O Devices Is to Use a Shared Set of Lines Called a System Bus

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

System Buses EE2222 Computer Interfacing and Microprocessors

System Buses EE2222 Computer Interfacing and Microprocessors Partially based on Computer Organization and Architecture by William Stallings Computer Electronics by Thomas Blum 2020 EE2222 1 Connecting • All the units must be connected • Different type of connection for different type of unit • CPU • Memory • Input/Output 2020 EE2222 2 CPU Connection • Reads instruction and data • Writes out data (after processing) • Sends control signals to other units • Receives (& acts on) interrupts 2020 EE2222 3 Memory Connection • Receives and sends data • Receives addresses (of locations) • Receives control signals • Read • Write • Timing 2020 EE2222 4 Input/Output Connection(1) • Similar to memory from computer’s viewpoint • Output • Receive data from computer • Send data to peripheral • Input • Receive data from peripheral • Send data to computer 2020 EE2222 5 Input/Output Connection(2) • Receive control signals from computer • Send control signals to peripherals • e.g. spin disk • Receive addresses from computer • e.g. port number to identify peripheral • Send interrupt signals (control) 2020 EE2222 6 What is a Bus? • A communication pathway connecting two or more devices • Usually broadcast (all components see signal) • Often grouped • A number of channels in one bus • e.g. 32 bit data bus is 32 separate single bit channels • Power lines may not be shown 2020 EE2222 7 Bus Interconnection Scheme 2020 EE2222 8 Data bus • Carries data • Remember that there is no difference between “data” and “instruction” at this level • Width is a key determinant of performance • 8, 16, 32, 64 bit 2020 EE2222 9 Address bus • Identify the source or destination of data • e.g. CPU needs to read an instruction (data) from a given location in memory • Bus width determines maximum memory capacity of system • e.g. -

ECESATUSB1 This Expresscard Power Esata Port Controller Card

1 Port ExpressCard Power eSATA Controller Adapter Card StarTech ID: ECESATUSB1 This ExpressCard Power eSATA port controller card can be installed in an available ExpressCard 34/54 mm slot to provide a powered eSATA connection, and also alternatively provide either external SATA (data only) or USB 2.0 connectivity from one uniquely designed port if using with standard eSATA or USB devices. An ideal solution for using an eSATA SSD Flash drive on your laptop, the power eSATA card delivers both a high speed eSATA connection and power from the combined USB port. A versatile connectivity solution, the card features built-in port multiplier support, allowing multi-drive eSATA storage enclosures to be connected to the host computer using a single eSATA cable. Taking advantage of the transfer speed of eSATA connection and the 5V power output of the USB 2.0 port, the ExpressCard Power eSATA adapter is the perfect answer for connecting compatible mobile drive enclosures, similar to the built-in power eSATA port provided by the following laptop computers: Toshiba: Satellite E105, A350, Satellite Pro P300; Qosmio G50, X305, Portege A600, M750, R500, R600; and Tecra M10, R10, A10. Dell: Studio 15, 17; Latitude E6400, E6500; Precision M2400, M4400, M6400, M6400 Covet. Applications Connects to eSATA SSD Flash drives, such as OCZ Throttle, Kangaru e-Flash drives and Ridata Racer series flash drives Provides connectivity between Notebooks and PCs with ExpressCard slots to external drive enclosures with Power eSATA (eSATA+USB) port, or with regular eSATA -

Computer Bus Characteristics

Upendra Sharma (upsharma.in) Computer Bus A bus, in computing, is a set of physical connections (cables, printed circuits, etc.) which can be shared by multiple hardware components in order to communicate with one another. The purpose of buses is to reduce the number of "pathways" needed for communication between the components, by carrying out all communications over a single data channel. This is why the metaphor of a "data highway" is sometimes used. If only two hardware components communicate over the line, it is called a hardware port (such as a serial port or parallel port). Characteristics A bus is characterised by the amount of information that can be transmitted at once. This amount, expressed in bits, corresponds to the number of physical lines over which data is sent simultaneously. A 32-wire ribbon cable can transmit 32 bits in parallel. The term "width" is used to refer to the number of bits that a bus can transmit at once. Additionally, the bus speed is also defined by its frequency (expressed in Hertz), the number of data packets sent or received per second. Each time that data is sent or received is called a cycle. This way, it is possible to find the maximum transfer speed of the bus, the amount of data which it can transport per unit of time, by multiplying its width by its frequency. A bus with a width of 16 bits and a frequency of 133 MHz, therefore, has a transfer speed equal to: Upendra Sharma (upsharma.in) Types of Buses In reality, each bus is generally constituted of 50 to 100 distinct physical lines, divided into three subassemblies: The address bus (sometimes called the memory bus) transports memory addresses which the processor wants to access in order to read or write data. -

Input/Output

Lectures 24: Input/Output I. External devices A. External devices are not connected directly to the system bus because they have a wide range of control logics, as well as data transfer speeds and formats. B. Virtually all external devices have buffers, control signals, status signals, and data bits. C. Those that deal with other forms of energy have transducers that converts from non-electrical data to electrical data, (e.g. key press to ASCII in a keyboard), or electrical data to non-electrical data (e.g. bytes to light in a monitor). D. In the past, intra-system (less than 1 meter) connections were usually parallel, and inter-system were serial. Now almost all are serial. 1. To convert from parallel to serial use a shift register. 2. USB (universal serial bus) is a common standard for serial transmission with USB 3.0 transferring at 5Gb/s. II. I/O Modules (south bridge and north bridge on a PC) on the motherboard provide the logic, buffers, error detection, and ports to communicate with the external devices on one side, and a system-type bus on the other. For external device interfaces, the modules have data, status, and control lines. For the system bus they have data, address, and control lines. The south bridge handles slower I/O devices and is connected to the north bridge rather than the system bus directly. III. Programmed I/O A. Overview of Programmed I/O waits for the processor to query it. B. Four types of I/O commands: 1) control (e.g. -

2 Port Flush Mount Expresscard 54Mm Superspeed USB 3.0 Card Adapter Startech ID: ECUSB3S254F

2 Port Flush Mount ExpressCard 54mm SuperSpeed USB 3.0 Card Adapter StarTech ID: ECUSB3S254F The ECUSB3S254F 2-Port Flush Mount USB 3.0 ExpressCard Adapter uses a unique form factor design that allows it to sit fully in a standard 54mm laptop ExpressCard slot without sticking out. When inserted, the USB 3.0 ports provided by the ExpressCard adapter sit flush with the sides of the laptop, creating a seamless add-on that can be left installed even while on the move, without having to worry about impact damage to either the card or the ExpressCard slot. The SuperSpeed USB 3.0 Card supports data transfer rates of up to 5Gbps, and is backward compatible with USB 2.0 (at up to 480Mbps), or USB 1.1/1.0 at up to 12/1.5 Mbps respectively - the perfect laptop accessory for users to connect USB devices, both new and old. Applications Users who need USB connectivity, but do not need to swap between other ExpressCard adapters, so will leave the card installed in the card slot Mobile users who want to leave ExpressCard adapters installed, without worry about damaging the card or slot while on the move Connect high performance USB 3.0 external storage devices to a laptop Upgrade an older laptop with USB 3.0 connectivity Expand on your laptop expansion capabilities with additional USB ports Features Unique flush-mount form factor design Two SuperSpeed USB 3.0 compliant ports with support for transfer rates up to 5 Gbps Backward compatible with USB 2.0/1.x devices Compliant with USB 3.0 base specification 1.0 and xHCI specification 0.95 Compliant with -

FLEXBUS: a High-Performance System-On-Chip Communication

34.4 FLEXBUS: A High-Performance System-on-Chip Communication Architecture with a Dynamically Configurable Topology ∗ Krishna Sekar Kanishka Lahiri Anand Raghunathan Sujit Dey Dept. of ECE NEC Laboratories America NEC Laboratories America Dept. of ECE UC San Diego, CA 92093 Princeton, NJ 08540 Princeton, NJ 08540 UC San Diego, CA 92093 [email protected] [email protected] [email protected] [email protected] ABSTRACT portunities for dynamically controlling the spatial allocation of com- munication architecture resources among different SoC components, In this paper, we describe FLEXBUS, a flexible, high-performance on- chip communication architecture featuring a dynamically configurable a capability, which if properly exploited, can yield substantial per- formance gains. We also describe techniques for choosing optimized topology. FLEXBUS is designed to detect run-time variations in com- munication traffic characteristics, and efficiently adapt the topology of FLEXBUS configurations under time-varying traffic profiles. We have the communication architecture, both at the system-level, through dy- conducted detailed experiments on FLEXBUS using a commercial de- namic bridge by-pass, as well as at the component-level, using compo- sign flow to analyze its area and performance under a wide variety of system-level traffic profiles, and applied it to an IEEE 802.11 MAC nent re-mapping. We describe the FLEXBUS architecture in detail and present techniques for its run-time configuration based on the char- processor design. The results demonstrate that FLEXBUS provides up acteristics of the on-chip communication traffic. The techniques un- to 31.5% performance gains compared to conventional architectures, with negligible hardware overhead. -

PDP-11 Bus Handbook (1979)

The material in this document is for informational purposes only and is subject to change without notice. Digital Equipment Corpo ration assumes no liability or responsibility for any errors which appear in, this document or for any use made as a result thereof. By publication of this document, no licenses or other rights are granted by Digital Equipment Corporation by implication, estoppel or otherwise, under any patent, trademark or copyright. Copyright © 1979, Digital Equipment Corporation The following are trademarks of Digital Equipment Corporation: DIGITAL PDP UNIBUS DEC DECUS MASSBUS DECtape DDT FLIP CHIP DECdataway ii CONTENTS PART 1, UNIBUS SPECIFICATION INTRODUCTION ...................................... 1 Scope ............................................. 1 Content ............................................ 1 UNIBUS DESCRIPTION ................................................................ 1 Architecture ........................................ 2 Unibus Transmission Medium ........................ 2 Bus Terminator ..................................... 2 Bus Segment ....................................... 3 Bus Repeater ....................................... 3 Bus Master ........................................ 3 Bus Slave .......................................... 3 Bus Arbitrator ...................................... 3 Bus Request ....................................... 3 Bus Grant ......................................... 3 Processor .......................................... 4 Interrupt Fielding Processor ......................... -

Upgrading and Repairing Pcs, 21St Edition Editor-In-Chief Greg Wiegand Copyright © 2013 by Pearson Education, Inc

Contents at a Glance Introduction 1 1 Development of the PC 5 2 PC Components, Features, and System Design 19 3 Processor Types and Specifications 29 4 Motherboards and Buses 155 5 BIOS 263 UPGRADING 6 Memory 325 7 The ATA/IDE Interface 377 AND 8 Magnetic Storage Principles 439 9 Hard Disk Storage 461 REPAIRING PCs 10 Flash and Removable Storage 507 21st Edition 11 Optical Storage 525 12 Video Hardware 609 13 Audio Hardware 679 14 External I/O Interfaces 703 15 Input Devices 739 16 Internet Connectivity 775 17 Local Area Networking 799 18 Power Supplies 845 19 Building or Upgrading Systems 929 20 PC Diagnostics, Testing, and Maintenance 975 Index 1035 Scott Mueller 800 East 96th Street, Indianapolis, Indiana 46240 Upgrading.indb i 2/15/13 10:33 AM Upgrading and Repairing PCs, 21st Edition Editor-in-Chief Greg Wiegand Copyright © 2013 by Pearson Education, Inc. Acquisitions Editor All rights reserved. No part of this book shall be reproduced, stored in a retrieval Rick Kughen system, or transmitted by any means, electronic, mechanical, photocopying, Development Editor recording, or otherwise, without written permission from the publisher. No patent Todd Brakke liability is assumed with respect to the use of the information contained herein. Managing Editor Although every precaution has been taken in the preparation of this book, the Sandra Schroeder publisher and author assume no responsibility for errors or omissions. Nor is any Project Editor liability assumed for damages resulting from the use of the information contained Mandie Frank herein. Copy Editor ISBN-13: 978-0-7897-5000-6 Sheri Cain ISBN-10: 0-7897-5000-7 Indexer Library of Congress Cataloging-in-Publication Data in on file. -

Model 225E MIDI Decoder / Preset Manager the 225E MIDI Decoder Translates Incoming MIDI Messages Into Analog Voltages and Pulses

Description - model 225e MIDI Decoder / Preset Manager The 225e MIDI decoder translates incoming MIDI messages into analog voltages and pulses. These control signals appear on three kinds of "busses" for subsequent distribution to 200e series modules. Four busses are routed internally to 200e series modules that respond directly to MIDI messages. Four more handle only note messages, decoding them into front panel voltages that represent pitches, velocities and pulses with sustain information. An additional six busses handle controller and clock messages (two controllers each), which are translated into standard 0-10 volt control voltages. Busses: Note and Controller message assigments to Pulses and CVs. Note messages are applied to busses A,B,C,D,E,F,G, and H; Continuous Controller and Clock messages are handled by busses J, K, L, M, N, and P. Each bus responds to one selected MIDI channel. But more than one bus may be assigned to the same channel, allowing multiple controllers CVs and note messages to be derived from a single MIDI channel. First select a bus for assignment use "bus select" to illuminate the LED next to the desired bus. MIDI NoteOn and pitch translation: Busses A-H There are two sets of Note messages busses: A-D and E-H. Internal busses will be explained in more detail later. For these busses the following display will appear: Bus:A Ch:15 Poly Tr:24 Ft:75 Vl:/ With the cursor buttons, select a data type. Use the knob to the right of the cursor buttons to enter data for the following fields: Ch: MIDI Channel. -

Computing Platforms Chapter 4

Computing Platforms Chapter 4 COE 306: Introduction to Embedded Systems Dr. Abdulaziz Tabbakh Computer Engineering Department College of Computer Sciences and Engineering King Fahd University of Petroleum and Minerals [Adapted from slides of Dr. A. El-Maleh, COE 306, KFUPM] Next . Basic Computing Platforms The CPU bus Direct Memory Access (DMA) System Bus Configurations ARM Bus: AMBA 2.0 Memory Components Embedded Platforms Platform-Level Performance Computing Platforms COE 306– Introduction to Embedded System– KFUPM slide 2 Embedded Systems Overview Actuator Output Analog/Digital Sensor Input Analog/Digital CPU Memory Embedded Computer Computing Platforms COE 306– Introduction to Embedded System– KFUPM slide 3 Computing Platforms Computing platforms are created using microprocessors, I/O devices, and memory components A CPU bus is required to connect the CPU to other devices Software is required to implement an application Embedded system software is closely tied to the hardware Computing Platform: hardware and software Computing Platforms COE 306– Introduction to Embedded System– KFUPM slide 4 Computing Platform A typical computing platform includes several major hardware components: The CPU provides basic computational facilities. RAM is used for program and data storage. ROM holds the boot program and some permanent data. A DMA controller provides direct memory access capabilities. Timers are used by the operating system A high-speed bus, connected to the CPU bus through a bridge, allows fast devices to communicate efficiently with the rest of the system. A low-speed bus provides an inexpensive way to connect simpler devices and may be necessary for backward compatibility as well. Computing Platforms COE 306– Introduction to Embedded System– KFUPM slide 5 Platform Hardware Components Computer systems may have one or more bus Buses are classified by their overall performance: lows peed, high- speed. -

BUS and CACHE MEMORY ORGANIZATIONS for MULTIPROCESSORS By

BUS AND CACHE MEMORY ORGANIZATIONS FOR MULTIPROCESSORS by Donald Charles Winsor A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 1989 Doctoral Committee: Associate Professor Trevor N. Mudge, Chairman Professor Daniel E. Atkins Professor John P. Hayes Professor James O. Wilkes ABSTRACT BUS AND CACHE MEMORY ORGANIZATIONS FOR MULTIPROCESSORS by Donald Charles Winsor Chairman: Trevor Mudge The single shared bus multiprocessor has been the most commercially successful multiprocessor system design up to this time, largely because it permits the implementation of efficient hardware mechanisms to enforce cache consistency. Electrical loading problems and restricted bandwidth of the shared bus have been the most limiting factors in these systems. This dissertation presents designs for logical buses constructed from a hierarchy of physical buses that will allow snooping cache protocols to be used without the electrical loading problems that result from attaching all processors to a single bus. A new bus bandwidth model is developed that considers the effects of electrical loading of the bus as a function of the number of processors, allowing optimal bus configurations to be determined. Trace driven simulations show that the performance estimates obtained from this bus model agree closely with the performance that can be expected when running a realistic multiprogramming workload in which each processor runs an independent task. The model is also used with a parallel program workload to investigate its accuracy when the processors do not operate independently. This is found to produce large errors in the mean service time estimate, but still gives reasonably accurate estimates for the bus utilization. -

MPC107 PCI Bridge/Integrated Memory Controller Fact Sheet

Freescale Semiconductor, Inc. Fact Sheet MPC107 PCI BRIDGE MEMORY CONTROLLER The MPC107 PCI Bridge/Integrated Memory Controller provides a bridge between the INTEGRATED MEMORY CONTROLLER Peripheral Component Interconnect (PCI) bus and Motorola MPC6xx, MPC7xx, and The memory interface controls processor and PCI . MPC74xx microprocessors. PCI support allows system designers to design systems interactions to main memory. It supports a variety of . quickly using peripherals already designed for PCI and the other standard interfaces programmable timing supporting DRAM (FPM, EDO), c available in the personal computer hardware environment. The MPC107 provides many SDRAM, and ROM/Flash ROM configurations, up to n of the other necessities for embedded applications, including a high-performance speeds of 100 MHz. I , memory controller and dual-processor support; two-channel flexible DMA controller; an r interrupt controller; an I2O-ready message unit; an inter-integrated circuit controller PCI BUS SUPPORT o (I2C); and low-skew clock drivers. The MPC107 contains an Embedded Programmable The MPC107 PCI interface is designed to connect the t Interrupt Controller (EPIC) featuring five hardware interrupts (IRQs) as well as 16 serial c processor and memory buses to the PCI local bus without u interrupts along with four timers. The MPC107 uses an advanced, 2.5V HiP3 process the need for “glue” logic at speeds up to 66 MHz. The d technology and is fully compatible with TTL devices. MPC107 acts as either a master or slave device on the n o MOTOROLA MPC107 BLOCK DIAGRAM c i m 60x Bus e S Memory Data Data Path e l ECC/Parity a Unit PIU c I O s 2 Memory e Add/Cntl e CCU MCU r DMA F 2 Mem Clocks I C DLL I2C PCIU IRQs Clock In EPIC PLL PCI Clocks ATU Arbiter FO Buffer Timers PCI Bus REQ/GNT OSC For More Information On This Product, Go to: www.freescale.com Freescale Semiconductor, Inc.