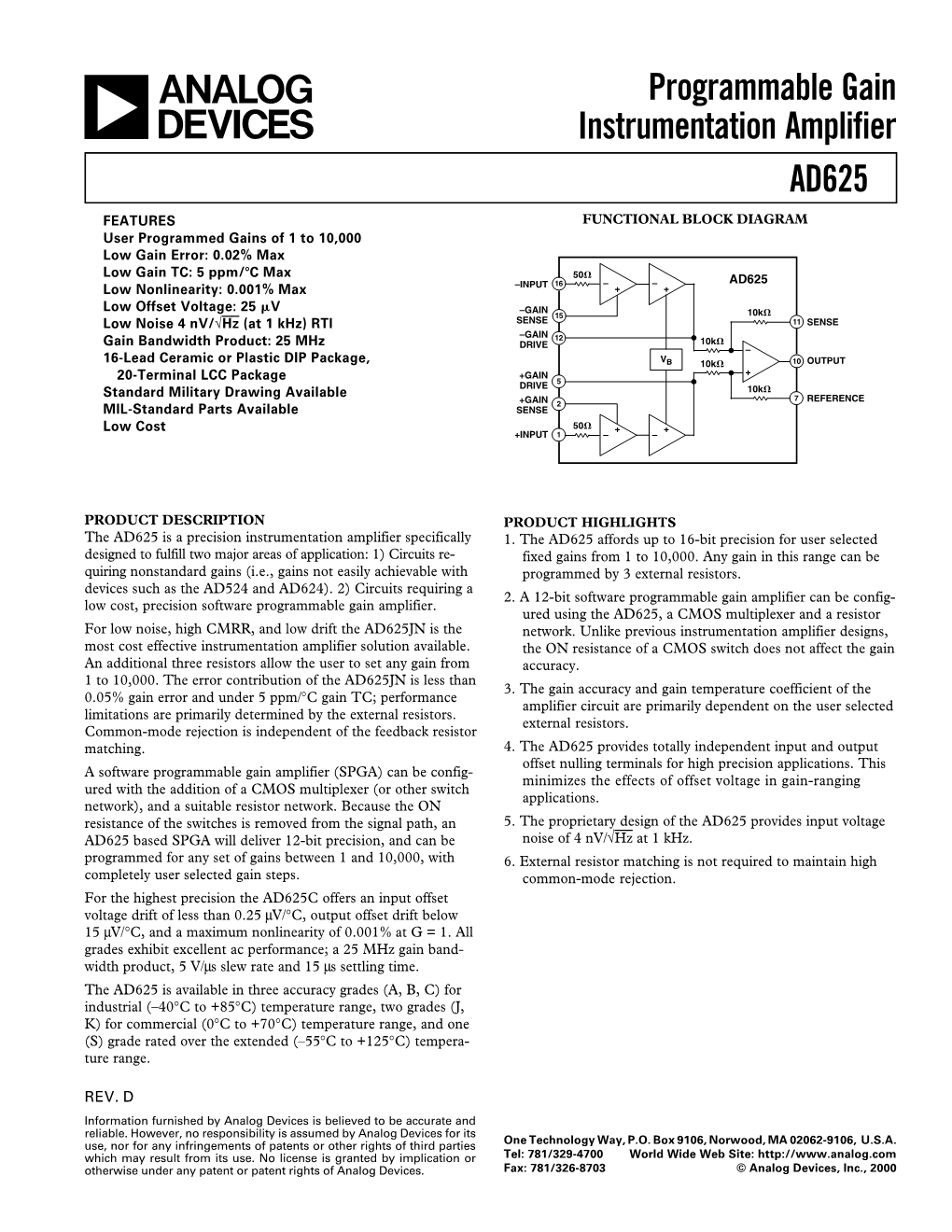

Programmable Gain Instrumentation Amplifier AD625

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

INA106: Precision Gain = 10 Differential Amplifier Datasheet

INA106 IN A1 06 IN A106 SBOS152A – AUGUST 1987 – REVISED OCTOBER 2003 Precision Gain = 10 DIFFERENTIAL AMPLIFIER FEATURES APPLICATIONS ● ACCURATE GAIN: ±0.025% max ● G = 10 DIFFERENTIAL AMPLIFIER ● HIGH COMMON-MODE REJECTION: 86dB min ● G = +10 AMPLIFIER ● NONLINEARITY: 0.001% max ● G = –10 AMPLIFIER ● EASY TO USE ● G = +11 AMPLIFIER ● PLASTIC 8-PIN DIP, SO-8 SOIC ● INSTRUMENTATION AMPLIFIER PACKAGES DESCRIPTION R1 R2 10kΩ 100kΩ 2 5 The INA106 is a monolithic Gain = 10 differential amplifier –In Sense consisting of a precision op amp and on-chip metal film 7 resistors. The resistors are laser trimmed for accurate gain V+ and high common-mode rejection. Excellent TCR tracking 6 of the resistors maintains gain accuracy and common-mode Output rejection over temperature. 4 V– The differential amplifier is the foundation of many com- R3 R4 10kΩ 100kΩ monly used circuits. The INA106 provides this precision 3 1 circuit function without using an expensive resistor network. +In Reference The INA106 is available in 8-pin plastic DIP and SO-8 surface-mount packages. Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners. PRODUCTION DATA information is current as of publication date. Copyright © 1987-2003, Texas Instruments Incorporated Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. www.ti.com SPECIFICATIONS ELECTRICAL ° ± At +25 C, VS = 15V, unless otherwise specified. -

Transistor Basics

Transistor Basics: Collector The schematic representation of a transistor is shown to the left. Note the arrow pointing down towards the emitter. This signifies it's an NPN transistor (current flows in the direction of the arrow). See the Q1 datasheet at: www.fairchildsemi.com. Base 2N3904 A transistor is basically a current amplifier. Say we let 1mA flow into the base. We may get 100mA flowing into the collector. Note: The Emitter currents flowing into the base and collector exit through the emitter (the sum off all currents entering or leaving a node must equal zero). The gain of the transistor will be listed in the datasheet as either βDC or Hfe. The gain won't be identical even in transistors with the same part number. The gain also varies with the collector current and temperature. Because of this we will add a safety margin to all our base current calculations (i.e. if we think we need 2mA to turn on the switch we'll use 4mA just to make sure). Sample circuit and calculations (NPN transistor): Let's say we want to heat a block of metal. One way to do that is to connect a power resistor to the block and run current through the resistor. The resistor heats up and transfers some of the heat to the block of metal. We will use a transistor as a switch to control when the resistor is heating up and when it's cooling off (i.e. no current flowing in the resistor). In the circuit below R1 is the power resistor that is connected to the object to be heated. -

S-Parameter Techniques – HP Application Note 95-1

H Test & Measurement Application Note 95-1 S-Parameter Techniques Contents 1. Foreword and Introduction 2. Two-Port Network Theory 3. Using S-Parameters 4. Network Calculations with Scattering Parameters 5. Amplifier Design using Scattering Parameters 6. Measurement of S-Parameters 7. Narrow-Band Amplifier Design 8. Broadband Amplifier Design 9. Stability Considerations and the Design of Reflection Amplifiers and Oscillators Appendix A. Additional Reading on S-Parameters Appendix B. Scattering Parameter Relationships Appendix C. The Software Revolution Relevant Products, Education and Information Contacting Hewlett-Packard © Copyright Hewlett-Packard Company, 1997. 3000 Hanover Street, Palo Alto California, USA. H Test & Measurement Application Note 95-1 S-Parameter Techniques Foreword HEWLETT-PACKARD JOURNAL This application note is based on an article written for the February 1967 issue of the Hewlett-Packard Journal, yet its content remains important today. S-parameters are an Cover: A NEW MICROWAVE INSTRUMENT SWEEP essential part of high-frequency design, though much else MEASURES GAIN, PHASE IMPEDANCE WITH SCOPE OR METER READOUT; page 2 See Also:THE MICROWAVE ANALYZER IN THE has changed during the past 30 years. During that time, FUTURE; page 11 S-PARAMETERS THEORY AND HP has continuously forged ahead to help create today's APPLICATIONS; page 13 leading test and measurement environment. We continuously apply our capabilities in measurement, communication, and computation to produce innovations that help you to improve your business results. In wireless communications, for example, we estimate that 85 percent of the world’s GSM (Groupe Speciale Mobile) telephones are tested with HP instruments. Our accomplishments 30 years hence may exceed our boldest conjectures. -

Fully-Differential Amplifiers

Application Report S Fully-Differential Amplifiers James Karki AAP Precision Analog ABSTRACT Differential signaling has been commonly used in audio, data transmission, and telephone systems for many years because of its inherent resistance to external noise sources. Today, differential signaling is becoming popular in high-speed data acquisition, where the ADC’s inputs are differential and a differential amplifier is needed to properly drive them. Two other advantages of differential signaling are reduced even-order harmonics and increased dynamic range. This report focuses on integrated, fully-differential amplifiers, their inherent advantages, and their proper use. It is presented in three parts: 1) Fully-differential amplifier architecture and the similarities and differences from standard operational amplifiers, their voltage definitions, and basic signal conditioning circuits; 2) Circuit analysis (including noise analysis), provides a deeper understanding of circuit operation, enabling the designer to go beyond the basics; 3) Various application circuits for interfacing to differential ADC inputs, antialias filtering, and driving transmission lines. Contents 1 Introduction . 3 2 What Is an Integrated, Fully-Differential Amplifier? . 3 3 Voltage Definitions . 5 4 Increased Noise Immunity . 5 5 Increased Output Voltage Swing . 6 6 Reduced Even-Order Harmonic Distortion . 6 7 Basic Circuits . 6 8 Circuit Analysis and Block Diagram . 8 9 Noise Analysis . 13 10 Application Circuits . 15 11 Terminating the Input Source . 15 12 Active Antialias Filtering . 20 13 VOCM and ADC Reference and Input Common-Mode Voltages . 23 14 Power Supply Bypass . 25 15 Layout Considerations . 25 16 Using Positive Feedback to Provide Active Termination . 25 17 Conclusion . 27 1 SLOA054E List of Figures 1 Integrated Fully-Differential Amplifier vs Standard Operational Amplifier. -

MOS Amplifier Basics

ECE 2C Laboratory Manual 2 MOS Amplifier Basics Overview This lab will explore the design and operation of basic single-transistor MOS amplifiers at mid-band. We will explore the common-source and common-gate configurations, as well as a CS amplifier with an active load and biasing. Table of Contents Pre-lab Preparation 2 Before Coming to the Lab 2 Parts List 2 Background Information 3 Small-Signal Amplifier Design and Biasing 3 MOSFET Design Parameters and Subthreshold Currents 5 Estimating Key Device Parameters 7 In-Lab Procedure 8 2.1 Common-Source Amplifier 8 Common-Source, no Source Resistor 8 Linearity and Waveform Distortion 8 Effect of Source and Load Impedances 9 Common-Source with Source Resistor 9 2.2 Common-Gate Amplifier 10 2.3 Amplifiers with Active Loading 11 Feedback-Bias Amplifier 11 CMOS Active-Load CS Amplifier 12 1 © Bob York 2 MOS Amplifier Basics Pre-lab Preparation Before Coming to the Lab Read through the lab experiment to familiarize yourself with the components and assembly sequence. Before coming to the lab, each group should obtain a parts kit from the ECE Shop. Parts List The ECE2 lab is stocked with resistors so do not be alarmed if you kits does not include the resistors listed below. Some of these parts may also have been provided in an earlier kit. Laboratory #2 MOS Amplifiers Qty Description 2 CD4007 CMOS pair/inverter 4 2N7000 NMOS 4 1uF capacitor (electrolytic, 25V, radial) 8 10uF capacitor (electrolytic, 25V, radial) 4 100uF capacitor (electrolytic, 25V, radial) 4 100-Ohm 1/4 Watt resistor 4 220-Ohm 1/4 Watt resistor 1 470-Ohm 1/4 Watt resistor 4 10-KOhm 1/4 Watt resistor 1 33-KOhm 1/4 Watt resistor 2 47-KOhm 1/4 Watt resistor 1 68-KOhm 1/4 Watt resistor 4 100-KOhm 1/4 Watt resistor 1 1-MOhm 1/4 Watt resistor 1 10k trimpot 2 100k trimpot © Bob York Background Information 3 Background Information Small-Signal Amplifier Design and Biasing In earlier experiments with transistors we learned how to establish a desired DC operating condition. -

Fully Differential Op Amps Made Easy

Application Report SLOA099 - May 2002 Fully Differential Op Amps Made Easy Bruce Carter High Performance Linear ABSTRACT Fully differential op amps may be unfamiliar to some designers. This application report gives designers the essential information to get a fully differential design up and running. Contents 1 Introduction . 2 2 What Does Fully Differential Mean?. 2 3 How Is the Second Output Used?. 3 3.1 Differential Gain Stages. 3 3.2 Single-Ended to Differential Conversion. 4 3.3 Working With Terminated Inputs. 5 4 A New Function . 7 5 Conclusions . 8 6 References . 9 List of Figures 1 Single-Ended Op Amp Schematic Symbol. 2 2 Fully Differential Op Amp Schematic Symbol. 2 3 Closing the Loop on a Single-Ended Op Amp. 3 4 Closing the Loop on a Fully Differential Op Amp. 3 5 Single Ended to Differential Conversion. 4 6 Relationship Between Vin, Vout+, and Vout– . 5 7 Fully Differential Amplifier Component Calculator. 6 8 Using a Fully Differential Op Amp to Drive an ADC. 7 9 Effect of Vocm on Vout+ and Vout– . 8 1 SLOA099 1 Introduction Fully differential op amps may be intimidating to some designers, But op amps began as fully differential components over 50 years ago. Techniques about how to use the fully differential versions have been almost lost over the decades. However, today’s fully differential op amps offer performance advantages unheard of in those first units. This report does not attempt a detailed analysis of op amp theory; reference 1 covers theory well. Instead, this report presents just the facts a designer needs to get started, and some resources for further design assistance. -

Tunnel-Diode Microwave Amplifiers

Tunnel diodes provide a means of low-noise microwave amplification, with the amplifiers using the negative resistance of the tunnel diode to a.chieve amplification by reflection. Th e tunnel diode and its assumed equivalent circuit are discussed. The concept of negative-resistance reflection amplifiers is discussed from the standpoints of stability, gain, and noise performance. Two amplifi,er configurations are shown. of which the circulator-coupled type 1'S carried further into a design fo/' a C-band amplifier. The result 1'S an amph'fier at 6000 mc/s with a 5.S-db noise figure over 380 mc/s. An X-band amplifier is also reported. C. T. Munsterman Tunnel-Diode Microwave Am.plifiers ecent advances in tunnel-diode fabrication where the gain of the ith stage is denoted by G i techniques have made the tunnel diode a and its noise figure by F i. This equation shows that Rpractical, low-noise, microwave amplifier. Small stages without gain (G < 1) contribute greatly to size, low power requirements, and reliability make the overall system noise figure, especially if they these devices attractive for missile application, es are not preceded by some source of gain. If a pecially since receiver sensitivity is significantly low-noise-amplification device can be located near improved, with resulting increased homing time. the source of the signal, the contribution from the Work undertaken at APL over the past year has successive stages can be minimized by making G] resulted in the unique design techniques and hard sufficiently large, and the overall noise figure is ware discussed in this paper.-Y.· then that of the amplifier Fl. -

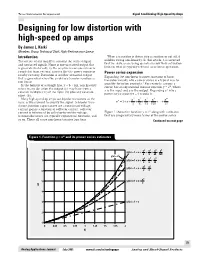

Designing for Low Distortion with High-Speed Op Amps by James L

Texas Instruments Incorporated Signal Conditioning: High-Speed Op Amps Designing for low distortion with high-speed op amps By James L. Karki Member, Group Technical Staff, High-Performance Linear Introduction When a transistor is driven into saturation or cut-off, it The output of any amplifier contains the desired signal exhibits strong non-linearity. In this article, it is assumed and unwanted signals. Noise is one unwanted output that that the devices are being operated below their saturation is generated internally by the amplifier’s components or is limits in what is typically referred to as linear operation. coupled in from external sources like the power supply or Power series expansion nearby circuitry. Distortion is another unwanted output Expanding the non-linear transfer functions of basic that is generated when the amplifier’s transfer function is transistor circuits into a power series is a typical way to non-linear. quantify distortion products.1 For example: assume a In the formula of a straight line, y = b + mx, non-linearity circuit has an exponential transfer function y = ex, where refers to any deviation the output (y) may have from a x is the input and y is the output. Expanding ex into a constant multiple (m) of the input (x) plus any constant power series around x = 0 results in offset (b). 234 5 n Many high-speed op amps use bipolar transistors as the x xxx x x basic active element to amplify the signal. In bipolar tran- ex=+++++1 ++ . 2 6 24 120 n! sistors, junction capacitances are a function of voltage, current gain is a function of collector current, collector current is influenced by collector-to-emitter voltage, Figure 1 shows the function y = ex along with estimates transconductances are typically exponential functions, and that use progressively more terms of the power series. -

A Tutorial on the Decibel This Tutorial Combines Information from Several Authors, Including Bob Devarney, W1ICW; Walter Bahnzaf, WB1ANE; and Ward Silver, NØAX

A Tutorial on the Decibel This tutorial combines information from several authors, including Bob DeVarney, W1ICW; Walter Bahnzaf, WB1ANE; and Ward Silver, NØAX Decibels are part of many questions in the question pools for all three Amateur Radio license classes and are widely used throughout radio and electronics. This tutorial provides background information on the decibel, how to perform calculations involving decibels, and examples of how the decibel is used in Amateur Radio. The Quick Explanation • The decibel (dB) is a ratio of two power values – see the table showing how decibels are calculated. It is computed using logarithms so that very large and small ratios result in numbers that are easy to work with. • A positive decibel value indicates a ratio greater than one and a negative decibel value indicates a ratio of less than one. Zero decibels indicates a ratio of exactly one. See the table for a list of easily remembered decibel values for common ratios. • A letter following dB, such as dBm, indicates a specific reference value. See the table of commonly used reference values. • If given in dB, the gains (or losses) of a series of stages in a radio or communications system can be added together: SystemGain(dB) = Gain12 + Gain ++ Gainn • Losses are included as negative values of gain. i.e. A loss of 3 dB is written as a gain of -3 dB. Decibels – the History The need for a consistent way to compare signal strengths and how they change under various conditions is as old as telecommunications itself. The original unit of measurement was the “Mile of Standard Cable.” It was devised by the telephone companies and represented the signal loss that would occur in a mile of standard telephone cable (roughly #19 AWG copper wire) at a frequency of around 800 Hz. -

MT-072: Precision Variable Gain Amplifiers (Vgas)

MT-072 TUTORIAL Precision Variable Gain Amplifiers (VGAs) INTRODUCTION Most data acquisition systems with wide dynamic range need some method of adjusting the input signal level to the analog-to-digital-converter (ADC). Typical ADC full scale input voltage ranges lie between 1 V and 10 V. To achieve the rated precision of the converter, the maximum input signal should be fairly near its full scale voltage. Transducers however, have a very wide range of output voltages. High gain is needed for a small sensor voltage, but with a large output, a high gain will cause the amplifier or ADC to saturate. So, some type of predictably controllable gain device is needed. Amplifiers with programmable gain have a variety of applications, and Figure 1 below lists some of them. Instrumentation Photodiode amplifier circuits Ultrasound preamplifiers Sonar preamplifiers Wide dynamic range sensors Driving ADCs (some ADCs have on-chip VGAs) Automatic gain control (AGC) loops Gain control z Resistor programmable z Pin programmable z Continuous analog voltage z Digital (5 to 8-bits typical) Figure 1: Variable Gain Amplifier (VGA) Applications Such a device has a gain that is controlled by a dc voltage or, more commonly, a digital input. This device is known as a variable gain amplifier (VGA), or programmable gain amplifier (PGA). In the case of voltage-controlled VGAs, it is common to make the gain in dB proportional to a linear control voltage. Digitally controlled VGAs may be configured either for a few selectable decade gains such as 10, 100, 100, etc., or they may also be configured for binary gains such as 1, 2, 4, 8, etc. -

A Practical Guide to Decibels

A Practical Guide to Decibels A Companion to The Art of Electronics Student Manual Lab 2 UCSD Physics 120A David Kleinfeld [email protected], Han Lin [email protected] Simply put, a decibel is a way to express a ratio. §1. Power Ratios We will first consider a ratio of powers. The formula to memorize and take to your deathbed is: Here, the square brackets mean “units of dB”. Notice that this formula is easy to remember because it has lots of tens, hence the “deci-” in “decibels”. Example 1-1: An attenuator is anything that takes in a signal and spits out a weaker one. Consider the attenuator below. How many dB’s of attenuation does this attenuator provide? Figure 1 In this problem, our power ratio is output power over input power, often simply known as power gain . We have learned something important (memorize this!) from the above example: A Practical Guide to Decibels 2 Question 1-1: An amplifier has a power gain of 2 (if you put in one watt, you will get out two watts). How many dB’s of power gain does this amp provide? ANSWER: +3 dB Question 1-2: You have a -10 dB attenuator. What is P out /P in ? ANSWER: 1/10 Figure 2 §2. Voltage Ratios In low frequency electronics, we are typically more concerned with voltages than power. However, the decibel is defined with respect to power. How can we use decibels for voltage ratios? Recalling that P = V 2/R, A Practical Guide to Decibels 3 Example 2-1: An RC filter provides -3 dB of voltage attenuation at a particular frequency.