Large Vector Extensions Inside the HMC

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

VII Chemical Bond

VII. INTO THE UNKNOWN 7-1 THE ELECTRON DENSITY Now we are ready to look at lowest level of engineering structure—the level at which everything else is determined—the relation between the structure of the electron density and properties. Most importantly, we are going to associate a properties with the structure of that thing we have heard of, but never seen—the chemical bond--begining with the moving electron and electron density. As you know, atomic electrons are in constant motion about the tiny but massive nucleus. An electron’s mass is about 1/2000 that of a proton or neutron and it is moving very fast compared to the nucleus. While an electron is traveling at 3 to 10 million meters per second, as we know from the Boltzmann equation, at the temperature that concern us— < 3000K—even a fast nucleus is moving at less than one thousandth this speed— 1000 or so meters per second. As a mental image, think of an atom as a bee hive. At the center of the hive is the queen bee, which we will take as the location of an atomic nucleus. The electrons are the worker bees, making circuits about the hive. If the beekeeper moves the hive a bit, the circling bees simply move along with the hive—their motion is fast compared to that of the hive. But how fast? Well, the “electron bees” are moving much faster than the ordinary bees of our experience. 16 17 In one second, an individual electron bee will make between 10 and 10 Fig. -

Zatanna and the House of Secrets Graphic Novels for Kids & Teens 741.5 Dc’S New Youth Movement Spring 2020 - No

MEANWHILE ZATANNA AND THE HOUSE OF SECRETS GRAPHIC NOVELS FOR KIDS & TEENS 741.5 DC’S NEW YOUTH MOVEMENT SPRING 2020 - NO. 40 PLUS...KIRBY AND KURTZMAN Moa Romanova Romanova Caspar Wijngaard’s Mary Saf- ro’s Ben Pass- more’s Pass- more David Lapham Masters Rick Marron Burchett Greg Rucka. Pat Morisi Morisi Kieron Gillen The Comics & Graphic Novel Bulletin of satirical than the romantic visions of DC Comics is in peril. Again. The ever- Williamson and Wood. Harvey’s sci-fi struggling publisher has put its eggs in so stories often centered on an ordinary many baskets, from Grant Morrison to the shmoe caught up in extraordinary circum- “New 52” to the recent attempts to get hip with stances, from the titular tale of a science Brian Michael Bendis, there’s hardly a one left nerd and his musclehead brother to “The uncracked. The first time DC tried to hitch its Man Who Raced Time” to William of “The wagon to someone else’s star was the early Dimension Translator” (below). Other 1970s. Jack “the King” Kirby was largely re- tales involved arrogant know-it-alls who sponsible for the success of hated rival Marvel. learn they ain’t so smart after all. The star He was lured to join DC with promises of great- of “Television Terror”, the vicious despot er freedom and authority. Kirby was tired of in “The Radioactive Child” and the title being treated like a hired hand. He wanted to character of “Atom Bomb Thief” (right)— be the idea man, the boss who would come up with characters and concepts, then pass them all pay the price for their hubris. -

X-Men Epic Collection: Children of the Atom Free

FREE X-MEN EPIC COLLECTION: CHILDREN OF THE ATOM PDF Stan Lee,Jack Kirby | 520 pages | 31 Dec 2016 | Marvel Comics | 9780785189046 | English | New York, United States X-Men Epic Collection: Children Of The Atom - Comics by comiXology Goodreads helps you keep track of books you want to read. Want to Read saving…. Want to Read Currently Reading Read. Other editions. Enlarge cover. Error rating book. Refresh and try again. Open Preview See a Problem? Details if other :. Thanks for telling us about the problem. Return to Book Page. X-Men Epic Collection Vol. Jack Kirby. Now, in this massive Epic Collection, you can feast your eyes as Stan, Jack and co. You'll experience the beginning of Professor X's teen team and their mission for peace and brotherhood between man Billed as "The Strangest Super-Heroes of All! You'll experience the beginning of Professor X's teen team and their mission for peace and brotherhood between man and mutant; their first battle with arch-foe Magneto; the dynamic debuts of Juggernaut, the Sentinels, Quicksilver, the Scarlet X-Men Epic Collection: Children of the Atom and X-Men Epic Collection: Children of the Atom Brotherhood of Evil Mutants. Get A Copy. Paperbackpages. More Details Other Editions 2. Friend Reviews. To see what your friends thought of this book, please sign up. Lists with This Book. Community Reviews. Showing Average rating 3. Rating details. More filters. Sort order. Jun 27, Sean Gibson rated it really liked it. And, I love me X-Men Epic Collection: Children of the Atom Stan Lee—the guy is one of my real-life heroes, and Spider-Man is my all- time favorite superhero. -

Superheroes Trivia Quiz Iv

SUPERHEROES TRIVIA QUIZ IV ( www.TriviaChamp.com ) 1> Which superhero carries an indestructible shield? a. The Green Lantern b. Captain America c. Captain Flag d. The Red Tornado 2> Which character is often romantically paired with Batman? a. The Black Canary b. Miss America c. Catwoman d. Hawkgirl 3> Which superhero started out as a petty criminal? a. The Atom b. Spiderman c. The Blue Knight d. Plastic Man 4> Which superhero's alter ego is Raymond Palmer? a. The Atom b. Hawkman c. The Green Arrow d. The Tornado 5> Which superhero is associated with the phrase, "With great power there must also come great responsibility"? a. Spiderman b. Hell Boy c. Batman d. The Hulk 6> Which superhero is nicknamed the "Scarlett Speedster"? a. The Flash b. Speedball c. Stardust d. The Thing 7> Which superhero is dubbed the "Man without Fear"? a. Daredevil b. The Flash c. Wolverine d. Green Lantern 8> Which superhero is the medical doctor for the X-men? a. Storm b. Shadowcat c. Ice Man d. The Beast 9> Who is Batgirl's father (Barbara Gordon)? a. The Mayor b. The Governor c. Batman's Butler d. The Chief of Police 10> Which superhero gains his power from a ring? a. The Green Lantern b. Storm c. Dazzler d. The Hulk 11> Which superhero can manipulate the weather? a. The Tornado b. The Atom c. Strom d. The Thing 12> Which Island does Wonder Woman call home? a. Emerald Island b. Paradise Island c. Amazonia d. Eden Isle 13> Where does the Green Arrow operate? a. -

Archives - Search

Current Auctions Navigation All Archives - Search Category: ALL Archive: BIDDING CLOSED! Over 150 Silver Age Comic Books by DC, Marvel, Gold Key, Dell, More! North (167 records) Lima, OH - WEDNESDAY, November 25th, 2020 Begins closing at 6:30pm at 2 items per minute Item Description Price ITEM Description 500 1966 DC Batman #183 Aug. "Holy Emergency" 10.00 501 1966 DC Batman #186 Nov. "The Jokers Original Robberies" 13.00 502 1966 DC Batman #188 Dec. "The Ten Best Dressed Corpses in Gotham City" 7.50 503 1966 DC Batman #190 Mar. "The Penguin and his Weapon-Umbrella Army against Batman and Robin" 10.00 504 1967 DC Batman #192 June. "The Crystal Ball that Betrayed Batman" 4.50 505 1967 DC Batman #195 Sept. "The Spark-Spangled See-Through Man" 4.50 506 1967 DC Batman #197 Dec. "Catwoman sets her Claws for Batman" 37.00 507 1967 DC Batman #193 Aug. 80pg Giant G37 "6 Suspense Filled Thrillers" 8.00 508 1967 DC Batman #198 Feb. 80pg Giant G43 "Remember? This is the Moment that Changed My Life!" 8.50 509 1967 Marvel Comics Group Fantastic Four #69 Dec. "By Ben Betrayed!" 6.50 510 1967 Marvel Comics Group Fantastic Four #66 Dec. "What Lurks Behind the Beehive?" 41.50 511 1967 Marvel Comics Group The Mighty Thor #143 Aug. "Balder the Brave!" 6.50 512 1967 Marvel Comics Group The Mighty Thor #144 Sept. "This Battleground Earth!" 5.50 513 1967 Marvel Comics Group The Mighty Thor #146 Nov. "...If the Thunder Be Gone!" 5.50 514 1969 Marvel Comics Group The Mighty Thor #166 July. -

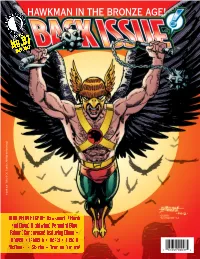

Hawkman in the Bronze Age!

HAWKMAN IN THE BRONZE AGE! July 2017 No.97 ™ $8.95 Hawkman TM & © DC Comics. All Rights Reserved. BIRD PEOPLE ISSUE: Hawkworld! Hawk and Dove! Nightwing! Penguin! Blue Falcon! Condorman! featuring Dixon • Howell • Isabella • Kesel • Liefeld McDaniel • Starlin • Truman & more! 1 82658 00097 4 Volume 1, Number 97 July 2017 EDITOR-IN-CHIEF Michael Eury PUBLISHER John Morrow Comics’ Bronze Age and Beyond! DESIGNER Rich Fowlks COVER ARTIST George Pérez (Commissioned illustration from the collection of Aric Shapiro.) COVER COLORIST Glenn Whitmore COVER DESIGNER Michael Kronenberg PROOFREADER Rob Smentek SPECIAL THANKS Alter Ego Karl Kesel Jim Amash Rob Liefeld Mike Baron Tom Lyle Alan Brennert Andy Mangels Marc Buxton Scott McDaniel John Byrne Dan Mishkin BACK SEAT DRIVER: Editorial by Michael Eury ............................2 Oswald Cobblepot Graham Nolan Greg Crosby Dennis O’Neil FLASHBACK: Hawkman in the Bronze Age ...............................3 DC Comics John Ostrander Joel Davidson George Pérez From guest-shots to a Shadow War, the Winged Wonder’s ’70s and ’80s appearances Teresa R. Davidson Todd Reis Chuck Dixon Bob Rozakis ONE-HIT WONDERS: DC Comics Presents #37: Hawkgirl’s First Solo Flight .......21 Justin Francoeur Brenda Rubin A gander at the Superman/Hawkgirl team-up by Jim Starlin and Roy Thomas (DCinthe80s.com) Bart Sears José Luís García-López Aric Shapiro Hawkman TM & © DC Comics. Joe Giella Steve Skeates PRO2PRO ROUNDTABLE: Exploring Hawkworld ...........................23 Mike Gold Anthony Snyder The post-Crisis version of Hawkman, with Timothy Truman, Mike Gold, John Ostrander, and Grand Comics Jim Starlin Graham Nolan Database Bryan D. Stroud Alan Grant Roy Thomas Robert Greenberger Steven Thompson BRING ON THE BAD GUYS: The Penguin, Gotham’s Gentleman of Crime .......31 Mike Grell Titans Tower Numerous creators survey the history of the Man of a Thousand Umbrellas Greg Guler (titanstower.com) Jack C. -

Jlunlimitedchecklist

WWW.HEROCLIXIN.COM WWW.HEROCLIXIN.COM WWW.HEROCLIXIN.COM WWW.HEROCLIXIN.COM 001_____SUPERMAN .......................................................... 100 C 001_____SUPERMAN .......................................................... 100 C TEAM-UP CARDS (1 of 2) TEAM-UP CARDS (2 of 2) 002_____GREEN LANTERN .................................................. 65 C 002_____GREEN LANTERN .................................................. 65 C 003_____THE FLASH ............................................................. 30 C 003_____THE FLASH ............................................................. 30 C SUPERMAN GREEN ARROW 004_____DR. FATE .........................................................65 - 10 C 004_____DR. FATE .........................................................65 - 10 C 001.01 _____TEAM UP: GREEN LANTERN 026.01 _____TEAM UP: SUPERMAN 005a____BATMAN .................................................................. 70 C 005a____BATMAN .................................................................. 70 C 001.02 _____TEAM UP: BATMAN 026.02 _____TEAM UP: GREEN LANTERN 005b____BATMAN .................................................................. 40 P 005b____BATMAN .................................................................. 40 P 001.03 _____TEAM UP: WONDER WOMAN 026.03 _____TEAM UP: BATMAN 006_____CADMUS LABS SCIENTIST ................................... 15 C 006_____CADMUS LABS SCIENTIST ................................... 15 C 001.04 _____TEAM UP: THE FLASH 026.04 _____TEAM UP: WONDER WOMAN 007_____S.T.A.R. -

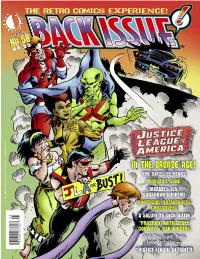

With Gerry Conway & Dan Jurgens

Justice League of America TM & © DC Comics. All Rights Reserved. 0 7 No.58 August 2012 $ 8 . 9 5 1 82658 27762 8 THE RETRO COMICS EXPERIENCE! IN THE BRONZE AGE! “JUSTICE LEAGUE DETROIT”! UNOFFICIAL JLA/AVENGERS CONWAY & DAN JURGENS A SALUTE TO DICK DILLIN “PRO2PRO” WITH GERRY THE SATELLITE YEARS SQUADRON SUPREME And the team fans love to hate — INJUSTICE GANG MARVEL’s JLA, CROSSOVERS ® The Retro Comics Experience! Volume 1, Number 58 August 2012 Celebrating the Best Comics of the '70s, '80s, '90s, and Beyond! EDITOR Michael “Superman”Eury PUBLISHER John “T.O.” Morrow GUEST DESIGNER Michael “Batman” Kronenberg COVER ARTIST ISSUE! Luke McDonnell and Bill Wray COVER COLORIST BACK SEAT DRIVER: Editorial by Michael Eury.........................................................2 Glenn “Green Lantern” Whitmore PROOFREADER Whoever was stuck on Monitor Duty FLASHBACK: 22,300 Miles Above the Earth .............................................................3 A look back at the JLA’s “Satellite Years,” with an all-star squadron of creators SPECIAL THANKS Jerry Boyd Rob Kelly Michael Browning Elliot S! Maggin GREATEST STORIES NEVER TOLD: Unofficial JLA/Avengers Crossovers................29 Rich Buckler Luke McDonnell Never heard of these? Most folks haven’t, even though you might’ve read the stories… Russ Burlingame Brad Meltzer Snapper Carr Mike’s Amazing Dewey Cassell World of DC INTERVIEW: More Than Marvel’s JLA: Squadron Supreme....................................33 ComicBook.com Comics SS editor Ralph Macchio discusses Mark Gruenwald’s dictatorial do-gooders Gerry Conway Eric Nolen- DC Comics Weathington J. M. DeMatteis Martin Pasko BRING ON THE BAD GUYS: The Injustice Gang.....................................................43 Rich Fowlks Chuck Patton These baddies banded together in the Bronze Age to bedevil the League Mike Friedrich Shannon E. -

ATOM-BOMB on Tag Day in Order ' That the M Anehma^R-^A City of V^Hago Charm ■1 • P

i. ,i / X •I. 'v7 -" 7 7 7 X. /• /• Tjll , I . ■; - V- • V if- . -■ :.y- y w y- '' Iw'V*' WEDNESDAY, FEBRUARY iQ Average Daily Net Prcaa Run 1 iW atKlifatfr X KUrtka Week Ended ^ “ - ' 8, 1854 AMta. _ 11,164 •»ii tP IR T o m i operation ______________ _____ CeOuyrt O&scs hearts and asking for donatkas to Fork' tr .gosmiij'.).!., of\ thethtt districtdlfltrtet tfrArtArdirector, nfof <ntArn*linternal iGirWtoHold1 thetumL Meauber at Um Audllr . George C BnuMrIiaf. a mess- large number of gli^ who en Berea* of Clrculatteas the A m u to r the revenue eaM with SUtlon WKNB* thusinsUcaily volunteered to work I .4 Children win he TV, New Britain, -will presoni a Tag Day for ber of the faculty of Maneheater ATOM-BOMB on Tag Day In order ' that the M anehma^r-^A City of V^hago Charm ■1 • p. m. «t the telecaat an the *T95S Federal In* High School and who la In charga a> ‘ . « • - • Amal Chvtvh. D river Fine 4 $35 of Tag Day, haa been aariated by Heart IMva might banefit : come Tax,” Saturday, from diSO to Dcaff Don’t let the other nuclear phjrkieists know you VOL. LXXm, NO. 112 gnest ap«eker 4:45 p. m. • * ' the following faculty advisers of A t'• o'clock, tha plaatlo hearts (Claakllei Advarllalag m Page 18) O n Recldess Cofint Heart Fund the Y-Teena; MISS Mary Mc» nro having henring trouble. Find Qut to d ^ about the nev^ MANCHESTER, CONN„ THURSDAY, FEBRUARY U , J»54 eanitla, epeech will bs eoUseted and takan to ths (TW ENTY B c h ^ wMA Sunset Relwkah l,odge members Adama Miss Anne Beephlef. -

The Flash #750 Deluxe Edition Pdf, Epub, Ebook

THE FLASH #750 DELUXE EDITION PDF, EPUB, EBOOK Joshua Williamson | 128 pages | 07 Jul 2020 | DC Comics | 9781779505071 | English | United States The Flash #750 Deluxe Edition PDF Book Reset it. Red Hood and the Outlaws Vol. Aquaman Vol. About this product Product Information The Flash landmark th Deluxe Edition is celebrated in an all-star collection featuring the best of the Scarlet Speedster! Let's get you back to tracking and discussing your comics! Your subscription to Read More was successful. Rows: Columns:. A moment happening in different realities, but developing in a way which is almost identical. Red Robin. Mike McKone. Collecting the first 12 issues of the series about the ultimate embedded war journalist trapped Of course you have to include a sunny sky, balloons and lighting bolts in that scenario too. Blue Beetle. Young Justice Book 2: Growing Up. Stay in Touch Sign up. Ben Meares. Nathaniel Adam. Chameleon Boy. Price Paid. Sailor Moon 1. Scott Lobdell. With his sacrifice, with accepting his role as the one to sit on the Chair, he saved his family, who now once again lives. Iris works on an article where she interviews ordinary people about the impact that the Flash has had on their lives. Hartley Rathaway. New Teen Titans Omnibus Vol. This wiki All wikis. Doctor Mid-Nite. Categories :. And so, Wally West reaches Tempus Fuginaut , and tells him he found out what he couldn't see by himself: time and reality are in shambles, with existence on the verge of collapsing. Hank Hall. And the end: his family, ripped away from him and from reality. -

Roy Thomas Roy Thomas

Edited by RROOYY TTHHOOMMAASS Celebrating 100 issues— and 50 years— of the legendary comics fanzine Characters TM & ©2011 DC Comics Centennial Edited by ROY THOMAS TwoMorrows Publishing - Raleigh, North Carolina ALTER EG O: CENTENNIAL THE 100TH ISSUE OF ALTER EGO, VOLUME 3 Published by: TwoMorrows Publishing 10407 Bedfordtown Drive Raleigh, North Carolina 27614 www.twomorrows.com • e-mail: [email protected] No part of this book may be reproduced in any form without written permission from the publisher. First Printing: March 2011 All Rights Reserved • Printed in Canada Softcover ISBN: 978-1-60549-031-1 UPC: 1-82658-27763-5 03 Trademarks & Copyrights: All illustrations contained herein are copyrighted by their respective copyright holders and are reproduced for historical reference and research purposes. All characters featured on the cover are TM and ©2011 DC Comics. All rights reserved. DC Comics does not endorse or confirm the accuracy of the views expressed in this book. Editorial package ©2011 Roy Thomas & TwoMorrows Publishing. Individual contributions ©2011 their creators, unless otherwise noted. Editorial Offices: 32 Bluebird Trail, St. Matthews, SC 29135 • e-mail: [email protected] Eight-issue subscriptions $60 U.S., $85 Canada, $107 elsewhere (in U.S. funds) Send subscription funds to TwoMorrows, NOT to editorial offices. Alter Ego is a TM of Roy & Dann Thomas This issue is dedicated to the memory of Mike Esposito and Dr. Jerry G. Bails, founder of A/E Special Thanks to: Christian Voltar Alcala, Heidi Amash, Michael Ambrose, Ger Apeldoorn, Mark Arnold, Michael Aushenker, Dick Ayers, Rodrigo Baeza, Bob Bailey, Jean Bails, Pat Bastienne, Alberto Becattini, Allen Bellman, John Benson, Gil Kane panel above from The Ring Doc Boucher, Dwight Boyd, Jerry K. -

Children of the Atom Is the First Guidebook Star-Faring Aliens—Visited Earth Over a Million Alike")

CONTENTS Section 1: Background............................... 1 Gladiators............................................... 45 Section 2: Mutant Teams ........................... 4 Alliance of Evil ....................................... 47 X-Men...................................... 4 Mutant Force ......................................... 49 X-Factor .................................. 13 Section 3: Miscellaneous Mutants ........................ 51 New Mutants .......................... 17 Section 4: Very Important People (VIP) ................. 62 Hellfire Club ............................. 21 Villains .................................................. 62 Hellions ................................. 27 Supporting Characters ............................ 69 Brotherhood of Evil Mutants ... 30 Aliens..................................................... 72 Freedom Force ........................ 32 Section 5: The Mutant Menace ................................79 Fallen Angels ........................... 36 Section 6: Locations and Items................................83 Morlocks.................................. 39 Section 7: Dreamchild ...........................................88 Soviet Super-Soldiers ............ 43 Maps ......................................................96 Credits: Dinosaur, Diamond Lil, Electronic Mass Tarbaby, Tarot, Taskmaster, Tattletale, Designed by Colossal Kim Eastland Converter, Empath, Equilibrius, Erg, Willie Tessa, Thunderbird, Time Bomb. Edited by Scintilatin' Steve Winter Evans, Jr., Amahl Farouk, Fenris, Firestar,