Pin Information for the Intel® Agilex™ AGIB027 Device Version: 2020-06-05

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Processing Framework and Match-Up Database MODIS Algorithm Version 3 By

Processing Framework and Match-up Database MODIS Algorithm Version 3 By Robert H. Evans University of Miami Miami, FL 33149-1098 April 30, 1999 Appendix 1 - ATBD A1.1 TABLE OF CONTENTS PREFACE .................................................................................................... 6 1.0 INTRODUCTION ...................................................................................... 7 1.1 Algorithm and Product Identification........................................................................7 1.2 Algorithm Overview..........................................................................................7 1.3 Document Scope ..............................................................................................7 1.4 Applicable Documents and Publications .....................................................................7 2.0 OVERVIEW AND BACKGROUND INFORMATION ......................................... 7 2.1 Experimental Objective ......................................................................................7 2.2 Historical Perspective ........................................................................................8 3.0 DESCRIPTION OF ALGORITHM................................................................. 8 3.1 Introduction based on AVHRR-Oceans Pathfinder .........................................................8 Matchup Databases ..............................................................................................8 3.1.1 Global matchup databases............................................................................................................9 -

Tokyo 2020 Paralympic Games

TOKYO 2020 PARALYMPIC GAMES QUALIFICATION REGULATIONS REVISED EDITION, JULY 2020 INTERNATIONAL PARALYMPIC COMMITTEE 2 CONTENTS 1. Introduction 2. Tokyo 2020 Paralympic Games Programme Overview 3. General IPC Regulations on Eligibility 4. IPC Redistribution Policy of Vacant Qualification Slots 5. Universality Wild Cards 6. Key Dates 7. Archery 8. Athletics 9. Badminton 10. Boccia 11. Canoe 12. Cycling (Track and Road) 13. Equestrian 14. Football 5-a-side 15. Goalball 16. Judo 17. Powerlifting 18. Rowing 19. Shooting 20. Swimming 21. Table Tennis 22. Taekwondo 23. Triathlon 24. Volleyball (Sitting) 25. Wheelchair Basketball 26. Wheelchair Fencing 27. Wheelchair Rugby 28. Wheelchair Tennis 29. Glossary 30. Register of Updates INTERNATIONAL PARALYMPIC COMMITTEE 3 INTRODUCTION These Qualification Regulations (Regulations) describe in detail how athletes and teams can qualify for the Tokyo 2020 Paralympic Games in each of the twenty- two (22) sports on the Tokyo 2020 Paralympic Games Programme (Games Programme). It provides to the National Paralympic Committees (NPCs), to National Federations (NFs), to sports administrators, coaches and to the athletes themselves the conditions that allow participation in the signature event of the Paralympic Movement. These Regulations present: • an overview of the Games Programme; • the general IPC regulations on eligibility; • the specific qualification criteria for each sport (in alphabetical order); and • a glossary of the terminology used throughout the Regulations. STRUCTURE OF SPORT-SPECIFIC QUALIFICATION -

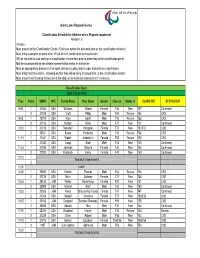

PI Classification Schedule GLRG.Xlsx

Great Lakes Regional Games Classification Schedule for Athletes with a Physical Impairment Version 1.6 Athletes - Must present to the Classification Centre 15 minutes before the allocated time on the classification schedule. Must bring a passport or some other official form of identification to classification. Will be required to read and sign a classification release form prior to presenting to the classification panel. May be accompanied by one athlete representative and/or an interpreter. Must be appropriately dressed in their sport clothes including shorts under tracksuits and sport shoes. Must bring their track chairs, strapping etc that they will be using in competition, to the classification session. Must ensure their throwing frames are at the stadium for technical assessments if necessary. Classification Day 1 Date: 9 June 2016 Time Panel SDMS NPC Family Name First Name Gender Class In Status In CLASS OUT STATUS OUT 9:00 1 31066 USA Williams Taleah Female T46 New T47 Confirmed 2 31008 USA Croft Philip Male T54 Review T54 CRS 9:45 1 15912 USA Rigo Isaiah Male T53 Review T53 CRS 2 31016 USA Nelson Brian Male F37 New F37 Confirmed 10:30 1 31218 USA Beaudoin Margaret Female T37 New T37/F37 CNS 2 30821 USA Evans Frederick Male T34 Review F34 CRS 11:15 1 11241 USA Weber Amberlynn Female T53 Review T53 CRS 2 31330 USA Langi Siale Male F43 New F43 Confirmed 11:45 1 31098 USA Johnson Shayna Female T44 New T44 Confirmed 2 27200 USA Frederick Emily Female F40 New F40 Confirmed 12:15 1 Technical Assessments 2 13:00 Lunch 14:00 1 20880 USA -

Para Athletics Classification Are You, Or Do You Know Someone Who May Be, Interested in Para Athletics?

PARA ATHLETICS CLASSIFICATION ARE YOU, OR DO YOU KNOW SOMEONE WHO MAY BE, INTERESTED IN PARA ATHLETICS? Classification determines who is eligible to compete in a Para sport and then groups the eligible athletes into sport classes according to their activity limitation in a certain sport or event. Athletes are classified as “T” (Track and Jump) or “F” (Field) based on which event they are competing in, followed by a number that represents impairment type and level of impairment. For example, T12. First Letter Represents: First Number Represents: Second Number Represents: T/F TRACK OR FIELD 1-6 IMPAIRMENT TYPE 1-8 DESCRIPTION OF IMPAIRMENT Typically T identifies a track 1 = Visual Impairment The number 1 through 8 specifies event and F for a field event. 2 = Intellectual Impairment the description of the impairment as There are certain exceptions 3 = Co-ordination Impairment per the classification rules (i.e. Long Jump is a T event) 4 = Upper Limb Deficiencies; Lower Limb Deficiencies without the use of prosthetic; short stature 5 = Impaired muscle power or range of movement 6 = Limb deficiencies with the use of prosthetic PHYSICAL IMPAIRMENT SHORT STATURE F40 F41 IMPAIRED MUSCLE POWER AND/OR PASSIVE RANGE OF MOVEMENT T/F51 T/F52 T/F53 T/F54 F55 F56 F57 Athletes who compete seated LIMB DEFICIENCY T/F42 T/F43 T/F44 T/F62 T/F63 T/F64 T/F45 T/F46 T/47 Lower limb deficiency without Lower limb deficiency with Upper limb deficiency the use of a prosthetic the use of a prosthetic with or without the use of a prosthetic ATHLETES WITH ATHETOSIS, ATAXIA AND/OR -

VMAA-Performance-Sta

Revised June 18, 2019 U.S. Department of Veterans Affairs (VA) Veteran Monthly Assistance Allowance for Disabled Veterans Training in Paralympic and Olympic Sports Program (VMAA) In partnership with the United States Olympic Committee and other Olympic and Paralympic entities within the United States, VA supports eligible service and non-service-connected military Veterans in their efforts to represent the USA at the Paralympic Games, Olympic Games and other international sport competitions. The VA Office of National Veterans Sports Programs & Special Events provides a monthly assistance allowance for disabled Veterans training in Paralympic sports, as well as certain disabled Veterans selected for or competing with the national Olympic Team, as authorized by 38 U.S.C. 322(d) and Section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program, VA will pay a monthly allowance to a Veteran with either a service-connected or non-service-connected disability if the Veteran meets the minimum military standards or higher (i.e. Emerging Athlete or National Team) in his or her respective Paralympic sport at a recognized competition. In addition to making the VMAA standard, an athlete must also be nationally or internationally classified by his or her respective Paralympic sport federation as eligible for Paralympic competition. VA will also pay a monthly allowance to a Veteran with a service-connected disability rated 30 percent or greater by VA who is selected for a national Olympic Team for any month in which the Veteran is competing in any event sanctioned by the National Governing Bodies of the Olympic Sport in the United State, in accordance with P.L. -

Alpine Soil Bacterial Community and Environmental Filters Bahar Shahnavaz

Alpine soil bacterial community and environmental filters Bahar Shahnavaz To cite this version: Bahar Shahnavaz. Alpine soil bacterial community and environmental filters. Other [q-bio.OT]. Université Joseph-Fourier - Grenoble I, 2009. English. tel-00515414 HAL Id: tel-00515414 https://tel.archives-ouvertes.fr/tel-00515414 Submitted on 6 Sep 2010 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. THÈSE Pour l’obtention du titre de l'Université Joseph-Fourier - Grenoble 1 École Doctorale : Chimie et Sciences du Vivant Spécialité : Biodiversité, Écologie, Environnement Communautés bactériennes de sols alpins et filtres environnementaux Par Bahar SHAHNAVAZ Soutenue devant jury le 25 Septembre 2009 Composition du jury Dr. Thierry HEULIN Rapporteur Dr. Christian JEANTHON Rapporteur Dr. Sylvie NAZARET Examinateur Dr. Jean MARTIN Examinateur Dr. Yves JOUANNEAU Président du jury Dr. Roberto GEREMIA Directeur de thèse Thèse préparée au sien du Laboratoire d’Ecologie Alpine (LECA, UMR UJF- CNRS 5553) THÈSE Pour l’obtention du titre de Docteur de l’Université de Grenoble École Doctorale : Chimie et Sciences du Vivant Spécialité : Biodiversité, Écologie, Environnement Communautés bactériennes de sols alpins et filtres environnementaux Bahar SHAHNAVAZ Directeur : Roberto GEREMIA Soutenue devant jury le 25 Septembre 2009 Composition du jury Dr. -

Taeguturn Section

T1 I TURNING I TAEGUTHREAD PAGE T1 PAGE T176 T2 I T-CLAMP I T-CAP I TECHNICAL INDEX PAGE T224 PAGE T328 INFORMATION PAGE T362 PAGE T346 T3 T4 T5 TaeguTurn Program T8 User Guide Grades T12 Chipbreakers T16 Trouble Shooting T22 Insert Selection for Cast Iron Materials T25 Insert Geometry for Workpiece Shape T26 Insert Selection & Recommended Cutting Parameters T27 TaeguTurn Inserts Designation System T36 Negative Inserts T38 Negative KNUX Type Inserts T54 Positive Inserts T75 Inserts for Pipe Skiving T90 Inserts for Aluminum T91 Ceramic Inserts T97 CBN Inserts T106 PCD Inserts T112 T6 TaeguTurn External Toolholders & Boring Bars T117 Designation System for External Toolholders T118 Toolholder Clamping System T120 Top Clamp/External Turning Toolholders T123 Multi Lock/External Turning Toolholders T127 Screw Clamp/External Turning Toolholders T134 T-Holders - External Turning T141 Top Clamp/External Toolholders for CBN & Ceramic Inserts T150 T-Holders - External Turning for Ceramic Dimple Inserts T154 Designation System for Boring Bars T158 Top Clamp/Boring Bars T159 Multi Lock/Boring Bars T160 Lever Lock/Boring Bars T163 Screw Clamp/Boring Bars T164 T-Holders - Internal Turning T173 T-Holders - Internal Turning for Ceramic Dimple Inserts T175 T7 I TAEGUTURN PROGRAM TURNING INSERTS WS WT FA For Inserts see pages For Inserts see pages For Inserts see pages CNMG T50 CNMA T42 CNMG T45 CNMG T50 DNMG T57 DNMG T53 WNMG T78 CCMT T80 FG MC SF For Inserts see pages For Inserts see pages For Inserts see pages CNMG T45 CNMG T46 CNMG T49 DNMG T54 DNMG -

View of the Algorithm Will Be Discussed Below to Summarize the Key Points of the Algorithm

EFFECTIVE NONLINEAR SUSCEPTIBILITIES OF METAL-INSULATOR AND METAL-INSULATOR-METAL NANOLAYERED STRUCTURES Dissertation Submitted to The School of Engineering of the UNIVERSITY OF DAYTON In Partial Fulfillment of the Requirements for The Degree of Doctor of Philosophy in Electro-Optics By Mallik Mohd Raihan Hussain Dayton, Ohio May, 4242 EFFECTIVE NONLINEAR SUSCEPTIBILITIES OF METAL-INSULATOR AND METAL-INSULATOR-METAL NANOLAYERED STRUCTURES Name: Hussain, Mallik Mohd Raihan APPROVED BY: Imad Agha, Ph.D. Andrew Sarangan, Ph.D. Advisory Committee Chairman Committee Member Associate Professor, Department of Professor, Department of Physics, and, Department of Electro- Electro-Optics and Photonics Optics and Photonics Partha Banerjee, Ph.D. Michael Scalora, Ph.D. Committee Member Committee Member Professor and Department Chair, Research Physicist, Charles M. Department of Electro-Optics and Bowden Research Facility, Photonics AMRDEC, US Army RDECOM Robert J. Wilkens, Ph.D., P.E. Eddy M. Rojas, Ph.D., M.A., P.E. Associate Dean for Research Dean, School of Engineering and Innovation Professor, School of Engineering ii © Copyright by Mallik Mohd Raihan Hussain All rights reserved 4242 ABSTRACT EFFECTIVE NONLINEAR SUSCEPTIBILITIES OF METAL-INSULATOR AND METAL-INSULATOR-METAL NANOLAYERED STRUCTURES Name: Hussain, Mallik Mohd Raihan University of Dayton Advisor: Dr. Imad Agha Nonlinear electromagnetic radiation (second and third harmonic) from the metal-insulator and metal-insulator-metal structures were measured and compared against predictions from the hydrodynamic models of plasmonics. This model incorporated higher order terms stem- ming from electron tunneling and nonlocality. This study shows that, besides the linear optical parameter like permittivity, conductivity etc, changes in the nonlinear optical pa- rameters, namely, second and third order susceptibilities (χ(2) and χ(3), respectively) can also be used to probe and compare the higher-order terms of the hydrodynamic model of plasmonics. -

Petitioner's Exhibit 17

JURC PETITIONER'S EXHIBIT 0.~~.....L--- Petitioner's Exhibit 17 7 TOWN OF CEDAR LAKE Preliminary Engineering Report Cedar Lake Water Utility System Improvements July 2020 Prepared by: !,?.!! !!e.!,~JI ~ •• !.'!!; ru.E.~~ ~ Ph: (219) 844 8680 • Fax: (219) 844 7754 · e-mail: [email protected] Your Vision • Our Focus Table of Contents 1. Project Location ............................................................................................................................................ 6 2. Current Needs ............................................................................................................................................... 6 2.1. Existing System ...................................................................................................................................... 6 2.1.a. Distribution System ....................................................................................................................... 6 2.1.b. Supply System ............................................................................................................................... 7 2.1.c. Storage System ............................................................................................................................. 8 2.1.d. Treatment Systems ....................................................................................................................... 8 2.1.e. Document Needs ......................................................................................................................... -

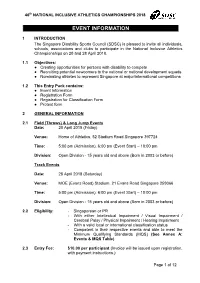

Event Information

46th NATIONAL INCLUSIVE ATHLETICS CHAMPIONSHIPS 2018 EVENT INFORMATION 1 INTRODUCTION The Singapore Disability Sports Council (SDSC) is pleased to invite all individuals, schools, associations and clubs to participate in the National Inclusive Athletics Championships on 20 and 28 April 2018. 1.1 Objectives: ● Creating opportunities for persons with disability to compete ● Recruiting potential newcomers to the national or national development squads ● Nominating athletes to represent Singapore at major/international competitions 1.2 This Entry Pack contains: ● Event Information ● Registration Form ● Registration for Classification Form ● Protest form 2 GENERAL INFORMATION 2.1 Field (Throws) & Long Jump Events Date: 20 April 2018 (Friday) Venue: Home of Athletics. 52 Stadium Road Singapore 397724 Time: 5:00 pm (Admission). 6:00 pm (Event Start) – 10:00 pm Division: Open Division - 15 years old and above (Born in 2003 or before) Track Events Date: 28 April 2018 (Saturday) Venue: MOE (Evans Road) Stadium. 21 Evans Road Singapore 259366 Time: 5:00 pm (Admission). 6:00 pm (Event Start) – 10:00 pm Division: Open Division - 15 years old and above (Born in 2003 or before) 2.2 Eligibility: - Singaporean or PR - With either Intellectual Impairment / Visual Impairment / Cerebral Palsy / Physical Impairment / Hearing Impairment - With a valid local or international classification status - Competent in their respective events and able to meet the Minimum Qualifying Standards (MQS) (See Annex A: Events & MQS Table) 2.3 Entry Fee: $10.00 per participant (Invoice will be issued upon registration, with payment instructions.) Page 1 of 12 46th NATIONAL INCLUSIVE ATHLETICS CHAMPIONSHIPS 2018 2.4 Registration 23rd March 2018 Deadline: Email completed forms to [email protected]. -

SECURITY COUNCIL COMMITTEE ESTABLISHED in PURSUANCE of RESOLUTION 253 (1968) CONCERNING the QUESTION of SOUTHERN Rhcldesia SECURITYCOUNCIL OFFICIALRECORDS

SIXTH REPORT OF THE SECURITY COUNCIL COMMITTEE ESTABLISHED IN PURSUANCE OF RESOLUTION 253 (1968) CONCERNING THE QUESTION OF SOUTHERN RHClDESIA SECURITYCOUNCIL OFFICIALRECORDS TWENTY-NINTH YEAR SPECIAL SUPPLEMENT No. 2A UNITED NATIONS annex Vi. eppendlx III SIXTH REPORT OF THE SECURITY COUNCIL COMMITTEE ESTABLISHED IN PURSUANCE OF RESOLUTION 263 (lB68) CONCERNING THE QUESTION OF SOUTHERN RHODESIA SECURITYCOUNCIL OFFICIALRECORQS TWENTY-NINTH YEAR SPECIAL SUPPLEMENT No. 2A UNITED NATIONS New York, 1974 NOTE Symbola of United Nations documenh an? composed of cvpftalbttm combined wfth &~rss. Mention of such a symbol indicates a reference to a United Nations doewnent. Documentaof the SecurityCouncll(symbo1 S/. .) arenormally published in quartsrly Slrpplements of fha Offi& Records of the Secur&v Council Thedate of thedocument indicatesthe aupplemnt in whichit appearsor in whichinformation about it iagiven. The maolutioncof the SecurityCouncil, numbered tn accordancewith a system adoptedin 1964,am publinhed in yearlyvolunws of Resolutionr and DeciAwts of the &cur@ CacncN.The new system, which has bean applied retroactively to ~saolution~ adoptedbefore 1 January1965, became fully operativeon that data. Sfiii70lRev.i m(rx VI, appendixIII I I e The sixth report of the Security Council Committee established in pursuance of resolution 253 (1968) concerning the question of Southern Rhodesia is published as Special Supplement No. 2. The present Supplement contains the tables entitled "Trade in commodities", issued aa annex VI, appdndfx III, to the above report. The tables are issued in the form in which they were presented to the Committee and the Council. NOTE: A DASH (-) INDICATES NIL, LESS THAN $US 1,000, OR FIGURES NOT AVAILABLE. -iii- AFRICA EUROPE LIT4fR ____-_--_--____-_---_--__-_______---_-___-_____~___ I)ESlLUI I YESTRY ASIA SOUTMRY S.AFR. -

Athletics Classification Rules and Regulations 2

IPC ATHLETICS International Paralympic Committee Athletics Classifi cation Rules and Regulations January 2016 O cial IPC Athletics Partner www.paralympic.org/athleticswww.ipc-athletics.org @IPCAthletics ParalympicSport.TV /IPCAthletics Recognition Page IPC Athletics.indd 1 11/12/2013 10:12:43 Purpose and Organisation of these Rules ................................................................................. 4 Purpose ............................................................................................................................... 4 Organisation ........................................................................................................................ 4 1 Article One - Scope and Application .................................................................................. 6 International Classification ................................................................................................... 6 Interpretation, Commencement and Amendment ................................................................. 6 2 Article Two – Classification Personnel .............................................................................. 8 Classification Personnel ....................................................................................................... 8 Classifier Competencies, Qualifications and Responsibilities ................................................ 9 3 Article Three - Classification Panels ................................................................................ 11 4 Article Four