3. Verilog Hardware Description Language

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

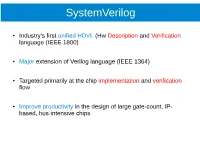

Systemverilog

SystemVerilog ● Industry's first unified HDVL (Hw Description and Verification language (IEEE 1800) ● Major extension of Verilog language (IEEE 1364) ● Targeted primarily at the chip implementation and verification flow ● Improve productivity in the design of large gate-count, IP- based, bus-intensive chips Sources and references 1. Accellera IEEE SystemVerilog page http://www.systemverilog.com/home.html 2. “Using SystemVerilog for FPGA design. A tutorial based on a simple bus system”, Doulos http://www.doulos.com/knowhow/sysverilog/FPGA/ 3. “SystemVerilog for Design groups”, Slides from Doulos training course 4. Various tutorials on SystemVerilog on Doulos website 5. “SystemVerilog for VHDL Users”, Tom Fitzpatrick, Synopsys Principal Technical Specialist, Date04 http://www.systemverilog.com/techpapers/date04_systemverilog.pdf 6. “SystemVerilog, a design and synthesis perspective”, K. Pieper, Synopsys R&D Manager, HDL Compilers 7. Wikipedia Extensions to Verilog ● Improvements for advanced design requirements – Data types – Higher abstraction (user defined types, struct, unions) – Interfaces ● Properties and assertions built in the language – Assertion Based Verification, Design for Verification ● New features for verification – Models and testbenches using object-oriented techniques (class) – Constrained random test generation – Transaction level modeling ● Direct Programming Interface with C/C++/SystemC – Link to system level simulations Data types: logic module counter (input logic clk, ● Nets and Variables reset, ● enable, Net type, -

Development of Systemc Modules from HDL for System-On-Chip Applications

University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange Masters Theses Graduate School 8-2004 Development of SystemC Modules from HDL for System-on-Chip Applications Siddhartha Devalapalli University of Tennessee - Knoxville Follow this and additional works at: https://trace.tennessee.edu/utk_gradthes Part of the Electrical and Computer Engineering Commons Recommended Citation Devalapalli, Siddhartha, "Development of SystemC Modules from HDL for System-on-Chip Applications. " Master's Thesis, University of Tennessee, 2004. https://trace.tennessee.edu/utk_gradthes/2119 This Thesis is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. To the Graduate Council: I am submitting herewith a thesis written by Siddhartha Devalapalli entitled "Development of SystemC Modules from HDL for System-on-Chip Applications." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the equirr ements for the degree of Master of Science, with a major in Electrical Engineering. Dr. Donald W. Bouldin, Major Professor We have read this thesis and recommend its acceptance: Dr. Gregory D. Peterson, Dr. Chandra Tan Accepted for the Council: Carolyn R. Hodges Vice Provost and Dean of the Graduate School (Original signatures are on file with official studentecor r ds.) To the Graduate Council: I am submitting herewith a thesis written by Siddhartha Devalapalli entitled "Development of SystemC Modules from HDL for System-on-Chip Applications". -

Lattice Synthesis Engine User Guide and Reference Manual

Lattice Synthesis Engine for Diamond User Guide April, 2019 Copyright Copyright © 2019 Lattice Semiconductor Corporation. All rights reserved. This document may not, in whole or part, be reproduced, modified, distributed, or publicly displayed without prior written consent from Lattice Semiconductor Corporation (“Lattice”). Trademarks All Lattice trademarks are as listed at www.latticesemi.com/legal. Synopsys and Synplify Pro are trademarks of Synopsys, Inc. Aldec and Active-HDL are trademarks of Aldec, Inc. All other trademarks are the property of their respective owners. Disclaimers NO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS “AS IS” WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN THIS DOCUMENT, EVEN IF LATTICE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU. Lattice may make changes to these materials, specifications, or information, or to the products described herein, at any time without notice. Lattice makes no commitment to update this documentation. Lattice reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors contained herein or to advise any user of this document of any correction if such be made. -

Version Control Friendly Project Management System for FPGA Designs

Copyright 2016 Society of Photo-Optical Instrumentation Engineers. This paper was published in Proceedings of SPIE (Proc. SPIE Vol. 10031, 1003146, DOI: http://dx.doi.org/10.1117/12.2247944 ) and is made available as an electronic reprint (preprint) with permission of SPIE. One print or electronic copy may be made for personal use only. Systematic or multiple reproduction, distribution to multiple locations via electronic or other means, duplication of any material in this paper for a fee or for com- mercial purposes, or modification of the content of the paper are prohibited. 1 Version control friendly project management system for FPGA designs Wojciech M. Zabołotnya aInstitute of Electronic Systems, Warsaw University of Technology, ul. Nowowiejska 15/19, 00-665 Warszawa, Poland ABSTRACT In complex FPGA designs, usage of version control system is a necessity. It is especially important in the case of designs developed by many developers or even by many teams. The standard development mode, however, offered by most FPGA vendors is the GUI based project mode. It is very convenient for a single developer, who can easily experiment with project settings, browse and modify the sources hierarchy, compile and test the design. Unfortunately, the project configuration is stored in files which are not suited for use with Version Control System (VCS). Another important problem in big FPGA designs is reuse of IP cores. Even though there are standard solutions like IEEE 1685-2014, they suffer from some limitations particularly significant for complex systems (e.g. only simple types are allowed for IP-core ports, it is not possible to use parametrized instances of IP-cores). -

(System)Verilog to Chisel Translation for Faster Hardware Design Jean Bruant, Pierre-Henri Horrein, Olivier Muller, Tristan Groleat, Frédéric Pétrot

(System)Verilog to Chisel Translation for Faster Hardware Design Jean Bruant, Pierre-Henri Horrein, Olivier Muller, Tristan Groleat, Frédéric Pétrot To cite this version: Jean Bruant, Pierre-Henri Horrein, Olivier Muller, Tristan Groleat, Frédéric Pétrot. (System)Verilog to Chisel Translation for Faster Hardware Design. 2020 31th International Symposium on Rapid System Prototyping (RSP), Sep 2020, VIrtual Conference, France. hal-02949112 HAL Id: hal-02949112 https://hal.archives-ouvertes.fr/hal-02949112 Submitted on 25 Sep 2020 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. (System)Verilog to Chisel Translation for Faster Hardware Design Jean Bruant∗;y, Pierre-Henri Horreinz, Olivier Mullery, Tristan Groleat´ x and Fred´ eric´ Petrot´ y OVHcloud, ∗Paris, zLyon, xBrest, France yUniv. Grenoble Alpes, CNRS, Grenoble INP1, TIMA, Grenoble, France Abstract—Bringing agility to hardware developments has been target, we also successfully use it into our production FPGA- a long-running goal for hardware communities struggling with based network functions at OVHcloud. limitations of current hardware description languages such as (System)Verilog or VHDL. The numerous recent Hardware Chisel introduces many features and concepts intended Construction Languages such as Chisel are providing enhanced to improve hardware design efficiency which are especially ways to design complex hardware architectures with notable useful for the design of complex IPs and in large projects. -

Managing Quartus II Projects 1 2013.11.4

Managing Quartus II Projects 1 2013.11.4 QII52012 Subscribe Send Feedback The Quartus II software organizes and manages the elements of your design within a project. The project encapsulates information about your design hierarchy, libraries, constraints, and project settings. Click File > New Project Wizard to quickly create a new project and specify basic project settings When you open a project, a unified GUI displays integrated project information. The Project Navigator allows you to view and edit the elements of your project. The Messages window lists important information about project processing. You can save multiple revisions of your project to experiment with settings that achieve your design goals. Quartus II projects support team-based, distributed work flows and a scripting interface. Quick Start To quickly create a project and specify basic settings, click File > New Project Wizard. © 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at ISO www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with 9001:2008 Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes Registered no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. -

Elemapprox -- the Rosetta Stone of Elementary Functions Approximation and Plotting

elemapprox -- The Rosetta stone of elementary functions approximation and plotting Going back to my HDL development/design projects, I’ve been having fun work- ing with elemapprox, a multi-language collection of modules and packages to assist in simulating floating-point hardware. It is kind of a Rosetta stone for elementary func- tions approximation adding basic plotting facilities as ASCII (low-resolution) and PBM (monochrome) bitmaps (higher res). Available ports include ANSI C, Verilog, VHDL and "VHDLIEEE" (perusing the existing approximations in the IEEE.math_real pack- age). The data type used for the computations is Verilog’s and VHDL’s real. This code has been tested with Icarus Verilog, GHDL and Modelsim (VHDL only). The Verilog driver module (testfunc.v) makes advanced use of Verilog system functions and tasks. By using this strong feature of Verilog, I was able to closely imitate the operation of the driver code (testfunc.c) from the ANSI C version. Development of the test driver for the VHDL version was not that straightforward and had to bypass some VHDL quirks; for instance the handling of variable-length strings. The complete code is here: http://github.com/nkkav/elemapprox and is licensed under the Modified BSD license. My motivation was to extend the original work on evaluating (single-precision) and plotting transcendental functions as discussed in Prof. Mark G. Arnold’s HDLCON 2001 paper. At this point my version adds support for all trigonometric (cyclic), inverse trigono- metric, hyperbolic and inverse hyperbolic functions as well as a few others: exp, log (ln), log2, log10, pow. I will be adding more functions in the future, for instance hypot, cbrt (cubic root) as well as other special functions that are of interest. -

Hardware Description Languages Compared: Verilog and Systemc

Hardware Description Languages Compared: Verilog and SystemC Gianfranco Bonanome Columbia University Department of Computer Science New York, NY Abstract This library encompasses all of the necessary components required to transform C++ into a As the complexity of modern digital systems hardware description language. Such additions increases, engineers are now more than ever include constructs for concurrency, time notion, integrating component modeling by means of communication, reactivity and hardware data hardware description languages (HDLs) in the types. design process. The recent addition of SystemC to As described by Edwards [1], VLSI an already competitive arena of HDLs dominated verification involves an initial simulation done in by Verilog and VHDL, calls for a direct C or C++, usually for proof of concept purposes, comparison to expose potential advantages and followed by translation into an HDL, simulation of flaws of this newcomer. This paper presents such the model, applying appropriate corrections, differences and similarities, specifically between hardware synthesization and further iterative Verilog and SystemC, in effort to better categorize refinement. SystemC is able to shorten this the scopes of the two languages. Results are based process by combining the first two steps. on simulation conducted in both languages, for a Consequently, this also decreases time to market model with equal specifications. for a manufacturer. Generally a comparison between two computer languages is based on the number of Introduction lines of code and execution time required to achieve a specific task, using the two languages. A Continuous advances in circuit fabrication number of additional parameters can be observed, technology have augmented chip density, such as features, existence or absence of constructs consequently increasing device complexity. -

Timing, Testbenches and More Advanced Verilog

Department of Computer Science and Electrical Engineering CMPE 415 Parameterized Modules and Simulation Prof. Ryan Robucci ParametersParameters Modules may include parameters that can be overridden for tuning behavior and facilitating code reuse module pdff(q,d,clk,arst); parameter size=1, resetval=0; output [size-1:0] q; input [size-1:0] d; input clk,arst; always @(posedge clk, posedge arst) if (arst) q<=resetval; else q <= d; endmodule Overriding the parameters in the module instantiation is optional and may be provided by an ordered list or named list: pdff I1 (.q(ur1q), .d(u1d), .clk(clk),.arst(rst)); pdff #(.size(8),.resetval(128)) I2 (.q(ur8q), .d(u8d), .clk(clk), .arst(rst)); pdff #(8,128) I3 (.q(ur8q), .d(u8d), .clk(clk), .arst(rst)); pdff #(.size( ),.resetval(1) ) I4 (.q(ur1q), .d(u1d), .clk(clk),.arst(rst)); Overriding the parameters can also be done with the keyword defparam and the hierarchical name. pdff I2 (.q(ur8q), .d(u8d), .clk(clk), .arst(rst)); defparam I2.size = 8; defparam I2.resetval = 128; This can also be useful for overriding parameters for simulation from the testbench: defparam topDUT.comModule1.uart2.BAUD_RATE = 100; Local parameters cannot be overridden directly from the instantiation, but they can depend on other parameters. Use keyword localparam module pdff(q,d,clk,arst); parameter size=1, resetval=0; localparam msb=size-1; output [msb:0] q; input [msb:0] d; input clk,arst; reg [msb:0] out; always @(posedge clk, posedge arst) if (arst) q<=resetval; else q <= d; endmodule ParametrizedParametrized SimulationSimulation ModelsModels Parametrization modules are useful for creating simulation for simulation that takes much less time to simulate, involves minimal differences from the code used for hardware, and maintains high functional test coverage. -

Introduction to Verilog

9 Introduction to Verilog Table of Contents 1. Introduction . 1 2. Lexical Tokens . 2 White Space, Comments, Numbers, Identifiers, Operators, Verilog Keywords 3. Gate-Level Modelling . 3 Basic Gates, buf, not Gates, Three-State Gates; bufif1, bufif0, notif1, notif0 4. Data Types . 4 Value Set, Wire, Reg, Input, Output, Inout Integer, Supply0, Supply1 Time, Parameter 5. Operators . 6 Arithmetic Operators, Relational Operators, Bit-wise Operators, Logical Operators Reduction Operators, Shift Operators, Concatenation Operator, Conditional Operator: “?” Operator Precedence 6. Operands . 9 Literals, Wires, Regs, and Parameters, Bit-Selects “x[3]” and Part-Selects “x[5:3]” Function Calls 7. Modules. 10 Module Declaration, Continuous Assignment, Module Instantiations, Parameterized Modules 8. Behavioral Modeling . 12 Procedural Assignments, Delay in Assignment, Blocking and Nonblocking Assignments begin ... end, for Loops, while Loops, forever Loops, repeat, disable, if ... else if ... else case, casex, casez 9. Timing Controls . 17 Delay Control, Event Control, @, Wait Statement, Intra-Assignment Delay 10. Procedures: Always and Initial Blocks . 18 Always Block, Initial Block 11. Functions . 19 Function Declaration, Function Return Value, Function Call, Function Rules, Example 12. Tasks . 21 13. Component Inference . 22 Registers, Flip-flops, Counters, Multiplexers, Adders/Subtracters, Tri-State Buffers Other Component Inferences 14. Finite State Machines . 24 Counters, Shift Registers 15. Compiler Directives. 26 Time Scale, Macro Definitions, Include Directive 16. System Tasks and Functions . 27 $display, $strobe, $monitor $time, $stime, $realtime, $reset, $stop, $finish $deposit, $scope, $showscope, $list 17. Test Benches . 29 Synchronous Test Bench Introduction to Verilog Friday, January 05, 2001 9:34 pm Peter M. Nyasulu Introduction to Verilog 1. Introduction Verilog HDL is one of the two most common Hardware Description Languages (HDL) used by integrated circuit (IC) designers. -

Development of VITAL - Compliant VHDL Models for Functionally Complex Devices

Development of VITAL - compliant VHDL models for functionally complex devices A.Poliakov, A.Sokhatski, SEVA Technologies, Inc. The paper is based on the development experience of VITAL level 0 compliant VHDL models of IDT FIFO memory family IC for the Free Model Foundation (FMF) [http://vhdl.org/fmf/]. The source data for the development was Integrated Device Technology (IDT) datasheets including timing parameters, VITAL specification, the FMF Guide Lines for VHDL VITAL models. Timing data was prepared in the SDF files. The paper dwells upon approaches and examples of describing functionally complex devices in VITAL standard. Introduction Let us try to imagine a bright future: a certain chip manufacturer, for example, IDT, manufacturer of memory chips, provides every new developed chip with documentation containing behavioral VHDL and Verilog models which precisely reflect both functionality and timing characteristics of a chip. This models will use the standard format of timing data presentation (the SDF) and corresponding HDL standards as VITAL VHDL. It would give the following advantages to engineers who apply the chips: 1) Behavioral level of the model ensures speedy board simulation. 2) Precise timing data ensures quality verification. 3) The standard timing data format ensures simplicity of uniting timing data and exchange with various tools. 4) The models can be used for research of chip behavior which have been incompletely reflected in the informal documentation (as datasheets). VITAL consists of the following standardized parts: 1) SDF to VHDL mapping specification 2) Model style constraints and development methodology 3) Timing routines 4) Primitive (AND, OR,…) timing models Until now VITAL standard was mostly used for functionally simple IC. -

Composition Semantics of the Rosetta Specification Language

Composition Semantics of the Rosetta Specification Language BY c 2012 Megan E. Peck Submitted to the graduate degree program in Electrical Engineering & Computer Science and the Graduate Faculty of the University of Kansas in partial fulfillment of the requirements for the degree of Master of Science. Chairperson Dr. Perry Alexander Dr. Andy Gill Dr. Prasad Kulkarni Date Defended: August 30, 2012 The Thesis Committee for Megan E. Peck certifies that this is the approved version of the following thesis: Composition Semantics of the Rosetta Specification Language Chairperson Dr. Perry Alexander Date Approved: ii Abstract The Rosetta specification language aims to enable system designers to abstractly design complex heterogeneous systems. To this end, Rosetta allows for compositional design to facilitate modularity, separation of concerns, and specification reuse. The behavior of Rosetta components and facets can be viewed as systems, which are well suited for coalgebraic denotation. The previous semantics of Rosetta lacked detail in the denotational work, and had no firm semantic basis for the composition operators. This thesis refreshes previous work on the coalgebraic denotation of Rosetta. It then goes on to define the denotation of the composition operators. A real-world Rosetta example using all types of composition serves as a demonstration of the power of composition as well as the clean, modular abstractness it affords the designer. iii Acknowledgements This thesis may be a long time coming, but that is not for lack of support. I first must thank my husband, Wesley. You’ve encouraged me from before I even thought I could do grad school, up to the very end, and have had more faith in me than I have had in myself.