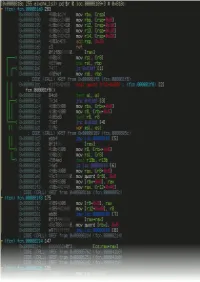

A Crash Course in X86 Disassembly

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

AMD Athlon™ Processor X86 Code Optimization Guide

AMD AthlonTM Processor x86 Code Optimization Guide © 2000 Advanced Micro Devices, Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD’s products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other applica- tion in which the failure of AMD’s product could create a situation where per- sonal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice. Trademarks AMD, the AMD logo, AMD Athlon, K6, 3DNow!, and combinations thereof, AMD-751, K86, and Super7 are trademarks, and AMD-K6 is a registered trademark of Advanced Micro Devices, Inc. Microsoft, Windows, and Windows NT are registered trademarks of Microsoft Corporation. -

Fill Your Boots: Enhanced Embedded Bootloader Exploits Via Fault Injection and Binary Analysis

IACR Transactions on Cryptographic Hardware and Embedded Systems ISSN 2569-2925, Vol. 2021, No. 1, pp. 56–81. DOI:10.46586/tches.v2021.i1.56-81 Fill your Boots: Enhanced Embedded Bootloader Exploits via Fault Injection and Binary Analysis Jan Van den Herrewegen1, David Oswald1, Flavio D. Garcia1 and Qais Temeiza2 1 School of Computer Science, University of Birmingham, UK, {jxv572,d.f.oswald,f.garcia}@cs.bham.ac.uk 2 Independent Researcher, [email protected] Abstract. The bootloader of an embedded microcontroller is responsible for guarding the device’s internal (flash) memory, enforcing read/write protection mechanisms. Fault injection techniques such as voltage or clock glitching have been proven successful in bypassing such protection for specific microcontrollers, but this often requires expensive equipment and/or exhaustive search of the fault parameters. When multiple glitches are required (e.g., when countermeasures are in place) this search becomes of exponential complexity and thus infeasible. Another challenge which makes embedded bootloaders notoriously hard to analyse is their lack of debugging capabilities. This paper proposes a grey-box approach that leverages binary analysis and advanced software exploitation techniques combined with voltage glitching to develop a powerful attack methodology against embedded bootloaders. We showcase our techniques with three real-world microcontrollers as case studies: 1) we combine static and on-chip dynamic analysis to enable a Return-Oriented Programming exploit on the bootloader of the NXP LPC microcontrollers; 2) we leverage on-chip dynamic analysis on the bootloader of the popular STM8 microcontrollers to constrain the glitch parameter search, achieving the first fully-documented multi-glitch attack on a real-world target; 3) we apply symbolic execution to precisely aim voltage glitches at target instructions based on the execution path in the bootloader of the Renesas 78K0 automotive microcontroller. -

Radare2 Book

Table of Contents introduction 1.1 Introduction 1.2 History 1.2.1 Overview 1.2.2 Getting radare2 1.2.3 Compilation and Portability 1.2.4 Compilation on Windows 1.2.5 Command-line Flags 1.2.6 Basic Usage 1.2.7 Command Format 1.2.8 Expressions 1.2.9 Rax2 1.2.10 Basic Debugger Session 1.2.11 Contributing to radare2 1.2.12 Configuration 1.3 Colors 1.3.1 Common Configuration Variables 1.3.2 Basic Commands 1.4 Seeking 1.4.1 Block Size 1.4.2 Sections 1.4.3 Mapping Files 1.4.4 Print Modes 1.4.5 Flags 1.4.6 Write 1.4.7 Zoom 1.4.8 Yank/Paste 1.4.9 Comparing Bytes 1.4.10 Visual mode 1.5 Visual Disassembly 1.5.1 2 Searching bytes 1.6 Basic Searches 1.6.1 Configurating the Search 1.6.2 Pattern Search 1.6.3 Automation 1.6.4 Backward Search 1.6.5 Search in Assembly 1.6.6 Searching for AES Keys 1.6.7 Disassembling 1.7 Adding Metadata 1.7.1 ESIL 1.7.2 Scripting 1.8 Loops 1.8.1 Macros 1.8.2 R2pipe 1.8.3 Rabin2 1.9 File Identification 1.9.1 Entrypoint 1.9.2 Imports 1.9.3 Symbols (exports) 1.9.4 Libraries 1.9.5 Strings 1.9.6 Program Sections 1.9.7 Radiff2 1.10 Binary Diffing 1.10.1 Rasm2 1.11 Assemble 1.11.1 Disassemble 1.11.2 Ragg2 1.12 Analysis 1.13 Code Analysis 1.13.1 Rahash2 1.14 Rahash Tool 1.14.1 Debugger 1.15 3 Getting Started 1.15.1 Registers 1.15.2 Remote Access Capabilities 1.16 Remoting Capabilities 1.16.1 Plugins 1.17 Plugins 1.17.1 Crackmes 1.18 IOLI 1.18.1 IOLI 0x00 1.18.1.1 IOLI 0x01 1.18.1.2 Avatao 1.18.2 R3v3rs3 4 1.18.2.1 .intro 1.18.2.1.1 .radare2 1.18.2.1.2 .first_steps 1.18.2.1.3 .main 1.18.2.1.4 .vmloop 1.18.2.1.5 .instructionset 1.18.2.1.6 -

Reverse Software Engineering As a Project-Based Learning Tool

Paper ID #33764 Reverse Software Engineering as a Project-Based Learning Tool Ms. Cynthia C. Fry, Baylor University CYNTHIA C. FRY is currently a Senior Lecturer of Computer Science at Baylor University. She worked at NASA’s Marshall Space Flight Center as a Senior Project Engineer, a Crew Training Manager, and the Science Operations Director for STS-46. She was an Engineering Duty Officer in the U.S. Navy (IRR), and worked with the Naval Maritime Intelligence Center as a Scientific/Technical Intelligence Analyst. She was the owner and chief systems engineer for Systems Engineering Services (SES), a computer systems design, development, and consultation firm. She joined the faculty of the School of Engineering and Computer Science at Baylor University in 1997, where she teaches a variety of engineering and computer science classes, she is the Faculty Advisor for the Women in Computer Science (WiCS), the Director of the Computer Science Fellows program, and is a KEEN Fellow. She has authored and co- authored over fifty peer-reviewed papers. Mr. Zachary Michael Steudel Zachary Steudel is a 2021 graduate of Baylor University’s computer science department. In his time at Baylor, he worked as a Teaching Assistant under Ms. Cynthia C. Fry. As part of the Teaching Assistant role, Zachary designed and created the group project for the Computer Systems course. Zachary Steudel worked as a Software Developer Intern at Amazon in the Summer of 2019, a Software Engineer Intern at Microsoft in the Summer of 2020, and begins his full-time career with Amazon in the summer of 2021 as a software engineer. -

Reassembleable Disassembling

Reassembleable Disassembling Shuai Wang, Pei Wang, and Dinghao Wu College of Information Sciences and Technology The Pennsylvania State University fszw175, pxw172, [email protected] Abstract struction level to enforce certain security policies. To ensure program control-flow integrity (CFI, meaning that Reverse engineering has many important applications in program execution is dictated to a predetermined control- computer security, one of which is retrofitting software flow graph) [1,4, 43, 17, 29, 37] without source code, the for safety and security hardening when source code is not original control-flow graph must be recovered from a bi- available. By surveying available commercial and aca- nary executable and the binary must be retrofitted with demic reverse engineering tools, we surprisingly found the CFI enforcement facility embedded [50, 49]. Sym- that no existing tool is able to disassemble executable bolic taint analysis [34] on binaries must recover assem- binaries into assembly code that can be correctly assem- bly code and data faithfully. The defending techniques bled back in a fully automated manner, even for simple against return-oriented programming (ROP) attacks also programs. Actually in many cases, the resulted disas- rely on binary analysis and reconstruction to identify and sembled code is far from a state that an assembler ac- eliminate ROP gadgets [44,9, 47, 22, 39]. cepts, which is hard to fix even by manual effort. This Despite the fact that many security hardening tech- has become a severe obstacle. People have tried to over- niques are highly dependent on reverse engineering, flex- come it by patching or duplicating new code sections for ible and easy-to-use binary manipulation itself remains retrofitting of executables, which is not only inefficient an unsolved problem. -

Endian: from the Ground up a Coordinated Approach

WHITEPAPER Endian: From the Ground Up A Coordinated Approach By Kevin Johnston Senior Staff Engineer, Verilab July 2008 © 2008 Verilab, Inc. 7320 N MOPAC Expressway | Suite 203 | Austin, TX 78731-2309 | 512.372.8367 | www.verilab.com WHITEPAPER INTRODUCTION WHat DOES ENDIAN MEAN? Data in Imagine XYZ Corp finally receives first silicon for the main Endian relates the significance order of symbols to the computers chip for its new camera phone. All initial testing proceeds position order of symbols in any representation of any flawlessly until they try an image capture. The display is kind of data, if significance is position-dependent in that regularly completely garbled. representation. undergoes Of course there are many possible causes, and the debug Let’s take a specific type of data, and a specific form of dozens if not team analyzes code traces, packet traces, memory dumps. representation that possesses position-dependent signifi- There is no problem with the code. There is no problem cance: A digit sequence representing a numeric value, like hundreds of with data transport. The problem is eventually tracked “5896”. Each digit position has significance relative to all down to the data format. other digit positions. transformations The development team ran many, many pre-silicon simula- I’m using the word “digit” in the generalized sense of an between tions of the system to check datapath integrity, bandwidth, arbitrary radix, not necessarily decimal. Decimal and a few producer and error correction. The verification effort checked that all other specific radixes happen to be particularly useful for the data submitted at the camera port eventually emerged illustration simply due to their familiarity, but all of the consumer. -

A Survey of Reverse Engineering Tools for the 32-Bit Microsoft Windows Environment

A Survey of Reverse Engineering Tools for the 32-Bit Microsoft Windows Environment RAYMOND J. CANZANESE, JR., MATTHEW OYER, SPIROS MANCORIDIS, and MOSHE KAM College of Engineering Drexel University, Philadelphia, PA, USA Reverse engineering is defined by Chikosfky and Cross as the process of analyzing a subject system to identify the system's components and their relationships, and to create representations of the system in another form or at a higher level of abstraction. The process of reverse engineering is accomplished using specific tools that, for the 32-bit Microsoft Windows environment, are categorized as hex editors, disassemblers/debuggers, decompilers, or related technologies such as code obfuscators, unpackers, and PE editors. An evaluation of each tool is provided that identifies its domain of applicability and usability. Categories and Subject Descriptors: A.1 [General]: Introductory and Survey; D.2.5 [Software Engineering]: Testing and Debugging General Terms: Security, Documentation Additional Key Words and Phrases: Reverse Engineering, Disassemblers, Debuggers, Decompilers, Code Obfuscators, PE Editors Unpackers, Hex Editors 1. INTRODUCTION 1.1 The Reverse Engineering Process Software engineers are sometimes asked to understand the behavior of a program given that program's binary executable file. If they have access to the appropriate reverse engineering tools, they might choose to adhere to the following process. First, a general disassembler/debugger is used to determine the basic functionality of the program. If disassembly and debugging shows that the binary code has been obfuscated, the next step would be to determine whether the obfuscator used is a common commercial obfuscator or a custom protection scheme. A PE editor would be used to make this determination. -

Implementing the UCSD PASCAL System on the MODCOMP Computer

TDA Progress Report 42-60 September and October 1960 Implementing the UCSD PASCAL System on the MODCOMP Computer T. Wolfe DSN Data Systems Section This article describes the UCSD PASCAL system developed by the University of California, San Diego, now available on the MODCOMP computer. The system includes a Pascal compiler and many useful utility programs. A BASIC compiler and a FORTRAN 77 compiler are also avatkble. There is currently a large amount of software availabie written in UCSD PASCAL, including a data base system, word processing systems and a MODULA compiler. I. Introduction Assembly language subroutines thus produced may also be called from either Pascal or FORTRAN. Currently the assem- The UCSD PASCAL* System is a complete interactive bler has not been modified to produce MODCOMP machine software development system consisting of an operating sys- code. A system library program may be used to build libraries tem, compilers (Pascal, BASIC, FORTRAN 77) two text of useful subroutines and the system linker used to link them editors (screen editor and line-oriented editor), a linker and to user programs. many useful utility programs. The system is written and main- tained in Pascal. The compiler generates code for an idealized processor known as the “pseudo-machine.” The “pseudo- Interpreters currently exist for Z80/8080, PDP 11 /LSI-1 1, code” (p-code) generated by the compiler is interpreted at 6800, 9900 and 6502 computers and are being developed for runtime by a program (known as the interpreter) which emu- other computers. Thus, software could be developed on an lates the pseudo-machine. -

A PROGRAMMABLE COMPUTER INTERFACE for CAMAC F by Robert W

NASA TECHNICAL NOTE NASA TN D-7148 A PROGRAMMABLE COMPUTER INTERFACE FOR CAMAC f by Robert W. Bercaw, Theodore E. Fessler, \ and Jeffrey M. Arnold Lewis Research Center Cleveland, Ohio 44135 NATIONAL AERONAUTICS AND SPACE ADMINISTRATION • WASHINGTON, D. C. • MARCH 1973 1. Report No. 2. Government Accession No. 3. Recipient's Catalog No. NASA TN D-7148 4. Title and Subtitle 5. Report Date March 1973 A PROGRAMMABLE COMPUTER INTERFACE FOR CAMAC 6. Performing Organization Code 7. Author(s) 8. Performing Organization Report No. Robert W. Bercaw, Theodore E. Fessler, and Jeffrey M. Arnold E-6957 10. Work Unit No. 9. Performing Organization Name and Address 503-10 Lewis Research Center 11. Contract or Grant No. National Aeronautics and Space Administration Cleveland, Ohio 44135 13. Type of Report and Period Covered 12. Sponsoring Agency Name and Address Technical Note National Aeronautics and Space Administration 14. Sponsoring Agency Code Washington, B.C. 20546 15. Supplementary Notes 16. Abstract An interface has been developed for CAMAC instrumentation systems that implements data transfers controlled either by the computer CPU or by an autonomous (data-channel) processor in the interface unit. The data channel processor executes programs stored in the computer memory. These programs consist of standard CAMAC module commands plus special control characters and commands for the processor itself. The interface was built for the PDP-15 computer, which has an 18-bit word structure, but both 18- and 24-bit data transfers can be made. A software system has been written that exploits the many features of the processor. 17. Key Words (Suggested by Author(s)) 18. -

Application Note Saving Data During a Power Failure Using the Dataflash® E-Series Family

Saving Data During a Power Failure Using the DataFlash® E-Series Family Application Note Saving Data During a Power Failure Using the DataFlash® E-Series Family Abstract This application note is intended to provide readers with information on how to save critical data to the Flash memory of DataFlash E-Series devices in the event of a power failure. The power failure is simulated by removing power to the devices. This document does not discuss how the power failure is detected, how the microcontroller may respond to the failure, or how the power rail is controlled for both the DataFlash device and the microcontroller. Product Highlights • Single 3V Read/Write Operation (1.65V - 3.6V Supply Range) • SPI Mode 0 and Mode 3 Compatible • Fast Read Access Times: 85 MHz Maximum Clock Frequency • Individual Hardware and Software Sector Protection • Security: 128-byte Register • JEDEC Standard Manufacturer and Device ID Read • Endurance: 100,000 Program/Erase Cycles per Page Minimum • Data Retention: 20 Years • Packaging Options: SOIC, DFN, WLCSP, Die/Wafer • Green (Pb/Halide-free) Packaging Options Application Note 114 11-Dec-2020 AN114 1 of 13 © 2020 Dialog Semiconductor Saving Data During a Power Failure Using the DataFlash® E-Series Family Revision History Revision Date Description A0 11-Dec-2020 Initial Release Application Note 114 11-Dec-2020 AN114 2 of 13 © 2020 Dialog Semiconductor Saving Data During a Power Failure Using the DataFlash® E-Series Family 1 Introduction The DataFlash E-series family of Flash memory devices are often used in applications such as server configuration, data logging, event counters and failure/error/status loggers. -

14-/12-Bit, 250MSPS, Ultralow-Power ADC with Analog Buffers Check for Samples: ADS41B29, ADS41B49

ADS41B29 ADS41B49 www.ti.com SBAS486E – NOVEMBER 2009–REVISED JULY 2012 14-/12-Bit, 250MSPS, Ultralow-Power ADC with Analog Buffers Check for Samples: ADS41B29, ADS41B49 1FEATURES DESCRIPTION The ADS41B29/B49 are members of the ultralow- 23• ADS41B49: 14-Bit, 250MSPS ADS41B29: 12-Bit, 250MSPS power ADS4xxx analog-to-digital converter (ADC) family, featuring integrated analog input buffers. • Integrated High-Impedance These devices use innovative design techniques to Analog Input Buffer: achieve high dynamic performance, while consuming – Input Capacitance: 2pF extremely low power. The analog input pins have – 200MHz Input Resistance: 3kΩ buffers, with benefits of constant performance and input impedance across a wide frequency range. The • Maximum Sample Rate: 250MSPS devices are well-suited for multi-carrier, wide • Ultralow Power: bandwidth communications applications such as PA – 1.8V Analog Power: 180mW linearization. – 3.3V Buffer Power: 96mW The ADS41B49/29 have features such as digital gain – I/O Power: 135mW (DDR LVDS) and offset correction. The gain option can be used to improve SFDR performance at lower full-scale input • High Dynamic Performance: ranges, especially at high input frequencies. The – SNR: 69dBFS at 170MHz integrated dc offset correction loop can be used to – SFDR: 82.5dBc at 170MHz estimate and cancel the ADC offset. At lower sampling rates, the ADC automatically operates at • Output Interface: scaled-down power with no loss in performance. – Double Data Rate (DDR) LVDS with Programmable Swing and Strength: The devices support both double data rate (DDR) low-voltage differential signaling (LVDS) and parallel – Standard Swing: 350mV CMOS digital output interfaces. The low data rate of – Low Swing: 200mV the DDR LVDS interface (maximum 500MBPS) – Default Strength: 100Ω Termination makes it possible to use low-cost field-programmable gate array (FPGA)-based receivers. -

Real-Time Operating System (RTOS)

Real-Time Operating System ELC 4438 – Spring 2016 Liang Dong Baylor University RTOS – Basic Kernel Services Task Management • Scheduling is the method by which threads, processes or data flows are given access to system resources (e.g. processor time, communication bandwidth). • The need for a scheduling algorithm arises from the requirement for most modern systems to perform multitasking (executing more than one process at a time) and multiplexing (transmit multiple data streams simultaneously across a single physical channel). Task Management • Polled loops; Synchronized polled loops • Cyclic Executives (round-robin) • State-driven and co-routines • Interrupt-driven systems – Interrupt service routines – Context switching void main(void) { init(); Interrupt-driven while(true); } Systems void int1(void) { save(context); task1(); restore(context); } void int2(void) { save(context); task2(); restore(context); } Task scheduling • Most RTOSs do their scheduling of tasks using a scheme called "priority-based preemptive scheduling." • Each task in a software application must be assigned a priority, with higher priority values representing the need for quicker responsiveness. • Very quick responsiveness is made possible by the "preemptive" nature of the task scheduling. "Preemptive" means that the scheduler is allowed to stop any task at any point in its execution, if it determines that another task needs to run immediately. Hybrid Systems • A hybrid system is a combination of round- robin and preemptive-priority systems. – Tasks of higher priority can preempt those of lower priority. – If two or more tasks of the same priority are ready to run simultaneously, they run in round-robin fashion. Thread Scheduling ThreadPriority.Highest ThreadPriority.AboveNormal A B ThreadPriority.Normal C ThreadPriority.BelowNormal D E F ThreadPriority.Lowest Default priority is Normal.