Serial Communication (Ch. 10) Digital Communication Interface Basics

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

SAS Storage Architecture: Serial Attached SCSI, 2005, Mike Jackson, 0977087808, 9780977087808, Mindshare Press, 2005

SAS Storage Architecture: Serial Attached SCSI, 2005, Mike Jackson, 0977087808, 9780977087808, MindShare Press, 2005 DOWNLOAD http://bit.ly/1zNQCoA http://www.barnesandnoble.com/s/?store=book&keyword=SAS+Storage+Architecture%3A+Serial+Attached+SCSI SAS (Serial Attached SCSI) is the serial storage interface that has been designed to replace and upgrade SCSI, by far the most popular storage interface for high-performance systems for many years. Retaining backward compatibility with the millions of lines of code written to support SCSI devices, SAS incorporates recent advances in high-speed serial design to provide better performance, better reliability and enhanced capabilities, all at a lower cost. SAS will be a significant part of many future high-performance storage systems, and hardware designers, system validation engineers, device driver developers and others working in this area will need a working knowledge of it.SAS Storage Architecture provides a comprehensive guide to the SAS standard. The book contains descriptions and numerous examples of the concepts presented, using the same building block approach as other MindShare offerings. This book details important concepts relating to the design and implementation of storage networks.Specific topics of interest include:SATA Compatibility Expander devices Discovery Process Connection protocols Arbitration of competing connection requests Flow Control protocols ACK/NAK protocol Primitives ? construction and uses Frames ? format, definition, used of each field Error checking mechanisms -

Crack Iscsi Cake 197

1 / 2 Crack Iscsi Cake 197 Open-E DSS V7 increases iSCSI target efficiency by supporting ... drive serial number and the drive serial number information from the robotic library), ... Open-E DSS V7 MANUAL www.open-e.com. 197 work in that User .... nuance pdf converter professional 8 crack keygen · avunu telugu movie english subtitles download torrent · Veerappan ... Crack Iscsi Cake 197.. Crack Iscsi Cake 1.97. Download. Crack Iscsi Cake 1.97. ISCSI...CAKE...1.8.0418...CRACK.. Merci..de..tlcharger..iSCSI.. Contribute to Niarfe/hack-recommender development by creating an account on GitHub. ... 197, ETAP. 198, EtQ. 199, Cincom Eloquence ... 1022, Adobe Target. 1023, Adobe ... 3485, Dell EqualLogic PS6500E iSCSI SAN Storage. 3486, Dell .... iscsi cake, iscsi cake crack, iscsi cake 1.8 crack full, iscsi cake 1.97 full, iscsi cake tutorial, iscsi cake 1.9 crack, iscsi cake 1.9 full, iscsi cake .... Crack Iscsi Cake 197 iscsi cake, iscsi cake 1.8 crack full, iscsi cake 1.9, iscsi cake full, iscsi cake 1.9 expired, iscsi cake crack, iscsi cake 1.9 full, .... Crack Iscsi Cake 197. June 16 2020 0. iscsi cake, iscsi cake 1.8 crack full, iscsi cake full, iscsi cake 1.8 serial number, iscsi cake 1.9, iscsi cake crack, iscsi cake ... Serial interface and protocol. Standard PC mice once used the RS-232C serial port via a D-subminiature connector, which provided power to run the mouse's .... Avira Phantom VPN Pro v3.7.1.26756 Final Crack (2018) .rar · fb limiter pro cracked full version ... Crack Iscsi Cake 197 · Hoshi Wo Katta Hi ... -

M515-2-Medialon-Control-System

Medialon Control System User Reference Manual Trademark Information Medialon is a trademark of Medialon Ltd. Product or company names that mentioned in Medialon Ltd publications are tradenames or trademarks of their respective owners, and such trademarks may also be registered in their respective countries. Copyright Information All Rights Reserved. This document is copyrighted © by Medialon Ltd and shall not be reproduced or copied without express written authorization from Medialon Ltd. The information in this document is subject to change without notice. Medialon Ltd assumes no responsibility for errors, and/or omissions contained in this information. Document Revision Date Document Software version Revision details Author/Editor edition May 2019 4.4.3 Rev 1 Medialon Manager 6.7 Published by Barco Eric Cantrell Medialon Showmaster Editor 2.7.0 June 2019 M515-1 Medialon Manager 6.7 Re-edited, published by Andie Davidson (ed) Medialon Showmaster Editor 2.7.0 Medialon Ltd May 2020 M515-2 Medialon Manager 6.7 Edited with addition of Eric Cantrell, Andie Medialon Showmaster Editor 2.7.0 Showmaster Go and Davidson (eds) Showmaster Mini M515-2 Contents 1 About this Manual .............................................................................................................................. 9 1.1 Prerequisites ..................................................................................................................................... 9 1.2 Objective of this Manual .................................................................................................................. -

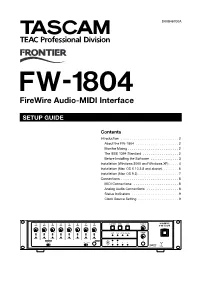

FW-1804 Firewire Audio-MIDI Interface

» D00846700A FW-1804 FireWire Audio-MIDI Interface SETUP GUIDE Contents Introduction ...............................2 About the FW-1804 .......................2 Monitor Mixing ...........................2 The IEEE 1394 Standard ...................2 Before Installing the Software ...............3 Installation (Windows 2000 and Windows XP) .....4 Installation (Mac OS X 10.2.8 and above).........6 Installation (Mac OS 9.2)......................7 Connections ...............................8 MIDI Connections ........................8 Analog Audio Connections .................8 Status Indicators .........................9 Clock Source Setting ......................9 Introduction About the FW-1804 • COMPUTER selects the signals from the DAW passed through the FireWire connection. The level of the signals from the computer is set using the master output control The FW-1804 provides your computer with high-quality of the DAW software and the two analog outputs may be audio facilities: eight channels of analog input and two of selected (using the software Control Panel) for output of output, with two channels of digital audio I/O through these signals. coaxial connections and eight channels of digital I/O through optical connections—at up to 96 kHz 24-bit. There • INPUTS selects the stereo mix of the analog, optical and are also two physical MIDI input and four physical output coaxial signals for monitoring. ports. • BOTH allows the computer signals to be monitored It is connected to the host computer using a single 6-pin to mixed with the input signals. 6-pin IEEE 1394 cable (supplied) that carries audio and Individual channels can be set to unity gain by pressing and MIDI information back and forth between the FW-1804 holding the computer's [Shift] key while clicking on the and the computer. -

SAS Enters the Mainstream Although Adoption of Serial Attached SCSI

SAS enters the mainstream By the InfoStor staff http://www.infostor.com/articles/article_display.cfm?Section=ARTCL&C=Newst&ARTICLE_ID=295373&KEYWORDS=Adaptec&p=23 Although adoption of Serial Attached SCSI (SAS) is still in the infancy stages, the next 12 months bode well for proponents of the relatively new disk drive/array interface. For example, in a recent InfoStor QuickVote reader poll, 27% of the respondents said SAS will account for the majority of their disk drive purchases over the next year, although Serial ATA (SATA) topped the list with 37% of the respondents, followed by Fibre Channel with 32%. Only 4% of the poll respondents cited the aging parallel SCSI interface (see figure). However, surveys of InfoStor’s readers are skewed by the fact that almost half of our readers are in the channel (primarily VARs and systems/storage integrators), and the channel moves faster than end users in terms of adopting (or at least kicking the tires on) new technologies such as serial interfaces. Click here to enlarge image To get a more accurate view of the pace of adoption of serial interfaces such as SAS, consider market research predictions from firms such as Gartner and International Data Corp. (IDC). Yet even in those firms’ predictions, SAS is coming on surprisingly strong, mostly at the expense of its parallel SCSI predecessor. For example, Gartner predicts SAS disk drives will account for 16.4% of all multi-user drive shipments this year and will garner almost 45% of the overall market in 2009 (see figure on p. 18). -

Download the • Event Information Is Stored As a Separate File

AAAATMANIRBHARTTMANIRBHARTAA BYBY HALHAL ONEONE STOPSTOP SOLUTIONSOLUTION FORFOR ALLALL AEROSPAEROSPACEACE NEEDSNEEDS OVERHAUL/UPGRADE • HAL has produced over 4200 • ISO 9001 "Navratna" Company aircraft & over 5200 engines, • ISO 14000 • About 25,000 Employees including 17 types of indigenous • Turnover more than • AS 9100D design. 2.8 Billion USD • HAL has also overhauled over 11000 • NADCAP • Listed Company on BSE aircraft and 33000 engines Certifications and NSE OVERHAUL/UPGRADE To achieve self reliance in design, development, manufacture, upgrade To become a and maintenance of aerospace equipment, diversifying significant into related areas and managing the business in a climate of growing global player in professional competence to achieve world class performance the aerospace standards for global competitiveness and growth in exports. industry. 3 CONTENT 9 TEJAS-LCA 32 AFCC 10 HTT-40 11 DHRUV 12 LCH 13 LUH 14 RUDRA 15 JAGUAR UPGRADE AIRCRAFT FLIGHT CONTROL PLATFORMS PAGE 6 PAGE 17 SYSTEM PAGE 33 ABOUT HAL PAGE 9 Communication, PAGE 31 Navigation & RECORDING Identification SYSTEM systems 6 THE COMPANY 18 DACS 34 SSDVRS 7 PRODUCTION CENTRES 19 ACS 235 35 CVFDR 8 DESIGN COMPLEX 20 SoftNet Radio 36 SSFDR 21 SCDLU 37 CPMM 22 VACS 38 SSFDR/CVR 23 MNS 24 VOR/ILS 25 ADVANCED TACAN 26 RAM 2700A 27 IFFT-2460ALH1 28 IFFI-3400A 29 CIT 30 AIS 4 CONTENT 42 Mission Computer for Mirage 2000 68 TRANSFORMER RECTIFIER UNIT (TRU) 43 Jaguar Darin III 69 AC POWER MANAGEMENT & DISTRIBUTION Mission Computer S YSTEM 44 Mission Computer (MC) 70 ALTERNATOR CONTROL -

For Immediate Release

an ellisys company FOR IMMEDIATE RELEASE SerialTek Contact: Simon Thomas, Director, Sales and Marketing Phone: +1-720-204-2140 Email: [email protected] SerialTek Debuts PCIe x16 Gen5 Protocol Analysis System and Web Application New Kodiak™ Platform Brings SerialTek Advantages to More Computing and Data Storage Markets Longmont, CO, USA — February 24, 2021 — SerialTek, a leading provider of protocol test solutions for PCI Express®, NVM Express®, Serial Attached SCSI, and Serial ATA, today introduced an advancement in the PCIe® test and analysis market with the release of the Kodiak PCIe x16 Gen5 Analysis System, as well as the industry’s first calibration-free PCIe x16 add-in-card (AIC) interposer and a new web-based BusXpert™ user interface to manage and analyze traces more efficiently than ever. The addition of PCIe x16 Gen5 to the Kodiak analyzer and SI-Fi™ interposer family brings previously unavailable analysis capabilities and efficiencies to computing, datacenter, networking, storage, AI, and other PCIe x16 Gen5 applications. With SerialTek’s proven calibration-free SI-Fi interposer technology, the Kodiak’s innovative state-of-the-art design, and the new BusXpert analyzer software, users can more easily set up the analyzer hardware, more accurately probe PCIe signals, and more efficiently analyze traces. Kodiak PCIe x16 Gen5 Analysis System At the core of the Kodiak PCIe x16 analyzer is an embedded hardware architecture that delivers substantial and unparalleled advancements in capture, search, and processing acceleration. Interface responsiveness is markedly advanced, searches involving massive amounts of data are fast, and hardware filtering is flexible and powerful. “Once installed in a customer test environment the Kodiak’s features and benefits are immediately obvious,” said Paul Mutschler, CEO of SerialTek. -

United States Patent (19) 11 Patent Number: 6,157,976 Tien Et Al

USOO6157976A United States Patent (19) 11 Patent Number: 6,157,976 Tien et al. (45) Date of Patent: Dec. 5, 2000 54 PCI-PCI BRIDGE AND PCI-BUS AUDIO OTHER PUBLICATIONS ACCELERATOR INTEGRATED CIRCUIT PCI System Architecture, Tom Shanley/Don Anderson, 75 Inventors: Paul Tien, Fremont; Cheng-Yeuan 1995, pp. 381-382. Tsay, Pleasanton; Rsong-Hsiang Shiao, Fremont, all of Calif. Primary Examiner Ayaz R. Sheikh Assistant Examiner Rupal D. Dharia 73 Assignee: ESS Technology, Fremont, Calif. Attorney, Agent, or Firm-Gray Cary Ware & Freidenrich 57 ABSTRACT 21 Appl. No.: 09/074,657 A semiconductor device with an embedded PCI 2.1 com 22 Filed: May 6, 1998 pliant bridge provides expanded functionality as System 51511 Int. Cl. ............................. GO6F13FOO700; GO6F 13/38/ level implementationsp of a PCI-to-PCI bridge,9. and enhances 52 U.S. Cl. ............................ 710/129, 710/127, 710/64; the level of integration possible. The embedded PCI-to-PCI 345/435; 84/604; 84/621; 84/622; 84/647 bridge allows the creation of multi-function, multimedia 58) Field of Search 345/435: 710/127 add-on cards Supporting multiple devices. Multi-function, 710129,6484/602,604 621 622 647. multimedia Subsystems that provide audio, graphics, MPEG, s w is s s 454. 70425s etc., are mapped into a bridged-to PCI-bus that keeps Such s traffic off the main PCI-bus. The advantage for the system or 56) References Cited add-in card Vendor is that the various multimedia chips that are combined can come from different Sources, providing an U.S. PATENT DOCUMENTS optimized and highly customized combination of functions. -

Profire Lightbridge User Guide | 2 Introduction 1

34-in/36-out FireWire Lightpipe Interface User Guide English Table of Contents English . 2 Introduction . 2 What’s in the Box . 2 About ProFire Lightbridge . 3 ProFire Lightbridge Features . 4 System Requirements . 5 Controls and Connectors . 6 Front Panel . 6 Rear Panel . 7 Driver Installation . 8 Hardware Connections . 8 Audio . 8 MIDI . 9 Word Clock . 9 Using ProFire Lightbridge . 9 The Software Control Panel . 10 Hardware Page . 10 About Page . 13 Word Clock Synchronization . 14 Understanding Word Clock . 14 Specifications . 18 Warranty . 19 Warranty Terms . 19 Warranty Registration . 19 M-Audio ProFire Lightbridge User Guide | 2 Introduction 1 hank you for purchasing M-Audio’s ProFire Lightbridge interface. ProFire Lightbridge uses the ADAT optical T I/O standard to bring extensive digital connectivity to your studio. With its four ADAT optical inputs, four ADAT optical outputs, S/PDIF coaxial input and output, and stereo analog outputs, ProFire Lightbridge lets you connect a variety of devices to your FireWire-equipped digital audio workstation. Using the high-bandwidth, industry-standard FireWire (IEEE1394) protocol, ProFire Lightbridge gives your DAW up to 34 audio inputs and 36 outputs while connecting to your computer via a single cable. This makes it perfect for multi-channel transfers to and from external multitrack recorders. ProFire Lightbridge is also ideal for linking your DAW to an external digital mixer, or for connecting to another computer hosting soft synths and signal processors. This manual will explain the features and operation of ProFire Lightbridge. Even if you are an experienced recording enthusiast, please take a moment to read this guide and familiarize yourself with all of the unique features of your ProFire Lightbridge. -

US-16X08 Reference Manual

D01247020B US-16x08USB2.0 Audio Interface/Mic Preamp Reference Manual Before connecting this unit to a computer, you must download and install a dedicated driver. Contents 1 – Introduction ..............................................3 Windows 8 ....................................................................23 Features ..................................................................................3 Windows 7 ....................................................................23 Conventions used in this manual ..................................3 Mac OS X and iTunes ........................................................24 iOS ..........................................................................................24 2 – Names and functions of parts ..................4 Front panel ............................................................................4 9 – MIDI Implementation Chart ...................25 Rear panel ..............................................................................5 10 – Troubleshooting ...................................26 3 – Installation ................................................6 Troubleshooting ................................................................26 System requirements.........................................................6 11 – Specifications ........................................28 Windows ..........................................................................6 Specifications .....................................................................28 Mac OS X..........................................................................6 -

Isolated RS-485 Transceivers Support DMX512 Stage Lighting & Special-Effects

Texas Instruments Incorporated Interface (Data Transmission) Isolated RS-485 transceivers support DMX512 stage lighting and special- effects applications By Thomas Kugelstadt Senior Applications Engineer Figure 1. Daisy-chained topology of DMX512 network Controller Receiver 1 Receiver 2 Receiver n Terminator (Master) (Slave) (Slave) (Slave) (120 W) OUT IN OUT IN OUT IN OUT IN Stage lighting and special-effects applications in modern Within the network, all nodes are connected through daisy- theaters, opera houses, sports arenas, and concert halls chaining; that is, each slave node has an IN connector as utilize complex data-transmission networks. These net- well as an OUT connector. The controller, which has only works, often reaching distances of up to 1200 m, provide an OUT connector, connects to the IN connector of the communication between several hundreds of network first slave. The OUT connector of the first slave connects nodes that control dimmers, moving lights, fog machines, to the IN connector of the next slave, and so on (see and other special-effects equipment. Figure 1). The OUT connector of the last slave in the The first standard ensuring reliable intercommunication chain connects to a 100-W or 120-W terminator plug. for these applications was known as DMX512 and was So that the ingoing and outgoing data signals of a originally developed in 1986 by the United States Institute DMX512 port can be distinguished, the IN connectors are for Theatre Technology (USITT) Engineering Commission. male XLR-5, and the OUT connectors are female XLR-5 In 1998, the Entertainment Services and Technology (see Figure 2). -

Serial Communication Buses

Computer Architecture 10 Serial Communication Buses Made wi th OpenOffi ce.org 1 Serial Communication SendingSending datadata oneone bitbit atat oneone time,time, sequentiallysequentially SerialSerial vsvs parallelparallel communicationcommunication cable cost (or PCB space), synchronization, distance ! speed ? ImprovedImproved serialserial communicationcommunication technologytechnology allowsallows forfor transfertransfer atat higherhigher speedsspeeds andand isis dominatingdominating thethe modernmodern digitaldigital technology:technology: RS232, RS-485, I2C, SPI, 1-Wire, USB, FireWire, Ethernet, Fibre Channel, MIDI, Serial Attached SCSI, Serial ATA, PCI Express, etc. Made wi th OpenOffi ce.org 2 RS232, EIA232 TheThe ElectronicElectronic IndustriesIndustries AllianceAlliance (EIA)(EIA) standardstandard RS-232-CRS-232-C (1969)(1969) definition of physical layer (electrical signal characteristics: voltage levels, signaling rate, timing, short-circuit behavior, cable length, etc.) 25 or (more often) 9-pin connector serial transmission (bit-by-bit) asynchronous operation (no clock signal) truly bi-directional transfer (full-duplex) only limited power can be supplied to another device numerous handshake lines (seldom used) many protocols use RS232 (e.g. Modbus) Made wi th OpenOffi ce.org 3 Voltage Levels RS-232RS-232 standardstandard convertconvert TTL/CMOS-levelTTL/CMOS-level signalssignals intointo bipolarbipolar voltagevoltage levelslevels toto improveimprove noisenoise immunityimmunity andand supportsupport longlong cablecable lengthslengths TTL/CMOS → RS232: 0V = logic zero → +3V…+12V (SPACE) +5V (+3.3V) = logic one → −3V…−12V (MARK) Some equipment ignores the negative level and accepts a zero voltage level as the "OFF" state The "dead area" between +3V and -3V may vary, many receivers are sensitive to differentials of 1V or less Made wi th OpenOffi ce.org 4 Data frame CompleteComplete one-byteone-byte frameframe consistsconsists of:of: start-bit (SPACE), data bits (7, 8), stop-bits (MARK) e.g.