New Method for Diagnostics of Ion Implantation Induced Charge Carrier Traps in Micro- and Nanoelectronic Devices

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

07. Hallmark 2011-12.Pdf

Know that the life of this world is only play and amusement pomp and mutual boasting among you, and rivalry in respect of wealth and children, as the likeness of vegetation after rain, thereof the growth is pleasing to the tiller; afterwards it dries up and you see it tutrning yellow: then it becomes straw. But in the Hereafter (there is) Forgiveness from Allah and (His) Good Pleasure (for the believers, good-doers), whereas the life of this worls is only a deceiving enjoyment Al-Hadeed 57:20 Army Burn Hall College for Boys The Hallmark 2011-12 Q U M O A N ND ON ASCE CONTENTS Message of the Chairman Board of Governors ....................................................................................... 7 Message of the Deputy Chairman Board of Governors ......................................................................... 9 Principal’s Message .................................................................................................................................... 10 From the Editor’s Pen ................................................................................................................................ 12 The College Faculty ................................................................................................................................... 14 VIEWS & REVIEWS ................................................................................................................................ 18 ANNUAL DAY AND PRIZE DISTRIBUTION Principal’s Report - Annual Parents Day and Prize Distribution Ceremony -

List of Bronze Medal Winners

LIST OF BRONZE MEDAL WINNERS FIRST POSITION IN INSTITUTION S. NO. ROLL NO. STUDENT NAME FATHER NAME CLASS INSTITUTION CITY/DISTRICT 1 20-459-00181-1-027-E AAMINAH RAZA HASSAN RAZA NASEEM 1 JAUHER LYCEUM HIGH SCHOOL MIANWALI 2 20-55-00657-1-001-E AAQIL MANNAN MANNAN KHALIL 1 THE CITY SCHOOL JUNIOR SECTION GUJRANWALA 3 20-66-00781-1-001-E AARAMISH AHMAD AHMAD RAZA 1 THE CITY SCHOOL KAPCO CHAPTER MUZAFFARGARH 4 20-55-00216-1-009-E AARIZ MALIK MUHAMMAD NAEEM 1 ROOTS MILLENNIUM SCHOOL KINGSBURY CAMPUS GUJRANWALA 5 20-021-20237-1-002-E ABDUL BARI KHAN MUHAMMAD KASHIF IQBAL 1 GLAMOUR CHILDREN SECONDARY SCHOOL KARACHI 6 20-51-20552-1-001-E ABDUL DAYAN JAVED MUHAMMAD WASIF JAVED 1 JUNIOR ACADEMY HAMZA CAMPUS RAWALPINDI 7 20-923-20039-1-001-E ABDUL HADI MUHAMMAD WAQAR ZAFAR 1 ARMY PUBLIC SCHOOL & COLLEGE (IQRA) NOWSHERA 8 20-51-00147-1-005-E ABDUL HADI MALIK SAEED IQBAL 1 ROOTS IVY INTERNATIONAL SCHOOLS PWD CAMPUS ISLAMABAD 9 20-021-20902-1-024-E ABDUL HADI IMRAN IMRAN HAMEED 1 DM SCHOOL SYSTEM KARACHI 10 20-51-00147-1-004-E ABDUL HADI USMAN MUHAMMAD USMAN GHANI 1 ROOTS IVY INTERNATIONAL SCHOOLS PWD CAMPUS ISLAMABAD 11 20-022-00320-1-002-E ABDUL MOMIN AHMED ALI 1 ARMY PUBLIC SCHOOL & COLLEGE SRC HYDERABAD 12 20-53-20799-1-002-E ABDUL MOMIN MUHAMMAD NOUMAN 1 THE EDUCATORS REHMAN CAMPUS GUJRAT 13 20-51-00257-1-001-E ABDUL MOOED NAVEED CHAUDARY NAVEED AHMED 1 ROOTS GARDEN SCHOOL 93-HARLEY CAMPUS RAWALPINDI 14 20-48-00970-1-019-E ABDUL RAFAY JAWAD KHAWAJA JAWAD HASSAN 1 LAHORE GRAMMAR SCHOOL SARGODHA 15 20-021-20546-1-004-E ABDULLAH AMIN FAROOQ 1 THE HORIZON HIGH KARACHI 16 20-41-00963-1-002-E ABDULLAH ADNAN MUHAMMAD ADNAN 1 ALLIED SCHOOL MADINA CAMPUS FAISALABAD * Bronze Medal: First position in the institution within the respective class and at least 75% achieved. -

Annual Report 2006-07

Annual Report 2009-2010 Facilities of the University and Improvements FACILITIES OF THE UNIVERSITY AND IMPROVEMENTS AFFILIATION BRANCH Affiliaton Committee visited large number of colleges all over the Punjab for grant of fresh affilication in various subjects as well as to verify the standard of education in the already affiliated institutions. The details are summarized below:- Total Colleges visited : 676 Fresh Affiliation granted : 76 Addition / Extension / Increase in intake granted : 363 Addition / Extension / Increase in intake not granted : 48 Affiliation not granted : 51 Provisional Affiliation / Addition in affiliation granted : 0 De-Affiliation / Affiliation withdrawn : 17 CHILD WELFARE CENTRE Introduction: Child Welfare Centre, University of the Punjab, is now in the 8th year of its establishment since 13th Jan, 2003. During these years the Centre flourished as a self sustaining institution for the education and rehabilitation of students with special needs. In addition a vocational training is also running. Child Welfare Centre is progressing towards provide excellent facilities of diagnosis test, parents counseling, behaviour therapy as well as rehabilitation and education of children with special needs to make them a self sustained citizen to the society .Child Welfare Centre is venturing to excel in providing quality education to children with special needs. Now CWC is extending rehabilitation facilities for all major disabilities viz Mental Retardation, Physical Handicapped, Hearing Impairment, Visual impairment & Autism. Physio Therapy: In the Child Welfare Centre we use multi disciplinary approaches, where skills & care join together. This approach incorporates medicine, physiotherapy, occupational & vocational therapy as well as speech & swallowing therapy. In physiotherapy department every new child is assessed by qualified physiotherapist carefully. -

Shahid Yaqub Abbasi Education 2019 Iub Prr.Pdf

IMPACT OF LEARNING ENVIRONMENT OF CADET COLLEGES ON PERSONALITY DEVELOPMENT AND LIFE SUCCESS OF STUDENTS IN PAKISTAN SHAHID YAQUB ABBASI Reg. No. 50/IU.PhD/2015 DEPARTMENT OF EDUCATION The Islamia University of Bahawalpur PAKISTAN 2019 IMPACT OF LEARNING ENVIRONMENT OF CADET COLLEGES ON PERSONALITY DEVELOPMENT AND LIFE SUCCESS OF STUDENTS IN PAKISTAN By SHAHID YAQUB ABBASI Reg. No. 50/IU.PhD/2015 A thesis submitted in partial fulfillment of the requirements for the Award of the degree of Doctor of Philosophy in Education DEPARTMENT OF EDUCATION The Islamia University of Bahawalpur PAKISTAN 2019 DECLARATION I, Shahid Yaqub Abbasi, Registration No. 50/IU.PhD/2015, Ph.D. Scholar (Session 2015-2018) in the Department of Education, The Islamia University of Bahawalpur hereby declare that the thesis titled, ―Impact of Learning Environment of Cadet Colleges on Personality Development and Life Success of Students in Pakistan‖ submitted by me in partial fulfillment of the requirement of Ph.D. in the subject of Education is my original work. I affirm that it has not been submitted or published earlier. It shall also not be submitted to obtain any degree to any other university or institution. Shahid Yaqub Abbasi i FORWARDING CERTIFICATE The research titled ―Impact of Learning Environment of Cadet Colleges on Personality Development and Life Success of Students in Pakistan‖ is conducted under my supervision and thesis is submitted to The Islamia University of Bahawalpur in the partial fulfillment of the requirements for award of the degree of Doctor of Philosophy in Education with my permission. Prof. Dr. Akhtar Ali ii APPROVAL CERTIFICATE This thesis titled ―Impact of Learning Environment of Cadet Colleges on Personality Development and Life Success of Students in Pakistan‖ written by Shahid Yaqub Abbasi is accepted and approved in the partial fulfillment of the requirement for the degree of Doctor of Philosophy in Education. -

Planning Report MC Sarai Alamgir

PUNJAB MUNICIPAL DEVELOPMENT FUND COMPANY PUNJAB MUNICIPAL SERVICES IMPROVEMENT PROJECT (PMSIP) PLANNING REPORT SARAI ALAMGIR 2008 TABLE OF CONTENTS CHAPTER 1 INTRODUCTION 3 1.1 Background 3 1.2 Punjab Municipal Service Improvement Project (PIMSIP) 3 1.2.1 Key Features of PMSIP 3 1.3 PMSIP Planning 3 1.3.1 Limitations of PMSIP Planning 4 1.4 The Planning Process 4 1.4.1. Secondary Data Collection 4 1.4.2. Mapping 5 1.4.3 Orientation Workshop 5 1.4.4 Field Data Collection 6 1.4.5 Data Analysis 7 1.4.6 The Visioning Workshop 7 1.4.7 Meeting for the Assessment of Options 7 CHAPTER 2 TMA PROFILE 9 2.1 District Profile 9 2.1.1 History 9 2.1.2 Location 9 2.1.3 Area/Demography 9 2.2 PROFILE OF SARAI ALAMGIR 9 2.2.1 History 9 2.2.2 Location 10 2.2.3 Area/ Demography 10 CHAPTER 3: URBAN PLANNING 11 3.1 Land use Characteristics 11 3.2 Growth Direction 11 3.3 Urban Planning Staff 12 CHAPTER 4: STATUS OF MUNICIPAL INFRASTRUCTURE 14 4.1 ROAD NETWORK 14 4.3 WATER SUPPLY 18 4.3.1 Water Service Area 18 4.3.2 Water Source 18 4.5 SOLID WASTE MANAGEMENT 23 4.5.1 Existing Collection System 23 4.5.2 Existing Land Fill/Dumping Sites 23 4.5.3 Area Required for Landfill 23 4.6 FIRE FIGHTING 27 CHAPTER 5 WORKSHOP ON VISIONING AND PRIORITIZATION OF DEVELOPMENT SECTORS 30 5.1 Pre-Workshop Consultations 30 5.2 Workshop Proceedings 30 2 Punjab Municipal Services Improvement Project (PMSIP) Planning Report – Sarai Alamgir 5.2.2 Workshop Participants 30 5.2.3 The Session 30 5.2.4 Group Formation 31 5.3 Prioritized List of Projects 31 CHAPTER 6 NSTITUTIONAL ANALYSIS 33 6.1 Capacity Building at TMA 33 6.2 Performance Management System 33 6.3 Financial Management System 34 Annex – A 37 Annex-B 39 Annex-C 40 Annex- D 41 CHAPTER 1 INTRODUCTION 1 Background Planning is a part of Punjab’s local government system with the planning responsibilities of TMAs, set out in PLGO. -

Institution-Wise Total Candidates Appeared / Passed / Pass Percentage Higher Secondary School Certificate Examination Annual, 2

BOARD OF INTERMEDIATE & SECONDARY EDUCATION, RAWALPINDI PAGE NO VIII BISER COMPUTER SECTION INSTITUTION-WISE TOTAL CANDIDATES APPEARED / PASSED / PASS PERCENTAGE DATE: SEPTEMBER 10, 2011 HIGHER SECONDARY SCHOOL CERTIFICATE EXAMINATION ANNUAL, 2011 ENRO CANC APPE UFM/ PASS PASS FAI ABS --PASSING GRADE WISE - GROUPS LLED LLED ARED ETC ED %AGE LED ENT A A1 B C D E INSTITUTE NAME 102161 CADET COLLEGE BOYS (SECONDARY LEVEL) FATEH PRE-ENG 16 0 16 8 0 0 8 0 JANG (ATTOCK) PRE-MED 1 0 1 0 1 100 0 0 1 SC-GEN 9 0 9 3 1 16.67 5 0 1 TOTAL 26 0 26 11 2 13.33 13 0 1 1 103003 GOVT. GIRLS HIGH SCHOOL, CHOA SAIDEN SHAH, HUMANITIES 16 0 14 0 6 42.86 8 2 1 3 2 (CHAKWAL.) TOTAL 16 0 14 0 6 42.86 8 2 1 3 2 103201 GOVT. GIRLS HIGH SCHOOL BHARPUR CHAKWAL. HUMANITIES 7 0 7 0 5 71.43 2 0 1 3 1 TOTAL 7 0 7 0 5 71.43 2 0 1 3 1 104277 CADAT COLLEGE KALLAR KAHAR SECONDARY SCHOOL PRE-ENG 69 0 69 0 69 100 0 0 29 21 18 1 CHAKWAL PRE-MED 18 0 18 0 18 100 0 0 7 11 TOTAL 87 0 87 0 87 100 0 0 36 32 18 1 106266 MILITARY COLLEGE JHELUM, SARAI ALAMGIR. PRE-ENG 85 0 85 0 85 100 0 0 30 10 31 14 SC-GEN 23 0 23 0 23 100 0 0 8 2 7 6 TOTAL 108 0 108 0 108 100 0 0 38 12 38 20 107011 GOVT. -

List of Bronze Medal Winners

LIST OF BRONZE MEDAL WINNERS FIRST POSITION IN INSTITUTION S. NO. ROLL NO. STUDENT NAME FATHER NAME CLASS INSTITUTION CITY/DISTRICT AAIMAH AHMED 1 18-47-20594-1-002-E IRFAN AHMED SUALEH 1 THE CITY NURSERY JHANG SUALEH 2 18-42-00739-1-014-E AAMINA HABIB HABIB QASIM 1 THE CITY SCHOOL JUNIOR LAHORE AL A'LA SCHOOL OF 3 18-42-20387-1-003-E AAMNA FAISAL FAISAL RIAZ 1 CONTEMPORARY AND LAHORE ISLAMIC STUDIES AANIYA AAMER 4 18-992-20490-1-003-E AAMER BHATTI 1 THE CITY NURSERY ABBOTTABAD BHATTI 5 18-051-00241-1-004-E AAYAN MASROOR TIPU MASROOR 1 ROOTS MILLENNIUM SCHOOL ISLAMABAD 6 18-544-20506-1-001-E ABBIHA MUNTAHA NISAR AHMAD 1 WINNINGTON SCHOOL JHELUM BLOOMFIELD HALL PREPS 7 18-61-00831-1-001-E ABDUL AHAD GARDEZI AHMAD NAWAZ GARDEZI 1 MULTAN AND JUNIOR SCHOOL ARMY PUBLIC SCHOOL 8 18-52-00546-1-069-E ABDUL AZIZ MUHAMMAD QASIM 1 SIALKOT JUNIOR CAMPUS 9 18-55-00222-1-011-E ABDUL AZIZ HAROON MUHAMMAD HAROON 1 THE NOOR SCHOOL GUJRANWALA THE CITY SCHOOL LIAQUAT 10 18-022-00518-1-001-E ABDUL HADI NASIR KHAN 1 HYDERABAD CAMPUS ALLIED SCHOOL 11 18-62-00468-1-009-E ABDUL HADI MUHAMMAD SHAKIR 1 BAHAWALPUR PRIMARY BAHAWALPUR CAMPUS ARMY PUBLIC SCHOOL 12 18-62-20346-1-008-E ABDUL KABEER HADI KHURRAM SHAHZAD 1 BAHAWALPUR MIDDLE BAHAWALPUR CANTT ABDUL MOIZ BIN MALIK RASHID THE CITY SCHOOL ATTOCK 13 18-57-00554-1-003-E 1 ATTOCK RASHID MEHMOOD CAMPUS AIR FOUNDATION SCHOOL 14 18-51-00538-1-004-E ABDUL RAFAY ABDUL HANAN ABBASSI 1 RAWALPINDI SYSTEM HARLEY CAMPUS AGA KHAN SCHOOL 15 18-021-00714-1-002-E ABDUL REHMAN MUHAMMAD IQBAL 1 KARACHI KHARADHAR ALLIED SCHOOL -

S# Code Name City Phone No Gender Principal Name Principal Mobile No 1 1024 Fazaia Education System School, E-9, PAF Complex, Islamabad Islamabad 051- Co-Education Dr

HSSC S# Code Name City Phone No Gender Principal Name Principal Mobile No 1 1024 Fazaia Education System School, E-9, PAF Complex, Islamabad Islamabad 051- Co-Education Dr. Wajiha Asif 0306-3966454 9262398,9507567 2 1073 Army Public School & College, Pothwar Complex, Alipur Farash, Islamabad 051-2618308,051- Co-Education ASAD 0333-5505318 Islamabad 9095549 MAHMOOD 3 1130 Fazaia Inter College, E-9, Islamabad. Islamabad 051-9507551, Co-Education Air Cdre(R) 0323-9516636 9261610 Waheed Tariq 4 1116 Bahria College, Naval Complex, E-8, Islamabad. Islamabad 20063551, Co-Education Cdr Hamid 0346-2434939 2289631,2289614 Hussain SI (M) 5 1156 Cadet College, Humak, Kahuta Road, Islamabad . Islamabad 051-4491541-3 MALE 0333-5619044 6 1229 Bahria Foundation College, East Service Road, Opp. St. 165, G-13/3, Islamabad 051-2300996-7 Co-Education Lt Cdr (R) Syed 0336-5186114 Islamabad Imtiaz Ali Shah 7 1213 DHAI Army Public School, ST. 23, Sector F, Commercial Area, Phase-Islamabad 051-2311382 Co-Education Mrs Rizwan 0323-5017000 II, Islamabad Khalid 8 1215 Bahria Model College, St. 34, E-8, Naval Complex, Islamabad Islamabad 051-20063083, Co-Education LT CDR(R) 0345-5151973 9261159, KHALID MAHMOOD PN 9 1216 Army Public School & College, G.T. Road, Rawat (F.A.), Islamabad Islamabad 0514612090 Co-Education Mr. Mian 03366644422- Muhammad Riaz 4612091 10 2202 Fazaia Intermediate College, Chaklala, Rawalpindi Cantt. Rawalpindi 051-9525511, 051- Co-Education Waqar Sultan 0300-8114110 9280724, Jandrani 11 2206 Fazaia Degree College, MRF Kamra, Attock. Attock 051-90994284, Co-Education Younas Nouman 0321-5121881 12 2213 Abdul Razzaq Fazaia College, Mianwali. -

ADMISSION FORM ENTRY : 2021 Attested CATEGORY: (Tick One Whichever Is Applicable) Photograph

Serial No._____ Roll No___________________ (To be allotted by the College) MILITARY COLLEGE SUI ADMISSION FORM ENTRY : 2021 Attested CATEGORY: (Tick one whichever is applicable) Photograph (Passport Size) District Dera Bugti Residents Balochistan Residents Army Offrs (Serving) Army Offrs (Retd) Army JCOs/Sldrs (Serving) Army JCOs/Sldrs (Retd) Pakistan Rangers (Sindh) Civilians/ Navy/ Air Force FC Bln North (JCOs/Sldrs Serving) FC Bln South (JCOs/Sldrs Serving) FATA MES (Civ) Gilgit Baltistan (Civ) Azad Jammu & Kashmir (Civ) APPLICATION FOR: 1. Class 8th PART – I GENERAL 2. FORM WILL BE FILLED IN BY THE CANDIDATE, WITH HIS OWN HANDWRITING. 3. Choice of Centre: WRITTEN TEST INTELLIGENCE TEST MEDICAL EXAMINATION Note:- While marking choice of centre, please see the attached slip for examination centres. PART – II PARTICULARS OF CANDIDATE 4. Name (IN BLOCK LETTERS) __________________________________________________ 5. Father’s Name _________________________________________________________ 6. Name of Guardian (if father not alive) ____________________________________________ 7. CNIC of Father/Guardian - - 8. Father’s/Guardian’s Occupation ______________________________________________ 9. Religion _______ Sect __________ 10. Caste ______________ Sub Caste ___________ 11. Date of Birth Day Month Year (in words) ______________________________________ 12. Place of Birth __________ 13. Total age (on 01 April 2021) Day Month Year 14. Distt of Domicile________________________ Province_________________________ 15. Name of School (presently attending) -

List of Bronze Medal Winners First Position in Institution S

LIST OF BRONZE MEDAL WINNERS FIRST POSITION IN INSTITUTION S. NO. ROLL NO. STUDENT NAME FATHER NAME CLASS INSTITUTION CITY/DISTRICT GARRISON ACADEMY 1 18-61-05562-1-007-C ABDUL HANAN ABDUL MANAN 1 MULTAN PRIMARY SECTION ARMY PUBLIC SCHOOL AND 2 18-51-05413-1-003-C ABDULLAH SAEED SAEED AHMAD 1 RAWALPINDI COLLEGE FWO ISLAMABAD MODEL COLLEGE 3 18-051-05485-1-001-C ABDULLAH SHAHZAD SHAHZAD QAYYUM 1 ISLAMABAD FOR BOYS DHAI EDUCATION SYSTEM 4 18-051-05608-1-004-C ALI ZEESHAN ZEESHAN AHMAD 1 ISLAMABAD FLAGSHIP CMAPUS 5 18-021-05677-1-001-C AMNA IRFAN 1 THE CITY NURSERY KARACHI ROOTS INTERNATIONAL 6 18-051-05653-1-002-C ARHAM WASEEM MUHAMMAD WASEEM 1 ISLAMABAD SCHOOLS REPTON CAMPUS FEDERAL SCIENCE COLLEGE 7 18-55-05453-1-004-C ARSH AMAN HAMID ALI 1 GUJRANWALA GIRLS WING 8 18-923-05315-1-008-C ASHRAF KHAN SHAFQAT NASIR 1 THE CITY NURSERY NOWSHERA ROOTS INTERNATIONAL 9 18-051-05653-1-003-C AYESHA RUBAB TARIQ MEHMOOD 1 ISLAMABAD SCHOOLS REPTON CAMPUS BEACONHOUSE KINDER 10 18-051-05345-1-001-C ESASHIKA KAMIL FARAZ AHMED 1 ISLAMABAD GARTEN POTOHAR CAMPUS THE CITY SCHOOL WARSAK 11 18-91-05672-1-002-C ESHAAL JASIM MUHAMMAD JASIM 1 PESHAWAR JUNIOR ROOTS IVY INTERNATIONAL 12 18-51-05096-1-005-C FATIMA AHMED IRFAN IRFAN AHMED 1 RAWALPINDI SCHOOL WESTRIDGE CAMPUS KIPS SCHOOL CANAL SIDE 13 18-42-05084-1-001-C FATIMA GORSI HINA GORSI 1 LAHORE CAMPUS FAZAIA INTER COLLEGE 14 18-51-05130-1-001-C HAMZA HAMAYUN MUHAMMAD HAMAYUN 1 RAWALPINDI JINNAH CAMP MUHAMMAD HASSAN ROOTS IVY INTERNATIONAL 15 18-51-05096-1-004-C HAREEM HASSAN 1 RAWALPINDI FAROOQ SCHOOL WESTRIDGE -

LIST of Silver MEDAL WINNERS FIRST POSITION in DISTRICT S

LIST OF Silver MEDAL WINNERS FIRST POSITION IN DISTRICT S. NO. ROLL NO. STUDENT NAME FATHER NAME CLASS INSTITUTION CITY/DISTRICT AGA KHAN HIGHER 1 19-021-05068-12-002-C ABDUL REHMAN KHAN ABDUL WAHEED KHAN 12 KARACHI SECONDARY SCHOOL PUNJAB COLLEGE OF 2 19-42-05314-12-012-C MOEED AHMED MUHAMMAD WAJID 12 LAHORE SCIENCE 3 19-53-05515-12-014-C MOHSIN SHEIKH TAIMOOR JAN 12 MILITARY COLLEGE JHELUM GUJRAT PUNJAB COLLEGE OF 4 19-42-05314-12-010-C MUHAMMAD ANAS MUHAMMAD ABID 12 LAHORE SCIENCE JINNAH EDUCATION SYSTEM 5 19-51-05059-12-006-C MUZAMMIL IFTIKHAR IFTIKHAR AHMED 12 RAWALPINDI IQBAL CAMPUS 6 19-53-05515-12-007-C RANA TAAHA HUSSAIN RANA MUHAMMAD YASIN 12 MILITARY COLLEGE JHELUM GUJRAT ROOTS MILLENNIUM 7 19-582-05163-12-001-C YOUSAF QAMAR QAMAR ZAMAN 12 MIRPUR SCHOOL HILL VIEW CAMPUS THE CITY SCHOOL 8 19-91-05729-11-002-C AFTAB AHMAD QUDRAT KHAN 11 PESHAWAR PESHAWAR CAMPUS 9 19-42-05740-11-007-C SARMAD NAWAZ TARIQ NAWAZ MALIK 11 AITCHISON COLLEGE LAHORE ABDUL RAFAY 10 19-51-05748-10-007-C NAVEED HASSAN 10 PAF COLLEGE LOWER TOPA RAWALPINDI MUGHAZ 11 19-42-05740-10-001-C HASSAAN MOHSIN MOHSIN AZIZ 10 AITCHISON COLLEGE LAHORE MUHAMMAD SHURAIM SARGODHIAN SPIRIT TRUST 12 19-222-05042-10-003-C ABDUL AZIZ 10 TANDOALLAHYAR AZIZ PUBLIC SCHOOL ARMY PUBLIC SCHOOL AND 13 19-55-05737-8-002-C AMNA SHAFAAT ALI SHAFAAT ALI 8 GUJRANWALA COLLEGE 14 19-66-05109-8-002-C AYESHA SALEEM MUHAMMAD SALEEM 8 BLOOMFIELD HALL SCHOOL MUZAFFARGARH MUHAMMAD YOUSAF ARMY PUBLIC SCHOOL & 15 19-40-05660-8-002-C AYESHA YOUSAF 8 SAHIWAL IQBAL COLLEGE ARMY PUBLIC SCHOOL & 16 -

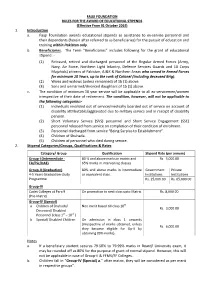

Review of Stipend Rules

FAUJI FOUNDATION RULES FOR THE AWARD OF EDUCATIONAL STIPENDS (Effective From 01 October 2019) 1. Introduction a. Fauji Foundation awards educational stipends as assistance to ex-service personnel and their dependents (herein after referred to as beneficiaries) for the pursuit of education and training within Pakistan only. b. Beneficiaries. The Term “Beneficiaries” includes following for the grant of educational stipend: - (1) Released, retired and discharged personnel of the Regular Armed Forces (Army, Navy, Air Force, Northern Light Infantry, Defence Services Guards and 10 Corps Mujahids) citizens of Pakistan, AJ&K & Northern Areas who served in Armed Forces for minimum 10 Years, up to the rank of Colonel (including deceased Brig). (2) Wives and widows (unless remarried) of 1b (1) above. (3) Sons and unmarried/divorced daughters of 1b (1) above. c. The condition of minimum 10 year service will be applicable to all ex-servicemen/women irrespective of their date of retirement. The condition, however, will not be applicable to the following categories:- (1) Individuals invalided out of service/medically boarded out of service on account of disability attributable/aggravated due to military service and in receipt of disability pension. (2) Short Voluntary Service (SVS) personnel and Short Service Engagement (SSE) personnel released from service on completion of their condition of enrolment. (3) Personnel discharged from service “Being Surplus to Establishment”. (4) Children of Shuhada. (5) Children of personnel who died during service. 2. Stipend Categories/Groups, Qualifications & Rates Category/ Group Qualification Stipend Rate (per annum) Group-I (Intermediate - 80 % and above marks in matric and Rs. 5,000.00 FA/FSc/DAE) 65% marks in intervening classes Group-II (Graduation) 80% and above marks in intermediate Government Private 4-5 Years Graduation study or equivalent class.