Technical Reference Manual for VP 110/01X VME Pentium® III-M Single Board Computer

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

HP T5545 Thin Client Overview

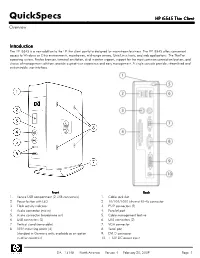

QuickSpecs HP t5545 Thin Client Overview Introduction The HP t5545 is a new addition to the HP thin client portfolio designed for mainstream business. The HP t5545 offers convenient access to Windows or Citrix environments, mainframes, mid-range servers, Unix/Linux hosts, and web applications. The ThinPro operating system, Firefox browser, terminal emulation, dual monitor support, support for the most common connection brokers, and choice of management solutions provide a great user experience and easy management. A single console provides streamlined and customizable user interface. Front Back 1. Secure USB compartment (2 USB connectors) 1. Cable lock slot 2. Power button with LED 2. 10/100/1000 Ethernet RJ-45 connector 3. Flash activity indicator 3. PS/2 connectors (2) 4. Audio connector (mic in) 4. Parallel port 5. Audio connector (headphone out) 5. Cable management feature 6. USB connectors (2) 6. USB connectors (2) 7. Vertical stand (removable) 7. VGA connector 8. VESA mounting points (4) 8. Serial port (standard in Germany only; available as an option 9. DVI-D connector in other countries) 10. +12V DC power input DA - 13148 North America — Version 4 — February 20, 2009 Page 1 QuickSpecs HP t5545 Thin Client Overview At A Glance HP ThinPro operating system supports modular software updates that can be applied remotely over the network for rapid deployment VIA Eden 1 GHz processor for great performance 512 MB System memory (64 MB reserved for video) 512 MB Flash memory Includes one parallel, one serial, two PS/2, and six USB 2.0 ports (two in back, two in front, and two in secure USB compartment – great for safeguarding USB wireless and Flash devices) MIC in and Audio out ports in front Built in dual monitor support (VGA and DVI-D native) HP Device Manager lets you remotely manage client devices from a central location HP's alliance with Altiris brings a leading management solution to the thin client market. -

Lsl-11 VIDEO TERMINAL USER's GUIDE EK-VT103-UG-001

LSl-11 VIDEO TERMINAL USER'S GUIDE EK-VT103-UG-001 VT103 LSl-11 VIDEO TERMINAL USER 1 S GUIDE digital equipment corporation • marlboro, massachusetts Preliminary, June 1979 First Edition, September 1979 Second Printing, March 1980 Copyright © 1979 by Digital Equipment Corporation The material in this manual is for informational purposes and is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual. Printed in U.S.A. This document was set on DIGITAL's DECset-8000 com puterized typesetting system. The following are trademarks of Digital Equipment Corporation. Maynard, Massachusetts: DIGITAL DECsystem-10 MASS BUS DEC DECSYSTEM-20 OMNIBUS PDP DIBOL OS/8 DECUS EDUSYSTEM RSTS UNIBUS VAX RSX VMS IAS CONTENTS PREFACE Page CHAPTER 1 OPERATOR INFORMATION 1 . 1 INTRODUCTION ................................................................................................................................. 1 1.2 CONTROLS AND INDICATORS ...................................................................................................... 1 1.2.1 Monitor Controls ....................................................................................................................... 2 1.2.2 Key boa rd Controls .................................................................................................................... 3 1.2.3 Keyboard Indicators ................................................................................................................. 8 1.2.4 Audible -

HP Integrity Rx7620 Server User Service Guide

HP Integrity rx7620 Server User Service Guide HP Part Number: A7027-96036-ed6 Published: October 2009 Edition: 6 © Copyright 2003-2009 HP Development Company, L.P. Legal Notices The information contained herein is subject to change without notice. The only warranties for HP products and services are set forth in the express warranty statements accompanying such products and services. Nothing herein should be construed as constituting an additional warranty. HP shall not be liable for technical or editorial errors or omissions contained herein. Printed in U.S.A. Intel, Pentium, Intel Inside, Itanium, and the Intel Inside logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. Linux is a U.S. registered trademark of Linus Torvalds. Microsoft and Windows are U.S. registered trademarks of Microsoft Corporation. Warranty To obtain a copy of the warranty for this product, see the warranty information website: BCS Global Limited Warranty and Technical Support Table of Contents About This Document.......................................................................................................13 Intended Audience................................................................................................................................13 New and Changed Information in This Edition...................................................................................13 Publishing History................................................................................................................................13 -

Digital Equipment Corporation VT300 Display Family

Datapro Reports on C25-384-101 Data Communications Terminals Digital Equipment Corporation VT300 Display Family In this report: Product Summary Analysis .................... -102 Editor's Note Competition Digital now offers the VT320, VT320-compatible displays are of Characteristics .......... -104 VT330, and VT340 displays, succes- fered by TeleVideo, Wyse Technol sors to the VT200 family that pro- ogy, Qume Corporation, Pricing ....................... -105 vide complete backward- Microterm, and Hewlett-Packard. compatibility with improved Microterm also offers VT330- and ergonomics and functionality. Digi VT340-compatible displays. AT&T, tal continues to provide service for Falco Data Products, and a few other the older line of displays, however. vendors offer VT320 emulation in their general-purpose ASCII dis Description plays. The VT320 is a monochrome dis play that provides single-session Vendor support for text-oriented applica Digital Equipment Corp. (DEC) tions. The VT330 and VT340 both 146 Main Street provide dual sessions and graphics Maynard, MA 01754-2571 capability. (508) 493-5111 Strengths In addition to introducing dual Price session support with the VT300 fam The North American Version of the ily, Digital designed higher VT320 sells for $575; the interna resolution, faster processing speed, tional version of the display costs and greater customization capability $625. The VT330 and VT340 sell for into the displays while lowering $1,995 and $2,795, respectively. prices significantly. Limitations Vendors such as Wyse Technology, TeleVideo, Microterm, and Hewlett Packard offer VT clones that provide enhancements such as multiple dis play configurations, more function keys and interfacing options, and more internal memory. © 1990 McGraw-Hili. Incorporated. Reproduction Prohibited. -

Download Powerterm Interconnect Datasheet

PowerTerm® InterConnect The complete host access solution in one compact, easy to use program PowerTerm® concurrent sessions, history scroll bar, InterConnect is Ericom® menu bar, scalable and selectable fonts, Software’s original host intelligent copy & paste, FTP client, connectivity solution Intellimouse support, advanced printing for organizations and file transfers between PCs and hosts. requiring fast and This full-feature client ensures fast, reliable accurate access to data connections for sharing residing on a variety of information throughout the hosts, including IBM, enterprise, regardless of host Digital, Unix, SCO and type. PowerTerm Data General. PowerTerm InterConnect offers multi- InterConnect is the language support: The GUI complete Windows solution for 16 and 32-bit multiple- host information access, working on Windows 3.x, Windows 95, Windows 98, Windows NT and Windows 2000 platforms. Seamless connectivity from PC to host The PowerTerm InterConnect terminal emulator maximizes enterprise-wide productivity by enabling reliable access to accounting, inventory management, transaction processing and other mission-critical legacy applications. PowerTerm InterConnect provides seamless connectivity to the widest range of machine types and information systems. (including menu and dialog boxes) is available in English, German, French, Spanish and Italian, Supports a full line of emulation types on while the program supports dozens of other the widest variety of hosts languages. PowerTerm InterConnect supports a full line of IBM, Digital, Wyse, Data General, SCO and other Secure terminal emulation terminal emulation types. Its extremely small PowerTerm InterConnect supports the host access footprint provides a simple, fast and effective needs of large and small organizations alike, means of running legacy applications from within allowing enterprises to standardize on a single Windows 3.x/95/98/NT/2000 platforms. -

TCD-SCSS-T.20191104.002 Accession Date

AccessionIndex: TCD-SCSS-T.20191104.002 Accession Date: 4-Nov-2019 Accession By: Ronan Scaife Object name: DEC MINC-11 laboratory minicomputer Vintage: c.1981 Synopsis: Lab computer plus instrument chassis successor to the original MIT LINC, Model: MINC11-AB, CAB 0, S/N: WF05524. Description: This item is a DEC MINC-11 laboratory minicomputer on a trolley, a later successor to the original MIT LINC that DEC also manufactured. It uses a PDP-11/03 rather than the original LINC processor. The MINC-11 was contained in a 19” chassis, plus a DEC RX02 dual floppy disk drive mounted on a laboratory trolley, with a DEC VT103 intelligent terminal above. It was designed for laboratory use, using special interface modules and (in DEC terminology) double-spaced quad-sized slots. The operating system was a special version of DEC’s RT-11, and booted straight into MINC-Basic, which had special functions to access the MINC modules. FORTRAN IV (Fortran-66) was optionally available for computationally-intensive applications. Lab sensors, actuators or instruments could be linked via BNC connectors at the front of the modules or via a connector block. The PDP-11/03 (aka LSI-11/03) was the first PDP-11 designed with large-scale integration circuits, using the Western Digital MCP-1600 chipset on a KDF11-AA (M8186) Q-bus CPU board, and MSV11-DD (M8044 DH) 32kW (64kB) memory boards. An RXV21 (M8029) floppy disk controller board interfaced to the RX02 dual floppy disk drive. A BDV11 bus terminator board also provides 2kW of PROM for diagnostics and booting. -

MS320®For Windows

MS320® forWindows Version 4.01 Minisoft, Inc. Minisoft Marketing AG 1024 First Street Papiermühleweg 1 Snohomish, WA 98290 Postfach 107 U.S.A. Ch-6048 Horw Switzerland 1-800-682-0200 Phone: +41-41-340 23 20 360-568-6602 Fax: +41-41-340 38 66 Fax: 360-568-2923 www.minisoft.ch Internet access: [email protected] [email protected] http://www.minisoft.com http://www.minisoft.us Disclaimer The information contained in this document is subject to change without notice. Minisoft, Inc. makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Minisoft, Inc. or its agents shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishings, performance, or use of this material. This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or trans- lated to another programming language without the prior written consent of Minisoft, Inc. ©2008 by Minisoft, Inc. Printed in U.S.A. © DCSi All product names and services identified in this document are trademarks or registered trademarks of their respective companies and are used throughout this document in edito- rial fashion only and are not intended to convey an endorsement or other affiliation with Minisoft, Inc. License Agreement READ CAREFULLY BEFORE INSTALLING THE MINISOFT SOFTWARE APPLICATION: CUSTOMER: THE MINISOFT SOFTWARE APPLICATION (“PRODUCT”) THAT YOU PURCHASED CONTAINS COPYRIGHTS, TRADE SECRETS, TRADE MARKS, AND OTHER INTELLECTUAL PROPERTY RIGHTS BELONGING TO MINISOFT, INC. -

L2/98-354 Terminal Graphics for Unicode

L2/98-354 TERMINAL GRAPHICS FOR UNICODE Frank da Cruz The Kermit Project Columbia University New York City USA [email protected] http://www.columbia.edu/kermit/ D R A F T # 4 Tue Nov 3 19:08:58 1998 THIS IS A PREFORMATTED PLAIN-TEXT ASCII DOCUMENT. IT IS DESIGNED TO BE VIEWED AS-IS IN A FIXED-PITCH FONT. ITS WIDEST LINE IS 79 COLUMNS. IT CONTAINS NO TABS. IF IT LOOKS MESSY TO YOU, PLEASE FEEL FREE TO PICK UP A CLEAN COPY OF THIS OR THE RELATED PROPOSALS BY ANONYMOUS FTP: HEX BYTE PICTURES FOR UNICODE (plain text) ftp://kermit.columbia.edu/kermit/ucsterminal/hex.txt ADDITIONAL CONTROL PICTURES FOR UNICODE (plain text) ftp://kermit.columbia.edu/kermit/ucsterminal/control.txt TERMINAL GRAPHICS FOR UNICODE (plain text) ftp://kermit.columbia.edu/kermit/ucsterminal/ucsterminal.txt Glyph Map (PDF, contributed by Michael Everson) ftp://kermit.columbia.edu/kermit/ucsterminal/terminal-emulation.pdf Clarification of SNI Glyphs (Microsoft Word 7.0) ftp://kermit.columbia.edu/kermit/ucsterminal/sni-charsets.doc Discussion (plain text) ftp://kermit.columbia.edu/kermit/ucsterminal/mail.txt (Note, the Exhibits are on paper and not available at the FTP site.) ABSTRACT A selection of terminal graphics characters is proposed for Unicode [24] and ISO 10646 [19] to allow Unicode-based terminal emulation software to display glyphs that are found on popular types of terminals but currently are not available in Unicode, and to exchange these characters with other Unicode-based applications. 1 CONTENTS 1. Introduction 2. Scope 3. Organization 4. (deleted) 5. 3270 Terminal Operator Status Indicators 6. -

Thesis May Never Have Been Completed

UvA-DARE (Digital Academic Repository) Digital Equipment Corporation (DEC): A case study of indecision, innovation and company failure Goodwin, D.T. Publication date 2016 Document Version Final published version Link to publication Citation for published version (APA): Goodwin, D. T. (2016). Digital Equipment Corporation (DEC): A case study of indecision, innovation and company failure. General rights It is not permitted to download or to forward/distribute the text or part of it without the consent of the author(s) and/or copyright holder(s), other than for strictly personal, individual use, unless the work is under an open content license (like Creative Commons). Disclaimer/Complaints regulations If you believe that digital publication of certain material infringes any of your rights or (privacy) interests, please let the Library know, stating your reasons. In case of a legitimate complaint, the Library will make the material inaccessible and/or remove it from the website. Please Ask the Library: https://uba.uva.nl/en/contact, or a letter to: Library of the University of Amsterdam, Secretariat, Singel 425, 1012 WP Amsterdam, The Netherlands. You will be contacted as soon as possible. UvA-DARE is a service provided by the library of the University of Amsterdam (https://dare.uva.nl) Download date:26 Sep 2021 Digital Equipment Corporation (DEC) (DEC) Corporation Digital Equipment David Thomas David Goodwin Digital Equipment Corporation (DEC): A Case Study of Indecision, Innovation and Company Failure David Thomas Goodwin Digital Equipment Corporation (DEC): A Case Study of Indecision, Innovation and Company Failure David Thomas Goodwin 1 Digital Equipment Corporation (DEC): A Case Study of Indecision, Innovation and Company Failure ACADEMISCH PROEFSCHRIFT ter verkrijging van de graad van doctor aan de Universiteit van Amsterdam op gezag van de Rector Magnificus prof. -

PDP-11 Systems and Options Catalog

Systems & Options Catalog October-December 1983 The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any error that may appear in this catalog. This Product Catalog was designed, produced, and typeset by Digital's Corporate Marketing Services using an in-house text-processing system. Correspondent, DATATRIEVE, DEC, DECmate, DECnet, DECmailer, DECstart, DECword, DECword/DP, DECwriter, Digital logo, FALCON, FMS-11, lAS, Internet, LA, Letterprinter 100, Letterwriter 1 00, MICRO/PDP-11 , MICRO/J-11 , MICRO/PDP-11, MICRO/T-11, MicroPower/Pascal, PACKETNET, PDP, P/OS, Professional 325 and 350, PROVUE, Q-bus, Rainbow 100, ReGIS, RSTS, RSX, RT-11 , UNIBUS, VAX, VMS, VT are trademarks of Digital Equipment Corporation. COPYRIGH"f©1983 DIGITAL EQUIPMENT CORPORATION New Products From DIGITAL MICRO/PDP-11-the performance of a minicomputer in a compact, economical microcomputer. Now there is Micro/RSX, especially designed for use on the MICRO/PDP-11. New Packaging for PDP-11/24s and PDP-11/44s- from boxes to building blocks to complete packaged sys tems. New Q-bus Mass Storage Packaging -Adds 10MB to the MICRO/PDP-11 -Adds removable floppies to Q-bus systems Table of Contents Introduction . Overview and How to Use . ii Ordering and Configuring Information. iv Supporting Products . viii Systems . ......... · 1-1 System Selection Chart . · 1-3 Q-bus System Chart. · 1-5 MICRO/PDP-11 Computer Models & Systems. · 1-8 PDP-11 /23-PLUS Computer Models & Systems. 1-12 UNIBUS System Chart. -

Manufacturing News Lnformation for HP Sales Reps Selling MIS, Office Automation, and Manufacturing Solutions April 1,1986

Yew HP LaserJet 500 PLUS printer I see story on page 19 Information Systems s, Manufacturing News lnformation for HP sales reps selling MIS, office automation, and manufacturing solutions April 1,1986 The Portable Plus enhanced - ' LCD display '1 Up to 1 -28 of memory HEWLETT For HP Use Only PACKARD MARKETING8 INTERNATIONALSECTOA lnformation Systems s EyJ@-hd&zmUS Field Operations Wmb3w& MapAcivmts hogram FMO FedaalMark DMK LhrectMark%- Manufacturing News CVCM VabAdded CMManagement Vol. 11, No. 11 m RW suppott nvlsicol FRD Fmand Remarkelnw Dm CorpmateMarkehng Camn-Wrs Formerly Computer News INFORMATION SYSTEMS (L NETWDRKS SECTOR Information Svstema Cmuv(ISG) OD O&esystemsm Editor om CmiCeRoductintyDi* PSD PemdSoftwareMbn Roman Kichorowsky EGD wenGeneral Systems Mn KO Chdalajara Cmwter Operatnn Personal computer (PC& Assistant Editors RTD Rose* Temimb Division HFW F'uertoRicoOpemfiop, Tracy Wester KD Portable Coquter Divsan BPC BdOperation Darleen Brettes +lCCQ GXnputer & CahJator Openti GFCD Grembk Personalhpter Di- m PdOlfreComputer Divisian Mia~tadOrasHP & PCS SngdporeOperation Information Systems Manufacturing News is pub- Kc0 P~CanplterDklributionOpetah lished biweekly for Hewlett-Packard field personnel to Perioherals GmuomG) help you sell HP solutions by organizing, summarizing, G~D'CB ~reeleiDivisian-W Peripherals BristoIDivision ';TO Greeley TwOpsa&,n and highlighting sales and marketing information. DMD DiscMWDivision €0 Baselhvlvon VCD V~ver~on KO Ink-JetCmqnnents Cpatlon Address editorial correspondence to lnformation Sys- Yx Sankg0l)muon tems & MunufacturingNews, Hewlett-Packard Com- BR3 Barcelo~Penpkrak~tan pany, Building 20BV, 3000 Hanover Street, Palo Alto, cw Cdrnada~etwmks-Opmatm GND Gremble Networks D~mon CA 94304-0890 USA, COMSYS 0000. WD RasevdleNetworksD~nsmn IND Mormatmn Networks [km InformalirmTechnolacv Gmuv (ITG) Please send address changes and subscription FIDIW Fort~dlmsl~Di&~InlmnathHardwaxe Operatan Iso InlmhSoftware Operation requests* to COMPUTER NEWS, HPDesk ESO Enhy Systam Operaban HP0000153. -

VT1000/VT1200 & Decimage User Guide

This document was prepared and published by Educational Services Development and Publishing, Digital Equipment Corporation. Installing and Using The VT1000 Video Terminal Order Number EK–V1000–UG–002 Digital Equipment Corporation First Edition, February 1990 Second Edition, June 1990 The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document. The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies. Restricted Rights: Use, duplication, or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph(c)(1)(ii)oftheRights in Technical Data and Computer Software clause at DFARS 252.227–7013. Copyright © by Digital Equipment Corporation 1990 All Rights Reserved. Printed in Taiwan. FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.