Timing Solutions for Ethernet AVB Networks.Fm

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Time-Synchronized Data Collection in Smart Grids Through Ipv6 Over

Time-synchronized Data Collection in Smart Grids through IPv6 over BLE Stanley Nwabuona Markus Schuss Simon Mayer Pro2Future GmbH Graz University of Technology Pro2Future GmbH and Graz Graz, Austria Graz, Austria University of Technology [email protected] [email protected] Graz, Austria [email protected] Konrad Diwold Lukas Krammer Alfred Einfalt Siemens Corporate Siemens Corporate Siemens Corporate Technology Technology Technology Vienna, Austria Vienna, Austria Vienna, Austria [email protected] [email protected] [email protected] ABSTRACT INTRODUCTION For the operation of electrical distribution system an increased Due to the progressing integration of distributed energy re- shift towards smart grid operation can be observed. This shift sources (such as domestic photovoltaics) into the distribution provides operators with a high level of reliability and efficiency grid [5], conventional – mostly passive – monitoring and con- when dealing with highly dynamic distribution grids. Techni- trol schemes of power systems are no longer applicable. This cally, this implies that the support for a bidirectional flow of is because these are not designed to handle and manage the data is critical to realizing smart grid operation, culminating in volatile and dynamic behavior stemming from these new active the demand for equipping grid entities (such as sensors) with grid entities. Therefore, advanced controlling and monitoring communication and processing capabilities. Unfortunately, schemes are required for distribution grid operation (i.e., in- the retrofitting of brown-field electric substations in distribu- cluding in Low-Voltage (LV) grids) to avoid system overload tion grids with these capabilities is not straightforward – this which could incur permanent damages. -

Ieee 802.1 for Homenet

IEEE802.org/1 IEEE 802.1 FOR HOMENET March 14, 2013 IEEE 802.1 for Homenet 2 Authors IEEE 802.1 for Homenet 3 IEEE 802.1 Task Groups • Interworking (IWK, Stephen Haddock) • Internetworking among 802 LANs, MANs and other wide area networks • Time Sensitive Networks (TSN, Michael David Johas Teener) • Formerly called Audio Video Bridging (AVB) Task Group • Time-synchronized low latency streaming services through IEEE 802 networks • Data Center Bridging (DCB, Pat Thaler) • Enhancements to existing 802.1 bridge specifications to satisfy the requirements of protocols and applications in the data center, e.g. • Security (Mick Seaman) • Maintenance (Glenn Parsons) IEEE 802.1 for Homenet 4 Basic Principles • MAC addresses are “identifier” addresses, not “location” addresses • This is a major Layer 2 value, not a defect! • Bridge forwarding is based on • Destination MAC • VLAN ID (VID) • Frame filtering for only forwarding to proper outbound ports(s) • Frame is forwarded to every port (except for reception port) within the frame's VLAN if it is not known where to send it • Filter (unnecessary) ports if it is known where to send the frame (e.g. frame is only forwarded towards the destination) • Quality of Service (QoS) is implemented after the forwarding decision based on • Priority • Drop Eligibility • Time IEEE 802.1 for Homenet 5 Data Plane Today • 802.1Q today is 802.Q-2011 (Revision 2013 is ongoing) • Note that if the year is not given in the name of the standard, then it refers to the latest revision, e.g. today 802.1Q = 802.1Q-2011 and 802.1D -

Implementing an IEEE 1588 V2 on I.MX RT Using Ptpd, Freertos, and Lwip TCP/IP Stack

NXP Semiconductors Document Number: AN12149 Application Note Rev. 1 , 09/2018 Implementing an IEEE 1588 V2 on i.MX RT Using PTPd, FreeRTOS, and lwIP TCP/IP stack 1. Introduction Contents This application note describes the implementation of 1. Introduction .........................................................................1 the IEEE 1588 V2 Precision Time Protocol (PTP) on 2. IEEE 1588 basic overview ..................................................2 2.1. Synchronization principle ........................................ 3 the i.MX RT MCUs running FreeRTOS OS. The IEEE 2.2. Timestamping ........................................................... 5 1588 standard provides accurate clock synchronization 3. IEEE 1588 functions on i.MX RT .......................................6 for distributed control nodes in industrial automation 3.1. Adjustable timer module .......................................... 6 3.2. Transmit timestamping ............................................. 8 applications. 3.3. Receive timestamping .............................................. 8 3.4. Time synchronization ............................................... 8 The implementation runs on the i.MX RT10xx 3.5. Input capture and output compare block .................. 8 Evaluation Kit (EVK) board with i.MX RT10xx MCUs. 4. IEEE 1588 implementation for i.MX RT ............................9 The demo software is based on the NXP MCUXpresso 4.1. Hardware components .............................................. 9 4.2. Software components ............................................ -

Publication Title 1-1962

publication_title print_identifier online_identifier publisher_name date_monograph_published_print 1-1962 - AIEE General Principles Upon Which Temperature 978-1-5044-0149-4 IEEE 1962 Limits Are Based in the rating of Electric Equipment 1-1969 - IEEE General Priniciples for Temperature Limits in the 978-1-5044-0150-0 IEEE 1968 Rating of Electric Equipment 1-1986 - IEEE Standard General Principles for Temperature Limits in the Rating of Electric Equipment and for the 978-0-7381-2985-3 IEEE 1986 Evaluation of Electrical Insulation 1-2000 - IEEE Recommended Practice - General Principles for Temperature Limits in the Rating of Electrical Equipment and 978-0-7381-2717-0 IEEE 2001 for the Evaluation of Electrical Insulation 100-2000 - The Authoritative Dictionary of IEEE Standards 978-0-7381-2601-2 IEEE 2000 Terms, Seventh Edition 1000-1987 - An American National Standard IEEE Standard for 0-7381-4593-9 IEEE 1988 Mechanical Core Specifications for Microcomputers 1000-1987 - IEEE Standard for an 8-Bit Backplane Interface: 978-0-7381-2756-9 IEEE 1988 STEbus 1001-1988 - IEEE Guide for Interfacing Dispersed Storage and 0-7381-4134-8 IEEE 1989 Generation Facilities With Electric Utility Systems 1002-1987 - IEEE Standard Taxonomy for Software Engineering 0-7381-0399-3 IEEE 1987 Standards 1003.0-1995 - Guide to the POSIX(R) Open System 978-0-7381-3138-2 IEEE 1994 Environment (OSE) 1003.1, 2004 Edition - IEEE Standard for Information Technology - Portable Operating System Interface (POSIX(R)) - 978-0-7381-4040-7 IEEE 2004 Base Definitions 1003.1, 2013 -

XMOS for AVB Ethernet Based Networking for Audio/Video

Only a few years ago, computer networks were complex beasts tended by special acolytes and running on different standards. Today they have become commonplace in many homes and offices, simply plugged together using Ethernet technology. The same revolutionary change is coming for Audio/Video (AV) networking, as AVB (Audio XMOS for AVB: Video Bridging) products that run over the same network, Ethernet based networking begin to enter the market. for Audio/Video Putting together networks of AV equipment for professional and consumer use, or for use in How Ethernet Works vehicles, is about to become simpler while also Within Ethernet, data is transmitted between delivering better quality. No longer will devices (such as a computer and a printer) in specialist connectors and cables be needed to packets. Each packet carries one or more create a rats' nest of connectivity. Instead addresses for its destination. Like a postal packet traversing the postal system, the network has no Audio Video Bridging (AVB), a set of knowledge of what is in the packet, but uses the international standards, will make setting up address to pass the packet to the next point in the and managing networks almost as simple as network. just plugging together the different elements. In an Ethernet based network, each endpoint Sound and video sources will be mixed and (computer, storage element, printer etc.) is distributed to screens and speakers, with high identified by a unique address and has a single quality, low latency and tight synchronization. connection to the network, through an Ethernet Furthermore, the connectors and cables are switch. -

Software Architecture for a Multiple AVB Listener and Talker Scenario

Software Architecture for a Multiple AVB Listener and Talker Scenario Christoph Kuhr and Alexander Car^ot Department of Computer Sciences and Languages, Anhalt University of Applied Sciences Lohmannstr. 23, 06366 K¨othen, Germany, fchristoph.kuhr, [email protected] Abstract 1.2 Concept for a Realtime Processing Cloud This paper presents a design approach for an AVB network segment deploying two differ- A specialized and scalable server infrastructure ent types of AVB server for multiple paral- is required to provide the realtime streaming re- lel streams. The first type is an UDP proxy quirements of this research project. The ser- server and the second server type is a digital vice time property of an Ethernet frame arriv- signal processing server. The Linux real time ing on a serial network interface at the wide area operating system configurations are discussed, network (WAN) side of this server cloud, is of as well as the software architecture itself and paramount importance for the software design. the integration of the Jack audio server. A During the service time of a single UDP stream proper operation of the JACK server, along- datagram, no concurrent stream datagrams can side two JACK clients, in this multiprocess- be received. Thus, the latencies of all streams ing environment could be shown, although a arriving on such an interface are accumulated. persisting buffer leak prevents significant jitter In addition to connecting the 60 streams to and latency measurements. A coarse assessment each other, the Soundjack cloud provides dig- shows however, that the operations are within ital signal processing algorithms for audio and reasonable bounds. -

Extremexos® Operating System

Data Sheet Highlights ExtremeXOS has a robust set of Layer 2 and Layer 3 control protocols, provides a flexible architecture for highly resilient networks and has been designed to support the nextgeneration Internet Protocol, IPv6. ExtremeXOS is a highly available and extensible software foundation for converged networks. ExtremeXOS offers high availability for carriergrade voice and video services over IP and for supporting mission- critical business applications such as CRM. • Modular Operating System • High Availability Architecture • Rich set of Layer-2 and Layer-3 ® protocols and features ExtremeXOS Operating System • Secure Network Access through role Version 16.2, 21.1, 22.7, and 30.4 based policy or Identity Management • Extensibility • Integrated Security with NetLogin, Overview MAC Security, IP Security Extreme Networks has created the ExtremeXOS modular Operating • User, location, and time-based System (OS) – for highly available, extensible, high-performance networks. dynamic security policies with ExtremeXOS high availability architecture with EAPS protocol helps reduce Identity Management network downtime for business continuity and access to mission-critical • Insight, control and automation for applications such as CRM, data warehouses and VoIP for carrier and voice virtualized data centers with XNV grade networks. (ExtremeXOS Network Virtualization) • Enhanced resiliency, Built-in security capabilities provide network access control integrated with synchronization, performance for endpoint integrity checking, identity management, and protection for the 2G/3G/4G mobile backhaul network control and management planes. • ExtremeXOS InSite SDK Software Defined Networking Ready with With ExtremeXOS you can extend the capabilities of your network by OpenFlow and OpenStack support integrating specialized application appliances such as security devices into • Ethernet Audio Video Bridging the network, providing insight and control at the network, application and (AVB) enabled user level. -

7-Port Gigabit Ethernet Switch with Audio Video Bridging and Two RGMII/MII/RMII Interfaces

KSZ9567R 7-Port Gigabit Ethernet Switch with Audio Video Bridging and Two RGMII/MII/RMII Interfaces Highlights • Five Integrated PHY Ports - 1000BASE-T/100BASE-TX/10BASE-Te IEEE 802.3 • Non-blocking wire-speed Ethernet switching fabric - Fast Link-up option significantly reduces link-up time • Full-featured forwarding and filtering control, includ- - Auto-negotiation and Auto-MDI/MDI-X support ing Access Control List (ACL) filtering - On-chip termination resistors and internal biasing for • Full VLAN and QoS support differential pairs to reduce power • Five ports with integrated 10/100/1000BASE-T PHY - LinkMD® cable diagnostic capabilities for determining transceivers cable opens, shorts, and length • Two ports with 10/100/1000 Ethernet MACs and con- • Advanced Switch Capabilities figurable RGMII/MII/RMII interfaces - IEEE 802.1Q VLAN support for 128 active VLAN • IEEE 1588v2 Precision Time Protocol (PTP) support groups and the full range of 4096 VLAN IDs - IEEE 802.1p/Q tag insertion/removal on per port basis • IEEE 802.1AS/Qav Audio Video Bridging (AVB) - VLAN ID on per port or VLAN basis • IEEE 802.1X access control support - IEEE 802.3x full-duplex flow control and half-duplex • EtherGreen™ power management features, back pressure collision control including low power standby - IEEE 802.1X access control 2 • Flexible management interface options: SPI, I C, (Port-based and MAC address based) MIIM, and in-band management via any port - IGMP v1/v2/v3 snooping for multicast packet filtering • Industrial temperature range support - IPv6 -

Schedulability Analysis of Ethernet Audio Video Bridging Networks with Scheduled Traffic Support

Real-Time Syst DOI 10.1007/s11241-017-9268-5 Schedulability analysis of Ethernet Audio Video Bridging networks with scheduled traffic support Mohammad Ashjaei1 · Gaetano Patti2 · Moris Behnam1 · Thomas Nolte1 · Giuliana Alderisi2 · LuciaLoBello2 © The Author(s) 2017. This article is published with open access at Springerlink.com Abstract The IEEE Audio Video Bridging (AVB)technology is nowadays under con- sideration in several automation domains, such as, automotive, avionics, and industrial communications. AVB offers several benefits, such as open specifications, the exis- tence of multiple providers of electronic components, and the real-time support, as AVB provides bounded latency to real-time traffic classes. In addition to the above men- tioned properties, in the automotive domain, comparing with the existing in-vehicle networks, AVB offers significant advantages in terms of high bandwidth, signifi- cant reduction of cabling costs, thickness and weight, while meeting the challenging EMC/EMI requirements. Recently, an improvement of the AVB protocol, called the AVB ST, was proposed in the literature, which allows for supporting scheduled traffic, i.e., a class of time-sensitive traffic that requires time-driven transmission and low latency. In this paper, we present a schedulability analysis for the real-time traffic crossing through the AVB ST network. In addition, we formally prove that, if the bandwidth in the network is allocated according to the AVB standard, the schedula- bility test based on response time analysis will fail for most cases even if, in reality, these cases are schedulable. In order to provide guarantees based on analysis test a bandwidth over-reservation is required. -

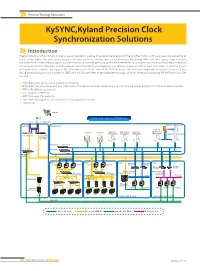

Kysync,Kyland Precision Clock Synchronization Solutions

Precise Timing Solutions KySYNC,Kyland Precision Clock Synchronization Solutions Introduction Precision clock synchronization solutions are using external precise time reference to establish the synchronization with local clocks by delivering all kinds of time signal. The time source provides the time reference, and the time server distributes the timing. While the time source is not available, the time server’s time keeping ability will be critical to assure the precision of the time reference. So in a precision clock synchronization network, the precision of time reference, time distribution and time keeping are hook-ups and all plays important role in each time node. In order to ensure all legacy devices which only support IRIG-B format could still be synced, the PTP (Precision Time Protocol) signal will need to be converted into IRIG-B format through clock conversion. IEEE 1588 will also be need to be distributed through all kinds of network including PRP/HSR and also SDH network. Kyland provides turnkey timing solution including: High-precision time server and IEEE 1588 industrial Ethernet switches supporting IEEE 1588 in both power profile (C37.238) and telecom profile PTP to IRIG-B time conversion IEEE 1588 over PRP/HSR IEEE 1588 over SDH network TMS (Time Management System) & Service Management System Time tester Satellite KySYNC, Intelligent Gateway, PRP/HSR Solution E1/T1 GPS Antenna Remote Control Center KySYNC Station Level Protection Engineering Server A Sever B Operation Maintenance Operation Workstation Workstation Workstation -

ORPHEUS Deliverable Template

Grant Agreement No.: 687645 Research and Innovation action Call Topic: H2020 ICT-19-2015 Object-based broadcasting – for European leadership in next generation audio experiences D4.1: Requirements for Representation, Archiving and Provision of Object-based Audio Version: v1.4 Deliverable type R (Document, report) Dissemination level PU (Public) Due date 01/06/2016 Submission date 17/06/2016 Lead editor Andreas Silzle (FHG) Authors Andrew Mason (BBC), Michael Meier (IRT), Simone Füg (FHG), Andreas Silzle (FHG) Reviewers Niels Bogaards (Elephantcandy), Halid Hrasnica (EURES) Work package, Task WP 4, T4.1, T4.2, and T4.3 Keywords File and streaming formats, BW64, meta data, ADM, MPEG-H Abstract This deliverable describes the requirements for representation, archiving and provision of object- based audio. Representation includes file and streaming formats for object-based audio. Provision is the distribution to end-user, including IP delivery, unicast streams and file downloads. For both file and streaming formats interoperable metadata have to be used. Among the requirements for the different formats are metadata support, existing standards, file size, compression, and support of advanced audio. The most important requirements for streaming formats are related to synchronization, existing standards, unicast and multicast transmission, latency, bitrate reduction, synchronization of audio signals, quality of service and specific requirements for streaming object- based audio metadata. Constrains and requirements of interoperability between -

Timing Needs in Cable Networks

Timing Needs in Cable Networks Yair Neugeboren Director System Architecture, Network and Cloud, ARRIS ITSF 2017 Outline • What is a Cable Network? • Timing Aspects in Cable • Distributed Architecture and Timing Requirements • Mobile Backhaul Support through Cable Networks Copyright 2017 – ARRIS Enterprises, LLC. All rights reserved 09 October 2017 2 Outline • What is a Cable Network? • Timing Aspects in Cable • Distributed Architecture and Timing Requirements • Mobile Backhaul Support through Cable Networks Copyright 2017 – ARRIS Enterprises, LLC. All rights reserved 09 October 2017 3 Cable Services Delivery - Today Commercial Residential Web Surf + OTT Video Voice Data Video Video Digital Analog Telephone Services Services Conferencing On Demand Television Television Gaming HFC Channelized Network Downstream [MHz] Copyright 2017 – ARRIS Enterprises, LLC. All rights reserved 09 October 2017 5 What is DOCSIS? The cable TV industry came together in the late 90’s and set up a group called CableLabs They created a set of specifications called Data Over Cable Service Interface Specifications, or DOCSIS for short DOCSIS defines the electrical and logical interfaces specification for network and RF elements in a cable network DOCSIS is a Point to Multipoint Protocol Downstream is continuous “One to Many” Upstream is dynamically scheduled BW allocation DOCSIS versions are 1.0, 1.1, 2.0, 3.0 and 3.1 Copyright 2017 – ARRIS Enterprises, LLC. All rights reserved 09 October 2017 6 Customer Assurance Lawful Cable Network TopologyRecord / Billing Systems Enforcement Back Office Northbound API The HFC network provides the communications link between the CMTS/CCAP and the stations, STBs, CMs and eMTAs. SDN Controller Abstrac on & Applica on HFC plant consists of up to ~160 km of optical fiber, fewLogi chundred meters of coaxial cable, RF distributions and Amplifiers.