High Power Bipolar Junction Transistors in Silicon Carbide

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

CHAPTER 8: Diffusion

1 Chapter 8 CHAPTER 8: Diffusion Diffusion and ion implantation are the two key processes to introduce a controlled amount of dopants into semiconductors and to alter the conductivity type. Figure 8.1 compares these two techniques and the resulting dopant profiles. In the diffusion process, the dopant atoms are introduced from the gas phase of by using doped-oxide sources. The doping concentration decreases monotonically from the surface, and the in-depth distribution of the dopant is determined mainly by the temperature and diffusion time. Figure 8.1b reveals the ion implantation process, which will be discussed in Chapter 9. Generally speaking, diffusion and ion implantation complement each other. For instance, diffusion is used to form a deep junction, such as an n-tub in a CMOS device, while ion implantation is utilized to form a shallow junction, like a source / drain junction of a MOSFET. Boron is the most common p-type impurity in silicon, whereas arsenic and phosphorus are used extensively as n-type dopants. These three elements are highly soluble in silicon with solubilities exceeding 5 x 1020 atoms / cm3 in the diffusion temperature range (between 800oC and 1200oC). These dopants can be introduced via several means, including solid sources (BN for B, As2O3 for As, and P2O5 for P), liquid sources (BBr3, AsCl3, and POCl3), and gaseous sources (B2H6, AsH3, and PH3). Usually, the gaseous source is transported to the semiconductor surface by an inert gas (e.g. N2) and is then reduced at the surface. 2 Chapter 8 Figure 8.1: Comparison of (a) diffusion and (b) ion implantation for the selective introduction of dopants into a semiconductor substrate. -

Which Pnictogen Is Best?† Cite This: New J

NJC PAPER Pnictogen bonding with alkoxide cages: which pnictogen is best?† Cite this: New J. Chem., 2019, 43,14305 Henry J. Trubenstein, ‡ Shiva Moaven, ‡ Maythe Vega, Daniel K. Unruh and Anthony F. Cozzolino * Pnictogen bonding is beginning to emerge as a useful supramolecular interaction. The design strategies for these systems are still in the early stages of development and much attention has been focused on the lighter pnictogens. Pnictogen bond donors can have up to three independent sites for binding which can result in triple pnictogen bonding. This has been observed in the self-assembly of antimony alkoxide cages, but not with the lighter congeners. This work reports structural characterization of an analogous arsenic alkoxide cage that engages in a single pnictogen bond and synthetic explorations of Received 14th July 2019, the bismuth congener. DFT calculations are used to evaluate the differences between the structures. Accepted 13th August 2019 Ultimately the partial charge on the pnictogen and the energy of the pnictogen lone pair dictate the DOI: 10.1039/c9nj03648b strength, orientation and number of pnictogen bonds that these cages form. Antimony cages strike the best balance between strength and directionality, allowing them to achieve triple pnictogen bonding rsc.li/njc where the other congeners do not. Introduction or bismuth.15–23 Recently, antimony centred PnBs have been purposefully designed into molecules to actively direct the self- A pnictogen bond (PnB), in analogy to a halogen or chalcogen assembly of reversed bilayer vesicles,24 enable anion binding bond (XB/HaB or ChB), is ‘‘the net attractive interaction between with applications in sensing and transport,25–28 self-assembly an electrophilic region associated with a [pnictogen] atom in a complex architectures through triple pnictogen bonding29 and molecular entity [the PnB donor] and a nucleophilic region in allow for supramolecular catalysis.30 These applications rely on another, or the same, molecular entity [the PnB acceptor].’’1 the predictable formation of PnBs. -

An Integrated Semiconductor Device Enabling Non-Optical Genome Sequencing

ARTICLE doi:10.1038/nature10242 An integrated semiconductor device enabling non-optical genome sequencing Jonathan M. Rothberg1, Wolfgang Hinz1, Todd M. Rearick1, Jonathan Schultz1, William Mileski1, Mel Davey1, John H. Leamon1, Kim Johnson1, Mark J. Milgrew1, Matthew Edwards1, Jeremy Hoon1, Jan F. Simons1, David Marran1, Jason W. Myers1, John F. Davidson1, Annika Branting1, John R. Nobile1, Bernard P. Puc1, David Light1, Travis A. Clark1, Martin Huber1, Jeffrey T. Branciforte1, Isaac B. Stoner1, Simon E. Cawley1, Michael Lyons1, Yutao Fu1, Nils Homer1, Marina Sedova1, Xin Miao1, Brian Reed1, Jeffrey Sabina1, Erika Feierstein1, Michelle Schorn1, Mohammad Alanjary1, Eileen Dimalanta1, Devin Dressman1, Rachel Kasinskas1, Tanya Sokolsky1, Jacqueline A. Fidanza1, Eugeni Namsaraev1, Kevin J. McKernan1, Alan Williams1, G. Thomas Roth1 & James Bustillo1 The seminal importance of DNA sequencing to the life sciences, biotechnology and medicine has driven the search for more scalable and lower-cost solutions. Here we describe a DNA sequencing technology in which scalable, low-cost semiconductor manufacturing techniques are used to make an integrated circuit able to directly perform non-optical DNA sequencing of genomes. Sequence data are obtained by directly sensing the ions produced by template-directed DNA polymerase synthesis using all-natural nucleotides on this massively parallel semiconductor-sensing device or ion chip. The ion chip contains ion-sensitive, field-effect transistor-based sensors in perfect register with 1.2 million wells, which provide confinement and allow parallel, simultaneous detection of independent sequencing reactions. Use of the most widely used technology for constructing integrated circuits, the complementary metal-oxide semiconductor (CMOS) process, allows for low-cost, large-scale production and scaling of the device to higher densities and larger array sizes. -

Chapter Iii Power Bipolar Junction Transistor (Bjt)

50 CHAPTER III POWER BIPOLAR JUNCTION TRANSISTOR (BJT) 3.1 INTRODUCTION Switching time and switching losses are primary concerns in high power applications. These two factors can significantly influence the frequency of operation and the efficiency of the circuit. Ideally, a high power switch should be able to turn-on and turn-off controllably and with minimum switching loss. The Bipolar junction transistor is an important power semiconductor device used as a switch in a wide variety of applications. The switching speed of a BJT is often limited by the excess minority charge storage in the base and collector regions of the transistor during the saturation state. The conventional methods for improving the switching frequency by reducing the lifetime of the lightly doped collector region through incorporation of impurities such as Au, Pt or by introducing radiation-induced defects have been found unsuitable for high voltage devices due to increased leakage, soft breakdown and high ‘ON’ state voltage [27]. Among the techniques proposed to overcome these problems, use of universal contact (UC) [2, 14] is particularly promising. The present work looks in detail at the various aspects arising out of incorporation of UC in BJTs. The UC is incorporated in the transistor by creating additional diffused regions in an otherwise conventional transistor. These diffused regions influence the minority carrier distribution, nature of minority current flow and also some other parameter such as VCE(sat). To study these phenomena, 51 an analytical model is developed and is utilized to understand the effect of universal contact on reverse recovery, VCE(sat) and other related issues. -

Vlsi Design Lecture Notes B.Tech (Iv Year – I Sem) (2018-19)

VLSI DESIGN LECTURE NOTES B.TECH (IV YEAR – I SEM) (2018-19) Prepared by Dr. V.M. Senthilkumar, Professor/ECE & Ms.M.Anusha, AP/ECE Department of Electronics and Communication Engineering MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) Recognized under 2(f) and 12 (B) of UGC ACT 1956 (Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – ‘A’ Grade - ISO 9001:2015 Certified) Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India Unit -1 IC Technologies, MOS & Bi CMOS Circuits Unit -1 IC Technologies, MOS & Bi CMOS Circuits UNIT-I IC Technologies Introduction Basic Electrical Properties of MOS and BiCMOS Circuits MOS I - V relationships DS DS PMOS MOS transistor Threshold Voltage - VT figure of NMOS merit-ω0 Transconductance-g , g ; CMOS m ds Pass transistor & NMOS Inverter, Various BiCMOS pull ups, CMOS Inverter Technologies analysis and design Bi-CMOS Inverters Unit -1 IC Technologies, MOS & Bi CMOS Circuits INTRODUCTION TO IC TECHNOLOGY The development of electronics endless with invention of vaccum tubes and associated electronic circuits. This activity termed as vaccum tube electronics, afterward the evolution of solid state devices and consequent development of integrated circuits are responsible for the present status of communication, computing and instrumentation. • The first vaccum tube diode was invented by john ambrase Fleming in 1904. • The vaccum triode was invented by lee de forest in 1906. Early developments of the Integrated Circuit (IC) go back to 1949. German engineer Werner Jacobi filed a patent for an IC like semiconductor amplifying device showing five transistors on a common substrate in a 2-stage amplifier arrangement. -

INA106: Precision Gain = 10 Differential Amplifier Datasheet

INA106 IN A1 06 IN A106 SBOS152A – AUGUST 1987 – REVISED OCTOBER 2003 Precision Gain = 10 DIFFERENTIAL AMPLIFIER FEATURES APPLICATIONS ● ACCURATE GAIN: ±0.025% max ● G = 10 DIFFERENTIAL AMPLIFIER ● HIGH COMMON-MODE REJECTION: 86dB min ● G = +10 AMPLIFIER ● NONLINEARITY: 0.001% max ● G = –10 AMPLIFIER ● EASY TO USE ● G = +11 AMPLIFIER ● PLASTIC 8-PIN DIP, SO-8 SOIC ● INSTRUMENTATION AMPLIFIER PACKAGES DESCRIPTION R1 R2 10kΩ 100kΩ 2 5 The INA106 is a monolithic Gain = 10 differential amplifier –In Sense consisting of a precision op amp and on-chip metal film 7 resistors. The resistors are laser trimmed for accurate gain V+ and high common-mode rejection. Excellent TCR tracking 6 of the resistors maintains gain accuracy and common-mode Output rejection over temperature. 4 V– The differential amplifier is the foundation of many com- R3 R4 10kΩ 100kΩ monly used circuits. The INA106 provides this precision 3 1 circuit function without using an expensive resistor network. +In Reference The INA106 is available in 8-pin plastic DIP and SO-8 surface-mount packages. Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners. PRODUCTION DATA information is current as of publication date. Copyright © 1987-2003, Texas Instruments Incorporated Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. www.ti.com SPECIFICATIONS ELECTRICAL ° ± At +25 C, VS = 15V, unless otherwise specified. -

Download Technical Paper

TECHNICAL PAPER Thermal and Electrical Breakdown Versus Reliability of Ta2O5 under Both – Bipolar Biasing Conditions P. Vašina, T. Zedníček, Z. Sita AVX Czech Republic, s.r.o., Dvorakova 328, 563 01 Lanskroun, Czech Republic J. Sikula and J. Pavelka CNRL TU Brno, Technicka 8, 602 00 Brno, Czech Republic Abstract: Our investigation of breakdown is mainly oriented to find a basic parameters describing the phenomena as well as its impact on reliability and quality of the final product that is “GOOD” tantalum capacitor. Basically, breakdown can be produced by a number of successive processes: thermal breakdown because of increasing conductance by Joule heating, avalanche and field emission break, an electromechanical collapse due to the attractive forces between electrodes electrochemical deterioration, dendrite formation and so on. Breakdown causes destruction in the insulator and across the electrodes mainly by melting and evaporation, sometimes followed by ignition. An identification of breakdown nature can be achieved from VA characteristics. Therefore, we have investigated the operating parameters both in the normal mode, Ta is a positive electrode, as well as in the reverse mode with Ta as a negative one. In the reverse mode we have reported that the thermal breakdown is initiated by an increase of the electrical conductance by Joule heating. Consequently followed in a feedback cycle consisting of temperature - conductivity - current - Joule heat - temperature. In normal mode an electrical breakdown can be stimulated by an increase of the electrical conductance in a channel by an electrical pulse and stored charge leads to the sample destruction. Both of these breakdowns have got a stochastic behaviour and could be hardly localized in advance. -

ECE 255, Diodes and Rectifiers

ECE 255, Diodes and Rectifiers 23 January 2018 In this lecture, we will discuss the use of Zener diode as voltage regulators, diode as rectifiers, and as clamping circuits. 1 Zener Diodes In the reverse biased operation, a Zener diode displays a voltage breakdown where the current rapidly increases within a small range of voltage change. This property can be used to limit the voltage within a small range for a large range of current. The symbol for a Zener diode is shown in Figure 1. Figure 1: The symbol for a Zener diode under reverse biased (Courtesy of Sedra and Smith). Figure 2 shows the i-v relation of a Zener diode near its operating point where the diode is in the breakdown regime. The beginning of the breakdown point is labeled by the current IZK also called the knee current. The oper- ating point can be approximated by an incremental resistance, or dynamic resistance described by the reciprocal of the slope of the point. Since the slope, dI proportional to dV , is large, the incremental resistance is small, generally on the order of a few ohms to a few tens of ohms. The spec sheet usually gives the voltage of the diode at a specified test current IZT . Printed on March 14, 2018 at 10 : 29: W.C. Chew and S.K. Gupta. 1 Figure 2: The i-v characteristic of a Zener diode at its operating point Q (Cour- tesy of Sedra and Smith). The diode can be fabricated to have breakdown voltage of a few volts to a few hundred volts. -

Transistor Basics

Transistor Basics: Collector The schematic representation of a transistor is shown to the left. Note the arrow pointing down towards the emitter. This signifies it's an NPN transistor (current flows in the direction of the arrow). See the Q1 datasheet at: www.fairchildsemi.com. Base 2N3904 A transistor is basically a current amplifier. Say we let 1mA flow into the base. We may get 100mA flowing into the collector. Note: The Emitter currents flowing into the base and collector exit through the emitter (the sum off all currents entering or leaving a node must equal zero). The gain of the transistor will be listed in the datasheet as either βDC or Hfe. The gain won't be identical even in transistors with the same part number. The gain also varies with the collector current and temperature. Because of this we will add a safety margin to all our base current calculations (i.e. if we think we need 2mA to turn on the switch we'll use 4mA just to make sure). Sample circuit and calculations (NPN transistor): Let's say we want to heat a block of metal. One way to do that is to connect a power resistor to the block and run current through the resistor. The resistor heats up and transfers some of the heat to the block of metal. We will use a transistor as a switch to control when the resistor is heating up and when it's cooling off (i.e. no current flowing in the resistor). In the circuit below R1 is the power resistor that is connected to the object to be heated. -

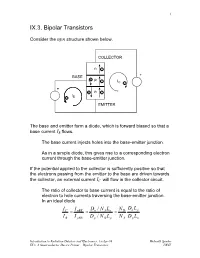

IX.3. a Semiconductor Device Primer – Bipolar Transistors LBNL 2

1 IX.3. Bipolar Transistors Consider the npn structure shown below. COLLECTOR n- BASE + +p -IC- + +n- I -B EMITTER The base and emitter form a diode, which is forward biased so that a base current IB flows. The base current injects holes into the base-emitter junction. As in a simple diode, this gives rise to a corresponding electron current through the base-emitter junction. If the potential applied to the collector is sufficiently positive so that the electrons passing from the emitter to the base are driven towards the collector, an external current IC will flow in the collector circuit. The ratio of collector to base current is equal to the ratio of electron to hole currents traversing the base-emitter junction. In an ideal diode IC I nBE Dn / N ALn N D Dn Lp = = = I B I pBE Dp / N D Lp N A Dp Ln Introduction to Radiation Detctors and Electronics, 13-Apr-99 Helmuth Spieler IX.3. A Semiconductor Device Primer – Bipolar Transistors LBNL 2 If the ratio of doping concentrations in the emitter and base regions ND /NA is sufficiently large, the collector current will be greater than the base current. ⇒ DC current gain Furthermore, we expect the collector current to saturate when the collector voltage becomes large enough to capture all of the minority carrier electrons injected into the base. Since the current inside the transistor comprises both electrons and holes, the device is called a bipolar transistor. Dimensions and doping levels of a modern high-frequency transistor (5 – 10 GHz bandwidth) 0 0.5 1.0 1.5 Distance [µm] (adapted from Sze) Introduction to Radiation Detctors and Electronics, 13-Apr-99 Helmuth Spieler IX.3. -

Laboratory Exercise 2 DC Characteristics of Bipolar Junction

DEPARTMENT OF SEMICONDUCTOR AND OPTOELECTRONIC DEVICES Semiconductor Device Laboratory Laboratory Exercise 2 DC characteristics of Bipolar Junction Transistors (BJT) The aim of the exercise The main aim of this laboratory exercise is to understand principles of operation of Bipolar Junction Transistors (BJT). It covers the measurements of static and small signal parameters. Backgrounds Physical structure of the BJT BJT is a semiconductor device having a three-layer structure with three external electrodes, the emitter (E), the base (B), and the collector (C). As shown in Fig. 1, the structure may be p-n-p or n-p-n type. Despite of the transistor type the emitter layer has always more acceptor or donor impurities added than the base or the collector layer. This asymmetry results from different roles the emitter and the collector layers play in the BJT. In normal operation of the BJT (as an amplifier), the base-emitter junction is forward biased and the base-collector junction is reverse biased. Transistor amplification is controlled by changing the current flow through the base-emitter junction. C N C . C P C . P B. N B. B . B . E . N . E P . E E (a) (b) Fig. 1. The n-p-n BJT (a) and the p-n-p BJT (b) along with their symbols There are three operating configurations of the BJT. These are the common-emitter (OE) configuration, the common-base configuration (OB), and the common-collector (OC) configuration. These configurations are shown in Fig. 2. (a) (b) (c) Fig. 2 The n-p-n transistor operating configurations: (a) common-emitter, (b) common-base, (c) common-collector DC characteristics Four types of characteristics can be defined for each of the transistor operating configurations.