Aperture Information This Is a Text File Describing the Size and Shape of Eachelement on the Board. Also Known As a D:Codelist

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Date Created Size MB . تماس بگیر ید 09353344788

Name Software ( Search List Ctrl+F ) Date created Size MB برای سفارش هر یک از نرم افزارها با شماره 09123125449 - 09353344788 تماس بگ ریید . \1\ Simulia Abaqus 6.6.3 2013-06-10 435.07 Files: 1 Size: 456,200,192 Bytes (435.07 MB) \2\ Simulia Abaqus 6.7 EF 2013-06-10 1451.76 Files: 1 Size: 1,522,278,400 Bytes (1451.76 MB) \3\ Simulia Abaqus 6.7.1 2013-06-10 584.92 Files: 1 Size: 613,330,944 Bytes (584.92 MB) \4\ Simulia Abaqus 6.8.1 2013-06-10 3732.38 Files: 1 Size: 3,913,689,088 Bytes (3732.38 MB) \5\ Simulia Abaqus 6.9 EF1 2017-09-28 3411.59 Files: 1 Size: 3,577,307,136 Bytes (3411.59 MB) \6\ Simulia Abaqus 6.9 2013-06-10 2462.25 Simulia Abaqus Doc 6.9 2013-06-10 1853.34 Files: 2 Size: 4,525,230,080 Bytes (4315.60 MB) \7\ Simulia Abaqus 6.9.3 DVD 1 2013-06-11 2463.45 Simulia Abaqus 6.9.3 DVD 2 2013-06-11 1852.51 Files: 2 Size: 4,525,611,008 Bytes (4315.96 MB) \8\ Simulia Abaqus 6.10.1 With Documation 2017-09-28 3310.64 Files: 1 Size: 3,471,454,208 Bytes (3310.64 MB) \9\ Simulia Abaqus 6.10.1.5 2013-06-13 2197.95 Files: 1 Size: 2,304,712,704 Bytes (2197.95 MB) \10\ Simulia Abaqus 6.11 32BIT 2013-06-18 1162.57 Files: 1 Size: 1,219,045,376 Bytes (1162.57 MB) \11\ Simulia Abaqus 6.11 For CATIA V5-6R2012 2013-06-09 759.02 Files: 1 Size: 795,893,760 Bytes (759.02 MB) \12\ Simulia Abaqus 6.11.1 PR3 32-64BIT 2013-06-10 3514.38 Files: 1 Size: 3,685,099,520 Bytes (3514.38 MB) \13\ Simulia Abaqus 6.11.3 2013-06-09 3529.41 Files: 1 Size: 3,700,856,832 Bytes (3529.41 MB) \14\ Simulia Abaqus 6.12.1 2013-06-10 3166.30 Files: 1 Size: 3,320,102,912 Bytes -

Information Required for Quotation

INFORMATION REQUIRED FOR QUOTATION GENERAL INFORMATION Date of Request: Quote Due Date: Requested By: Company: Address: Telephone: FAX: e-mail: Contacts: Purchasing: Telephone: e-mail: Technical: Telephone: e-mail: Quotation Type: Assembly: Consignment Partial Turnkey Turnkey Test Type: Flying Prober Gen-Rad Functional Thermal Testing X-Ray Box Build: Consignment Partial Turnkey Turnkey Quality Requirement (IPC-A-610 Class II is default standard): Quotation Quantities: Turn-time Desired: PRODUCT INFORMATION Electronic Data Preferred – See Attachments A and B All Quotes BOM w/part numbers, descriptions, quantities, reference designators, part types (SMT, Through-hole) Assembly Drawing Circuit Board Drawing (including panelization, when applicable) Special instructions Additional Information for Partial Turnkey/Turnkey Quotes AVL w/approved manufacturers, manufacturer’s part numbers, preferred sources Additional Information for All Test Quotes CAD database Schematics Circuit Board (sample assembled board preferred) Additional Information for Functional Test Quotes Test procedure (with time required) Specifications and space required for test equipment to be provided Specifications for test equipment to be purchased Additional Information for Box Build Quotes Mechanical drawings of fabricated parts INFORMATION REQUIRED FOR MANUFACTURING Contacts Documentation: Telephone: e-mail: Engineering: Telephone: e-mail: Purchasing: Telephone: e-mail: Quality: Telephone: e-mail: Assembly 1. BOM w/part numbers, descriptions, quantities, reference designators 2. AVL w/approved manufacturers, manufacturer’s part numbers, preferred sources (Turnkey parts only) 3. Spares (unpopulated locations) List 4. Assembly Drawings w/pin 1 indicated for polarized parts (5 sets, if electronic data not provided) 5. Circuit Board Drawing 6. Special Instructions and visual aids (pictures, etc) 7. Solder sample (rejected bare circuit board) 8. -

Release Notes: Desktop Edition

Release Notes: Desktop Edition AutoVue 19.2c2: November 30, 2007 Installation • Please make sure you have AutoVue 19.2c1 installed before upgrading to AutoVue 19.2c2. Note: If you have an older version of AutoVue installed (e.g. AutoVue 19.2), please uninstall it before installing AutoVue 19.2c1 and upgrading to AutoVue 19.2c2. MCAD Formats • Added font substitution for missing native fonts: • CATIA 4 and CATIA 5 • Pro/ENGINEER • Unigraphics • Added support for Unigraphics NX5. • Performed bugs fixes for Unigraphics and CATIA 5. EDA Formats • Added font substitution for missing native fonts: • Altium Protel • OrCAD Layout • Cadence Allegro Layout • Cadence Allegro IPF • Cadence Allegro Extract • Mentor Board Station • Mentor PADS • Zuken CADSTAR • P-CAD • PDIF AEC Formats • Added font substitution for missing native fonts: • AutoCAD • MicroStation 7 and MicroStation 8 • Performed bug fixes for AutoCAD. Release Notes - AutoVue Desktop Edition - 1 - November 30, 2007 AutoVue 19.2c1: September 30, 2007 Packaging and Licensing • Introduced separate installers for the following product packages: • AutoVue Office • AutoVue 2D, AutoVue 2D Professional • AutoVue 3D Professional-SME, AutoVue 3D Advanced, AutoVue 3D Professional Advanced • AutoVue EDA Professional • AutoVue Electro-Mechanical Professional • AutoVue DEMO • Customers are no longer required to enter license keys to install and run the product. • To install 19.2c1, users are required to first uninstall 19.2. MCAD Formats • General bug fixes for CATIA 5 EDA Formats • Performed maintenance and bug fixes for Allegro files. General • Enabled interface for customized resource resolution DLL to give integrators more flexibility on how to locate external resources. Sample source code and DLL is located in the integrat\VisualC\reslocate directory. -

Installation and Administration Manual Oracle Autovue 20.0.0, Desktop Version Copyright © 1989, 2010, Oracle And/Or Its Affiliates

Installation and Administration Manual Oracle AutoVue 20.0.0, Desktop Version Copyright © 1989, 2010, Oracle and/or its affiliates. All rights reserved. Portions of this software Copyright 1996-2007 Glyph & Cog, LLC. Portions of this software Copyright Unisearch Ltd, Australia. Portions of this software are owned by Siemens PLM © 1986-2008. All rights reserved. This software uses ACIS® software by Spatial Technology Inc. ACIS® Copyright © 1994-1999 Spatial Technology Inc. All rights reserved. Oracle is a registered trademark of Oracle Corporation and/or its affiliates. Other names may be trademarks of their respective owners. This software and related documentation are provided under a license agreement containing restrictions on use and disclosure and are protected by intellectual property laws. Except as expressly permitted in your license agreement or allowed by law, you may not use, copy, reproduce, translate, broadcast, modify, license, transmit, distribute, exhibit, perform, publish or display any part, in any form, or by any means. Reverse engineering, disassembly, or decompilation of this software, unless required by law for interoperability, is prohibited. The information contained herein is subject to change without notice and is not warranted to be error-free. If you find any errors, please report them to us in writing. If this software or related documentation is delivered to the U.S. Government or anyone licensing it on behalf of the U.S. Govern- ment, the following notice is applicable: U.S. GOVERNMENT RIGHTS Programs, software, databases, and related documentation and technical data delivered to U.S. Government customers are "com- mercial computer software" or "commercial technical data" pursuant to the applicable Federal Acquisition Regulation and agency- specific supplemental regulations. -

Release Notes: Web Edition

Release Notes: Web Edition AutoVue 19.2c2: November 30, 2007 Installation • Please make sure you have AutoVue 19.2c1 installed before upgrading to AutoVue 19.2c2. Note: If you have an older version of AutoVue installed (e.g. AutoVue 19.2), please uninstall it before installing AutoVue 19.2c1 and upgrading to AutoVue 19.2c2. MCAD Formats • Added font substitution for missing native fonts: • CATIA 4 and CATIA 5 • Pro/ENGINEER • Unigraphics • Added support for Unigraphics NX5. • Performed bugs fixes for Unigraphics and CATIA 5. EDA Formats • Added font substitution for missing native fonts: • Altium Protel • OrCAD Layout • Cadence Allegro Layout • Cadence Allegro IPF • Cadence Allegro Extract • Mentor Board Station • Mentor PADS • Zuken CADSTAR • P-CAD • PDIF AEC Formats • Added font substitution for missing native fonts: • AutoCAD • MicroStation 7 and MicroStation 8 • Performed bug fixes for AutoCAD. Release Notes - AutoVue Web Edition - 1 - November 30, 2007 AutoVue 19.2c1: September 30, 2007 Packaging and Licensing • Introduced separate installers for the following product packages: • AutoVue Office • AutoVue 2D, AutoVue 2D Professional • AutoVue 3D Professional-SME, AutoVue3D Advanced, AutoVue 3D Professional Advanced • AutoVue EDA Professional • AutoVue Electro-Mechanical Professional • Customers are no longer required to enter license keys to install and run AutoVue Web Edition and AutoVue VueLinks. • To install 19.2c1, users are required to first uninstall 19.2. MCAD Formats • General bug fixes for CATIA 5 EDA Formats • Performed maintenance and bug fixes for Allegro files. AEC Formats • General bug fixes of metafiles for AutoCAD files. General • Added a checkbox, Resolve Local Resources, under the General section in the Options > Configuration dialog to enable/disable resource resolution on client side. -

Printed Circuit Board

Jurnal Teknik Elektro Vol. 10 No. 1 P-ISSN 1411 - 0059 Januari - Juni 2018 E-ISSN 2549 - 1571 Analisis Karakteristik Elektrik Bentuk Geometri Jalur Printed Circuit Board Menggunakan Pendekatan Finite Element Putut Son Maria1 dan Elva Susianti2 1Jurusan Teknik Elektro, Fakultas Sains dan Teknologi, Universitas Islam Negeri Sultan Syarif Kasim Riau 2Jurusan Teknik Elektronika, Politeknik Caltex Riau [email protected], [email protected] Abstract— Some Electronics Computer Aided Design (ECAD) softwares have provided several track shapes to design a Printed Circuit Board (PCB), such as right angle, rounded and trapezoidal. However, it is quite difficult to find scientific literature that can be used as a guide which explains and compiles directly about each character of the geometry. This study aims to analyze and to observe the electrical characteristics of the geometry shape on the Printed Circuit Board (PCB) path by using the finite element method. Each PCB path shape is modeled according to its geometry and physical properties, then calculated for its electrical quantity and be observed for its performance at given current. Simulation and numerical calculations showed that the shape of trapezoidal and rounded geometry have lower resistance and planar inductance of 6.8% and 7.39% respectively than the right angle shape. Keywords— ECAD, PCB, geometric shape, Finite Element Analysis Abstrak— Beberapa perangkat lunak yang termasuk kategori Electronics Computer Aided Design (ECAD) telah menyediakan beberapa pilihan bentuk jalur Printed Circuit Board (PCB) seperti right angle, rounded dan trapezoidal. Tidak banyak ditemukan literatur ilmiah yang dapat dijadikan pedoman yang menjelaskan dan mengkomparasikan secara langsung tentang masing-masing karakter dari bentuk geometri tersebut. -

Altium Limited ASX Announcement

`Altium Limited ASX Announcement Date: 15 June 2021 ALTIUM LIMITED ACN 009 568 772 Level 6, Tower B Announcement authorised by: The Zenith Samuel Weiss 821 Pacific Highway Chatswood NSW 2067 Chairman Australia Altium Limited Investor Relations Contact Details: Kim Besharati Chief of Staff (US based) Phone: +1 858 864 1513 Mobile: +1 760 828 3567 Altium to Host Investor Call to Present its Vision for Industry Transformation and Strategy for Value Creation Sydney, Australia - 15 June 2021 - Electronics design software company Altium Limited (ASX:ALU) will host an investor call at 9.30am AEST on Friday 18th June to share details of the Company vision and strategy to unify and to transform the electronics industry. Altium CEO Aram Mirkazemi, Chairman Sam Weiss and CFO Martin Ive will host the investor call and demonstrate why Altium is uniquely positioned within the global electronics manufacturing industry and how its cloud platform Altium 365 and industry partners platform Nexar connect the electronics value chain from beginning to end. Altium management will reiterate their commitment to achieving Altium’s aspirational 2025 financial goals of US$500 million and 100,000 subscribers and demonstrate why the Altium Board of Directors recently rejected an unsolicited acquisition offer by Autodesk Inc. Investor Call Details Date: Altium Investor Call, Friday 18 June 9.30am AEST Host: CEO Aram Mirkazemi, Chairman Sam Weiss and CFO Martin Ive Participants can pre-register for the investor call using the following link to receive dial in details: https://apac.directeventreg.com/registration/event/7187104 Contact Details: Kim Besharati - Chief of Staff (US based) Samuel Weiss - Chairman Mobile: +1 760 828 3567 Mobile: +61 404 892 221 ENDS Page 1 of 2 About Altium Altium (ASX:ALU) is a multinational software corporation headquartered in San Diego, California, that focuses on electronics design systems for 3D PCB design and embedded system development. -

Altium Limited ASX Announcement

`Altium Limited ASX Announcement 14 July 2020 ALTIUM LIMITED ACN 009 568 772 Level 6, Tower B Announcement authorised by: The Zenith Samuel Weiss 821 Pacific Highway Chatswood NSW 2067 Chairman Australia Altium Limited Investor Relations Contact Details: Kim Besharati VP Investor Relations & Corporate Affairs Phone: +1 858 864 1513 Mobile: +1 760 828 3567 Unaudited Sales and Revenue for the Full Year Ending 30 June 2020 Altium Achieves 10% Revenue Growth and Exceeds 50,000 Subscriber Target Sydney, Australia - 14 July 2020 - Electronic design software company Altium Limited (ASX:ALU) updates the market on its unaudited sales and revenue for the full year ended 30 June 2020. Altium achieved revenue growth of 10% to US $189 million with solid performances delivered in core business units and key regions during the challenging COVID-19 environment. Altium delivered record growth in new Altium Designer seats and subscriptions to exceed its 50,000 subscriber target. Other highlights include: ● Strong increase of 14% in new Altium Designer seats sold. ● Record growth of 17% in the subscription base to well over 50,000 subscribers. ● Cash balance of over US $90 million. Unaudited Sales and Revenue Performance for the Year Ended 30 June 2020 FY20 FY19 Change (US$ million) (US$ million) % Worldwide Revenue 189 172 10% Worldwide Sales 194 177 10% Comments from Altium’s CEO Mr Aram Mirkazemi: Altium CEO, Mr Aram Mirkazemi commented: “Altium’s strategy of providing attractive pricing and extended payment terms to support our customers during COVID-19 and to drive volume to support our pursuit of market dominance has been rewarded. -

COMPARISON REPORT ALTIUM DESIGNER 13 Vs

COMPARISON REPORT ALTIUM DESIGNER 13 vs. ALTIUM DESIGNER 16 The world is changing, and electronics are leading the charge towards the future. At the core of our evolutionary pursuit for progress are engineers and companies like yours driving humanity forward. But do you have the design technology needed to deliver the connected, intelligent and autonomous devices of the future? Invest in your future with Altium Subscription. Invest in Invest in Invest in Your Skills Your Company’s Success Your Tools Maintain your competitive edge Deliver the best products to market first Equip yourself to design the with access to the newest design at the lowest possible cost and continue to technologies of the future with the latest methodologies and resources. drive your industry forward. EDA innovations in Altium Designer. VERSION FEATURE COMPARISON Altium Altium Feature Name What it Does How It Benefits You Designer 13 Designer 16 Enhance the readability of components Customize pin names, designator Customizable Schematic Pins placed on your design with customizable in positions, font properties, and colors. properties. Have complete control over your compo- Select alternative part choices for nent selection process and include pin Alternative Part Choice System - obsolete or unavailable components. compatible backup part choices directly in your BOM. Automatically detect and setup con- Design accurate high-speed board layouts Technology-Aware xSignals Wizard straints for common with automatic configuration for DDR3/4 - high-speed technologies. and USB 3.0 class and match length rules. Precisely measure your board layout in Measure all board objects while Precise 3D Measurements Native 3D PCB™ and clearly communicate - in 3D view. -

Installation and Administration Manual Copyright © 1989, 2008, Oracle And/Or Its Affiliates

AutoVue Desktop Version 19.3.1 Installation and Administration Manual Copyright © 1989, 2008, Oracle and/or its affiliates. All rights reserved. Portions of this software Copyright 1996-2007 Glyph & Cog, LLC. Portions of this software Copyright Unisearch Ltd, Australia. Portions of this software are owned by Siemens PLM © 1986-2008. All rights reserved. This software uses ACIS® software by Spatial Technology Inc. ACIS® Copyright © 1994-1999 Spatial Technology Inc. All rights reserved. Oracle is a registered trademark of Oracle Corporation and/or its affiliates. Other names may be trademarks of their respective owners. This software and related documentation are provided under a license agreement containing restrictions on use and disclosure and are protected by intellectual property laws. Except as expressly permitted in your license agreement or allowed by law, you may not use, copy, reproduce, translate, broadcast, modify, license, transmit, distribute, exhibit, perform, publish or display any part, in any form, or by any means. Reverse engineering, disassembly, or decompilation of this software, unless required by law for interoperability, is prohibited. The information contained herein is subject to change without notice and is not warranted to be error-free. If you find any errors, please report them to us in writing. If this software or related documentation is delivered to the U.S. Government or anyone licensing it on behalf of the U.S. Govern- ment, the following notice is applicable: U.S. GOVERNMENT RIGHTS Programs, software, databases, and related documentation and technical data delivered to U.S. Government customers are "com- mercial computer software" or "commercial technical data" pursuant to the applicable Federal Acquisition Regulation and agency- specific supplemental regulations. -

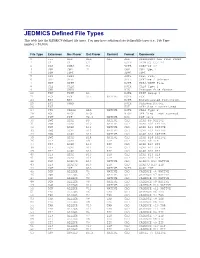

JEDMICS Defined File Types This Table Lists the JEDMICS Defined File Types

JEDMICS Defined File Types This table lists the JEDMICS defined file types. You may have additional site defined file types (i.e., File Type number > 50,000). File Type Extension Src Flavor Dst Flavor Content Format Comments 0 --- ALL ALL ALL ALL REPRESENT ALL FILE TYPES 1 C4 C4 C4 RSTR JEDMICS CCITT4 2 IGS IGES V3 VCTR IGES-2D v3 3 CGM CGM T1 CGM CGM Type 1 4 SGM SGML SGML SGML 5 TXT TEXT ASCI Text File 6 OFF OFFL OFFL Offline / Unknown 7 NIF NIFF RSTR NIRS/NIFF File 8 CAL CALS RSTR CALS Type 1 9 UNK UNKN BIN Unknown file format 20 TIF TIFF G6 RSTR TIFF Group 6 21 PCX PCX ALL NATIVE RSTR PCX 23 EPS EPS RSTR Encapsulated Postscript 25 RST UNKN RSTR Unknown Raster 26 EXT EXT Off-line - restricted 27 CT2 CALS2 ALL NATIVE RSTR CALS Type 2 28 NOF NIOF NIOF NIOF Off-line - not scanned 29 PDF PDF V2.1 NATIVE DOC PDF v2.1 30 DWG ACAD R9 NATIVE CAD ACAD R9 NATIVE 31 DWG ACAD R10 NATIVE CAD ACAD R10 NATIVE 32 DWG ACAD R11 NATIVE CAD ACAD R11 NATIVE 33 DWG ACAD R12 NATIVE CAD ACAD R12 NATIVE 34 DWG ACAD R13 NATIVE CAD ACAD R13 NATIVE 35 DWG ACAD R14 NATIVE CAD ACAD R14 NATIVE 36 ZIP ACAD R9 ZIP CAD ACAD R9 ZIP 37 ZIP ACAD R10 ZIP CAD ACAD R10 ZIP 38 ZIP ACAD R11 ZIP CAD ACAD R11 ZIP 39 ZIP ACAD R12 ZIP CAD ACAD R12 ZIP 40 ZIP ACAD R13 ZIP CAD ACAD R13 ZIP 41 DWG ACAD R14 ZIP CAD ACAD R14 ZIP 42 DWG ACAD3D R13 NATIVE CAD ACAD3D R13 NATIVE 43 ZIP ACAD3D R13 ZIP CAD ACAD3D R13 ZIP 44 DXF DXF ALL NATIVE VCTR ACAD DXF 45 DGN ALLEGR V6 NATIVE CAD CADENCE v6 NATIVE 46 DGN ALLEGR V7 NATIVE CAD CADENCE v7 NATIVE 47 DGN ALLEGR V8 NATIVE CAD CADENCE v8 NATIVE -

Orcad Layout® User's Guide

OrCAD Layout® User’s Guide Product Version 10.0 June 2003 1985-2003 Cadence Design Systems, Inc. All rights reserved. Printed in the United States of America. Cadence Design Systems, Inc., 555 River Oaks Parkway, San Jose, CA 95134, USA Trademarks: Trademarks and service marks of Cadence Design Systems, Inc. (Cadence) contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence’s trademarks, contact the corporate legal department at the address shown above or call 1-800-862-4522. All other trademarks are the property of their respective holders. Restricted Print Permission: This publication is protected by copyright and any unauthorized use of this publication may violate copyright, trademark, and other laws. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. This statement grants you permission to print one (1) hard copy of this publication subject to the following conditions: 1 The publication may be used solely for personal, informational, and noncommercial purposes; 2 The publication may not be modified in any way; 3 Any copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement; and 4 Cadence reserves the right to revoke this authorization at any time, and any such use shall be discontinued immediately upon written notice from Cadence. Disclaimer: Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence.