Mosfet Enhence Deplition

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Electronics Ii Curriculum Guide January 2012

PASSAIC COUNTY TECHNICAL INSTITUTE ELECTRONICS II CURRICULUM GUIDE JANUARY 2012 I. Course Description – Electronics Technology II Electronics II is designed to provide the student with enhanced skills and understanding of the electronics industry and changing career opportunities. Course goals are to provide the student with an augmented comprehension of advanced digital circuits and applications based on sound electrical fundamentals. Lab applications and projects are combined with theory based learning to provide the learner with a program which emulates industry standards and practices. II. Course Outline and Objectives UNIT 1: ELECTRONICS SHOP SAFETY (5.1.12.C.1, 5.1.4.D.3, 5.1.P.B.3) Students will: 1. develop a clear understanding of things that conduct electricity 2. understand lab and electrical hazards 3. know the dangers of electricity and how it affects the human body 4. learn how to report lab hazards to school personnel 5. develop a positive attitude about safe environments 6. learn proper use of tools in a safe manner 7. operate test equipment safely and effectively 8. avoid and report obstructions in the lab which can lead to injury 9. identify elements in the lab which can potentially cause injury 10. create and document a personal safety plan 11. know where to access safety standards posted in the lab 12. learn to ask appropriate questions when concerned about safety 13. operate and maintain all lab computers and peripherals efficiently 14. wear hand and eye protection as instructed 15. pass the program safety test with a 100% score UNIT 2: WORK ENVIRONMNETS IN ELECTRONICS (9.2.8.A.1, 9.4.12.O. -

Design & Performance Analysis of DG-MOSFET for Reduction of Short

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by Directory of Open Access Journals Ankita Wagadre Int. Journal of Engineering Research and Applications www.ijera.com ISSN : 2248-9622, Vol. 4, Issue 7( Version 1), July 2014, pp.30-34 RESEARCH ARTICLE OPEN ACCESS Design & Performance Analysis of DG-MOSFET for Reduction of Short Channel Effect over Bulk MOSFET at 20nm Ankita Wagadre*, Shashank Mane** *(Research scholar, Department of Electronics & Communication, SBITM, Betul-460001) ** (Assistant Professor, Department of Electronics & Communication, SBITM, Betul-460001) ABSTRACT An aggressive scaling of conventional MOSFETs channel length reduces below 100nm and gate oxide thickness below 3nm to improved performance and packaging density. Due to this scaling short channel effect (SCEs) like threshold voltage, Subthreshold slope, ON current and OFF current plays a major role in determining the performance of scaled devices. The double gate (DG) MOSFETS are electro-statically superior to a single gate (SG) MOSFET and allows for additional gate length scaling. Simulation work on both devices has been carried out and presented in paper. The comparative study had been carried out for threshold voltage (VT), Subthreshold slope (Sub VT), ION and IOFF Current. It is observed that DG MOSFET provide good control on leakage current over conventional Bulk (Single Gate) MOSFET. The VT (Threshold Voltage) is 2.7 times greater than & ION of DG MOSFET is 2.2 times smaller than the conventional Bulk (Single Gate) MOSFET. Keywords - DG MOSFET (Double Gate Metal oxide Field Effect Transistor), Short Channel Effect (SCE), Bulk (Single Gate) MOSFET. -

An Integrated Semiconductor Device Enabling Non-Optical Genome Sequencing

ARTICLE doi:10.1038/nature10242 An integrated semiconductor device enabling non-optical genome sequencing Jonathan M. Rothberg1, Wolfgang Hinz1, Todd M. Rearick1, Jonathan Schultz1, William Mileski1, Mel Davey1, John H. Leamon1, Kim Johnson1, Mark J. Milgrew1, Matthew Edwards1, Jeremy Hoon1, Jan F. Simons1, David Marran1, Jason W. Myers1, John F. Davidson1, Annika Branting1, John R. Nobile1, Bernard P. Puc1, David Light1, Travis A. Clark1, Martin Huber1, Jeffrey T. Branciforte1, Isaac B. Stoner1, Simon E. Cawley1, Michael Lyons1, Yutao Fu1, Nils Homer1, Marina Sedova1, Xin Miao1, Brian Reed1, Jeffrey Sabina1, Erika Feierstein1, Michelle Schorn1, Mohammad Alanjary1, Eileen Dimalanta1, Devin Dressman1, Rachel Kasinskas1, Tanya Sokolsky1, Jacqueline A. Fidanza1, Eugeni Namsaraev1, Kevin J. McKernan1, Alan Williams1, G. Thomas Roth1 & James Bustillo1 The seminal importance of DNA sequencing to the life sciences, biotechnology and medicine has driven the search for more scalable and lower-cost solutions. Here we describe a DNA sequencing technology in which scalable, low-cost semiconductor manufacturing techniques are used to make an integrated circuit able to directly perform non-optical DNA sequencing of genomes. Sequence data are obtained by directly sensing the ions produced by template-directed DNA polymerase synthesis using all-natural nucleotides on this massively parallel semiconductor-sensing device or ion chip. The ion chip contains ion-sensitive, field-effect transistor-based sensors in perfect register with 1.2 million wells, which provide confinement and allow parallel, simultaneous detection of independent sequencing reactions. Use of the most widely used technology for constructing integrated circuits, the complementary metal-oxide semiconductor (CMOS) process, allows for low-cost, large-scale production and scaling of the device to higher densities and larger array sizes. -

Vlsi Design Lecture Notes B.Tech (Iv Year – I Sem) (2018-19)

VLSI DESIGN LECTURE NOTES B.TECH (IV YEAR – I SEM) (2018-19) Prepared by Dr. V.M. Senthilkumar, Professor/ECE & Ms.M.Anusha, AP/ECE Department of Electronics and Communication Engineering MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) Recognized under 2(f) and 12 (B) of UGC ACT 1956 (Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – ‘A’ Grade - ISO 9001:2015 Certified) Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India Unit -1 IC Technologies, MOS & Bi CMOS Circuits Unit -1 IC Technologies, MOS & Bi CMOS Circuits UNIT-I IC Technologies Introduction Basic Electrical Properties of MOS and BiCMOS Circuits MOS I - V relationships DS DS PMOS MOS transistor Threshold Voltage - VT figure of NMOS merit-ω0 Transconductance-g , g ; CMOS m ds Pass transistor & NMOS Inverter, Various BiCMOS pull ups, CMOS Inverter Technologies analysis and design Bi-CMOS Inverters Unit -1 IC Technologies, MOS & Bi CMOS Circuits INTRODUCTION TO IC TECHNOLOGY The development of electronics endless with invention of vaccum tubes and associated electronic circuits. This activity termed as vaccum tube electronics, afterward the evolution of solid state devices and consequent development of integrated circuits are responsible for the present status of communication, computing and instrumentation. • The first vaccum tube diode was invented by john ambrase Fleming in 1904. • The vaccum triode was invented by lee de forest in 1906. Early developments of the Integrated Circuit (IC) go back to 1949. German engineer Werner Jacobi filed a patent for an IC like semiconductor amplifying device showing five transistors on a common substrate in a 2-stage amplifier arrangement. -

Digital Electronics Syllabus

Digital Electronics Mrs. Carlson – D102 Pathway to Engineering Project Lead the Way CTE Academy Sioux Falls, SD [email protected] DE Course Description Digital electronics is the foundation of all modern electronic devices such as cellular phones, MP3 players, laptop computers, digital cameras, and high-definition televisions. The major focus of Digital Electronics is to expose students to the design process of combinational and sequential logic design, key elements of careers in engineering. Students design circuits to solve problems, export their designs to a printed circuit auto-routing program that generates printed circuit boards, and use appropriate components to build their designs. DE Expectations Project Lead the Way’s Pathway to Engineering program is a pre-professional program. Participants in this program will be held to the highest academic and behavior standards. Academic expectations include: Preparing for class and having all required materials on hand: pen/pencil, calculator, engineering notebook, 3-ring binder Completing activities and meeting project deadlines Working cooperatively with others Submitting ALL assignments on or before the assigned due date Using the PLTW Learning Management System to review course materials, receive messages and keep track of due dates Behavior expectations include: Being punctual for all class meeting times Maintaining a clean and SAFE working environment Speaking respectfully to others Using all equipment SAFELY and for its intended purpose only Late work policy: -

Chapter 1 Computers and Digital Basics Computer Concepts 2014 1 Your Assignment…

Chapter 1 Computers and Digital Basics Computer Concepts 2014 1 Your assignment… Prepare an answer for your assigned question. Use Chapter 1 in the book and this PowerPoint to procure information. Prepare a PowerPoint presentation to: 1. Show your answer and additional information/facts – make sure you understand and can explain your answer. Provide as must information and detail as possible. Add graphics to enhance. 2. Where in the book did you find your information? Include the page number. 3. What more do you need to find out to help you better understand this question? Be prepared to share your information with the class. Chapter 1: Computers and Digital Basics 2 1 The Digital Revolution The digital revolution is an ongoing process of social, political, and economic change brought about by digital technology, such as computers and the Internet The technology driving the digital revolution is based on digital electronics and the idea that electrical signals can represent data, such as numbers, words, pictures, and music Chapter 1: Computers and Digital Basics 6 1 The Digital Revolution Digitization is the process of converting text, numbers, sound, photos, and video into data that can be processed by digital devices The digital revolution has evolved through four phases, beginning with big, expensive, standalone computers, and progressing to today’s digital world in which small, inexpensive digital devices are everywhere Chapter 1: Computers and Digital Basics 7 1 The Digital Revolution Chapter 1: Computers and Digital Basics -

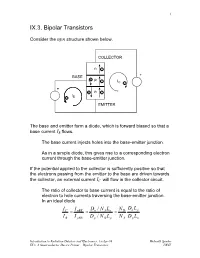

IX.3. a Semiconductor Device Primer – Bipolar Transistors LBNL 2

1 IX.3. Bipolar Transistors Consider the npn structure shown below. COLLECTOR n- BASE + +p -IC- + +n- I -B EMITTER The base and emitter form a diode, which is forward biased so that a base current IB flows. The base current injects holes into the base-emitter junction. As in a simple diode, this gives rise to a corresponding electron current through the base-emitter junction. If the potential applied to the collector is sufficiently positive so that the electrons passing from the emitter to the base are driven towards the collector, an external current IC will flow in the collector circuit. The ratio of collector to base current is equal to the ratio of electron to hole currents traversing the base-emitter junction. In an ideal diode IC I nBE Dn / N ALn N D Dn Lp = = = I B I pBE Dp / N D Lp N A Dp Ln Introduction to Radiation Detctors and Electronics, 13-Apr-99 Helmuth Spieler IX.3. A Semiconductor Device Primer – Bipolar Transistors LBNL 2 If the ratio of doping concentrations in the emitter and base regions ND /NA is sufficiently large, the collector current will be greater than the base current. ⇒ DC current gain Furthermore, we expect the collector current to saturate when the collector voltage becomes large enough to capture all of the minority carrier electrons injected into the base. Since the current inside the transistor comprises both electrons and holes, the device is called a bipolar transistor. Dimensions and doping levels of a modern high-frequency transistor (5 – 10 GHz bandwidth) 0 0.5 1.0 1.5 Distance [µm] (adapted from Sze) Introduction to Radiation Detctors and Electronics, 13-Apr-99 Helmuth Spieler IX.3. -

Laboratory Exercise 2 DC Characteristics of Bipolar Junction

DEPARTMENT OF SEMICONDUCTOR AND OPTOELECTRONIC DEVICES Semiconductor Device Laboratory Laboratory Exercise 2 DC characteristics of Bipolar Junction Transistors (BJT) The aim of the exercise The main aim of this laboratory exercise is to understand principles of operation of Bipolar Junction Transistors (BJT). It covers the measurements of static and small signal parameters. Backgrounds Physical structure of the BJT BJT is a semiconductor device having a three-layer structure with three external electrodes, the emitter (E), the base (B), and the collector (C). As shown in Fig. 1, the structure may be p-n-p or n-p-n type. Despite of the transistor type the emitter layer has always more acceptor or donor impurities added than the base or the collector layer. This asymmetry results from different roles the emitter and the collector layers play in the BJT. In normal operation of the BJT (as an amplifier), the base-emitter junction is forward biased and the base-collector junction is reverse biased. Transistor amplification is controlled by changing the current flow through the base-emitter junction. C N C . C P C . P B. N B. B . B . E . N . E P . E E (a) (b) Fig. 1. The n-p-n BJT (a) and the p-n-p BJT (b) along with their symbols There are three operating configurations of the BJT. These are the common-emitter (OE) configuration, the common-base configuration (OB), and the common-collector (OC) configuration. These configurations are shown in Fig. 2. (a) (b) (c) Fig. 2 The n-p-n transistor operating configurations: (a) common-emitter, (b) common-base, (c) common-collector DC characteristics Four types of characteristics can be defined for each of the transistor operating configurations. -

Lecture Notes for Digital Electronics

Lecture Notes for Digital Electronics Raymond E. Frey Physics Department University of Oregon Eugene, OR 97403, USA [email protected] March, 2000 1 Basic Digital Concepts By converting continuous analog signals into a finite number of discrete states, a process called digitization, then to the extent that the states are sufficiently well separated so that noise does create errors, the resulting digital signals allow the following (slightly idealized): • storage over arbitrary periods of time • flawless retrieval and reproduction of the stored information • flawless transmission of the information Some information is intrinsically digital, so it is natural to process and manipulate it using purely digital techniques. Examples are numbers and words. The drawback to digitization is that a single analog signal (e.g. a voltage which is a function of time, like a stereo signal) needs many discrete states, or bits, in order to give a satisfactory reproduction. For example, it requires a minimum of 10 bits to determine a voltage at any given time to an accuracy of ≈ 0:1%. For transmission, one now requires 10 lines instead of the one original analog line. The explosion in digital techniques and technology has been made possible by the incred- ible increase in the density of digital circuitry, its robust performance, its relatively low cost, and its speed. The requirement of using many bits in reproduction is no longer an issue: The more the better. This circuitry is based upon the transistor, which can be operated as a switch with two states. Hence, the digital information is intrinsically binary. So in practice, the terms digital and binary are used interchangeably. -

Introduction (Pdf)

chapter1.fm Page 1 Thursday, August 17, 2000 4:43 PM CHAPTER 1 INTRODUCTION The evolution of digital circuit design n Compelling issues in digital circuit design n How to measure the quality of digital design n Valuable references 1.1 A Historical Perspective 1.2 Issues in Digital Integrated Circuit Design 1.3 Quality Metrics of A Digital Design 1.4 Summary 1.5 To Probe Further 1 chapter1.fm Page 2 Thursday, August 17, 2000 4:43 PM 2 INTRODUCTION Chapter 1 1.1A Historical Perspective The concept of digital data manipulation has made a dramatic impact on our society. One has long grown accustomed to the idea of digital computers. Evolving steadily from main- frame and minicomputers, personal and laptop computers have proliferated into daily life. More significant, however, is a continuous trend towards digital solutions in all other areas of electronics. Instrumentation was one of the first noncomputing domains where the potential benefits of digital data manipulation over analog processing were recognized. Other areas such as control were soon to follow. Only recently have we witnessed the con- version of telecommunications and consumer electronics towards the digital format. Increasingly, telephone data is transmitted and processed digitally over both wired and wireless networks. The compact disk has revolutionized the audio world, and digital video is following in its footsteps. The idea of implementing computational engines using an encoded data format is by no means an idea of our times. In the early nineteenth century, Babbage envisioned large- scale mechanical computing devices, called Difference Engines [Swade93]. Although these engines use the decimal number system rather than the binary representation now common in modern electronics, the underlying concepts are very similar. -

Field Effect Transistor (FET) Types and Features

Field Effect Transistor (FET) Types and Features Here I’m discussing about the topic FET. FET is another semiconductor device like BJT which can be used as switch, amplifier, resistor etc. FET consists of 3 terminals. Drain(D) Source(S) Gate(G) In these 3 terminals, Gate terminal acts as a controlling terminal. We know that a BJT acts as a current controlling device. Like that, FET also acts as a voltage controlling device. Here, the voltage between gate and source controls the drain current. So, it is called as voltage controlled device. FET Features: FET is more temperature stable compared to BJT It requires less space compared to BJT. So it is used heavily in circuits. FET has higher input impedance. So, it is more useful in amplifiers. Types of FETs: 1. Junction FET 2. MESFET 3. MOSFET Here I am discussing about the topic JFET. Junction FET (JFET): Basically the JFET is classified into 2 types. N-Channel JFET P-Channel JFET N-Channel JFET: When we consider a silicon bar and fabricated n-type at its two ends and heavily doped p-type materials at each side of the bar, the thin region will be remained as observed in figure is channel. Since this channel is in n-type bar this is called as n-channel FET. Here the current is carried by electrons. P-Channel FET: When we consider a silicon bar and fabricated p-type at its two ends and heavily doped n-type materials at each side of the bar, here the thin region remained as observed in figure is channel. -

Digital Electronics Part II - Circuits

Digital Electronics Part II - Circuits Dr. I. J. Wassell Gates from Transistors 1 Introduction • Logic circuits are non-linear, consequently we will introduce a graphical technique for analysing such circuits • The construction of an NMOS inverter from an n-channel field effect transistor (FET) is described • CMOS logic is then introduced Solving Non-linear circuits • First of all we need to introduce Ohm’s Law. For a linear component such as a resistor, this states that the voltage across the device is proportional to the current through it, i.e., V = IR • We will apply this concept to a simple circuit consisting of 2 resistors in series connected across an ideal voltage source – known as a potential divider 2 Potential Divider • What is the voltage at point x relative to the the 0V point? I V = V1 +V2 V = IR V = IR R1 V1 1 1 2 2 V x V = IR1 + IR2 = I(R1 + R2 ) R 2 V2 V I = 0V (R1 + R2) V R2 Vx = V2 = R2 = V (R1 + R2 ) R1 + R2 Potential Divider • How can we do this graphically? I So if V = 10V, R1 = 1 Ω and R2 = 2 Ω R V 1 1 V x R2 2 Vx = V =10 = 7.6 V R R + R 1+ 2 2 V2 1 2 0V Current Current through through R2 (2 Ω) R1 (1 Ω) 0V Voltage x= 6.7V Voltage V= 10V across R2 across R1 3 Graphical Approach • Clearly approach works for a linear circuit. • How could we apply this if we have a non- linear device, e.g., a transistor in place of R2? • What we do is substitute the V-I characteristic of the non-linear device in place of the linear characteristic (a straight line due to Ohm’s Law) used previously for R2 Graphical Approach