Fast and Energy-Efficient Monocular Depth Estimation on Embedded

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Penguin Computing Upgrades Corona with Latest AMD Radeon Instinct GPU Technology for Enhanced ML and AI Capabilities

Penguin Computing Upgrades Corona with latest AMD Radeon Instinct GPU Technology for Enhanced ML and AI Capabilities November 18, 2019 Fremont, CA., November 18, 2019 -Penguin Computing, a leader in high-performance computing (HPC), artificial intelligence (AI), and enterprise data center solutions and services, today announced that Corona, an HPC cluster first delivered to Lawrence Livermore National Lab (LLNL) in late 2018, has been upgraded with the newest AMD Radeon Instinct™ MI60 accelerators, based on Vega which, per AMD, is the World’s 1st 7nm GPU architecture that brings PCIe® 4.0 support. This upgrade is the latest example of Penguin Computing and LLNL’s ongoing collaboration aimed at providing additional capabilities to the LLNL user community. As previously released, the cluster consists of 170 two-socket nodes with 24-core AMD EPYCTM 7401 processors and a PCIe 1.6 Terabyte (TB) nonvolatile (solid-state) memory device. Each Corona compute node is GPU-ready with half of those nodes today utilizing four AMD Radeon Instinct MI25 accelerators per node, delivering 4.2 petaFLOPS of FP32 peak performance. With the MI60 upgrade, the cluster increases its potential PFLOPS peak performance to 9.45 petaFLOPS of FP32 peak performance. This brings significantly greater performance and AI capabilities to the research communities. “The Penguin Computing DOE team continues our collaborative venture with our vendor partners AMD and Mellanox to ensure the Livermore Corona GPU enhancements expand the capabilities to continue their mission outreach within various machine learning communities,” said Ken Gudenrath, Director of Federal Systems at Penguin Computing. Corona is being made available to industry through LLNL’s High Performance Computing Innovation Center (HPCIC). -

Survey and Benchmarking of Machine Learning Accelerators

1 Survey and Benchmarking of Machine Learning Accelerators Albert Reuther, Peter Michaleas, Michael Jones, Vijay Gadepally, Siddharth Samsi, and Jeremy Kepner MIT Lincoln Laboratory Supercomputing Center Lexington, MA, USA freuther,pmichaleas,michael.jones,vijayg,sid,[email protected] Abstract—Advances in multicore processors and accelerators components play a major role in the success or failure of an have opened the flood gates to greater exploration and application AI system. of machine learning techniques to a variety of applications. These advances, along with breakdowns of several trends including Moore’s Law, have prompted an explosion of processors and accelerators that promise even greater computational and ma- chine learning capabilities. These processors and accelerators are coming in many forms, from CPUs and GPUs to ASICs, FPGAs, and dataflow accelerators. This paper surveys the current state of these processors and accelerators that have been publicly announced with performance and power consumption numbers. The performance and power values are plotted on a scatter graph and a number of dimensions and observations from the trends on this plot are discussed and analyzed. For instance, there are interesting trends in the plot regarding power consumption, numerical precision, and inference versus training. We then select and benchmark two commercially- available low size, weight, and power (SWaP) accelerators as these processors are the most interesting for embedded and Fig. 1. Canonical AI architecture consists of sensors, data conditioning, mobile machine learning inference applications that are most algorithms, modern computing, robust AI, human-machine teaming, and users (missions). Each step is critical in developing end-to-end AI applications and applicable to the DoD and other SWaP constrained users. -

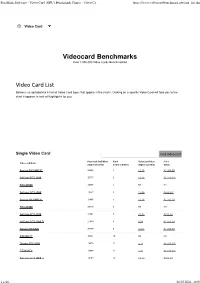

Videocard Benchmarks

Software Hardware Benchmarks Services Store Support About Us Forums 0 CPU Benchmarks Video Card Benchmarks Hard Drive Benchmarks RAM PC Systems Android iOS / iPhone Videocard Benchmarks Over 1,000,000 Video Cards Benchmarked Video Card List Below is an alphabetical list of all Video Card types that appear in the charts. Clicking on a specific Video Card will take you to the chart it appears in and will highlight it for you. Find Videocard VIDEO CARD Single Video Card Passmark G3D Rank Videocard Value Price Videocard Name Mark (lower is better) (higher is better) (USD) High End (higher is better) 3DP Edition 826 822 NA NA High Mid Range Low Mid Range 9xx Soldiers sans frontiers Sigma 2 21 1926 NA NA Low End 15FF 8229 114 NA NA 64MB DDR GeForce3 Ti 200 5 2004 NA NA Best Value Common 64MB GeForce2 MX with TV Out 2 2103 NA NA Market Share (30 Days) 128 DDR Radeon 9700 TX w/TV-Out 44 1825 NA NA 128 DDR Radeon 9800 Pro 62 1768 NA NA 0 Compare 128MB DDR Radeon 9800 Pro 66 1757 NA NA 128MB RADEON X600 SE 49 1809 NA NA Video Card Mega List 256MB DDR Radeon 9800 XT 37 1853 NA NA Search Model 256MB RADEON X600 67 1751 NA NA GPU Compute 7900 MOD - Radeon HD 6520G 610 1040 NA NA Video Card Chart 7900 MOD - Radeon HD 6550D 892 775 NA NA A6 Micro-6500T Quad-Core APU with RadeonR4 220 1421 NA NA A10-8700P 513 1150 NA NA ABIT Siluro T400 3 2059 NA NA ALL-IN-WONDER 9000 4 2024 NA NA ALL-IN-WONDER 9800 23 1918 NA NA ALL-IN-WONDER RADEON 8500DV 5 2009 NA NA ALL-IN-WONDER X800 GT 84 1686 NA NA All-in-Wonder X1800XL 30 1889 NA NA All-in-Wonder X1900 127 1552 -

AI Chips: What They Are and Why They Matter

APRIL 2020 AI Chips: What They Are and Why They Matter An AI Chips Reference AUTHORS Saif M. Khan Alexander Mann Table of Contents Introduction and Summary 3 The Laws of Chip Innovation 7 Transistor Shrinkage: Moore’s Law 7 Efficiency and Speed Improvements 8 Increasing Transistor Density Unlocks Improved Designs for Efficiency and Speed 9 Transistor Design is Reaching Fundamental Size Limits 10 The Slowing of Moore’s Law and the Decline of General-Purpose Chips 10 The Economies of Scale of General-Purpose Chips 10 Costs are Increasing Faster than the Semiconductor Market 11 The Semiconductor Industry’s Growth Rate is Unlikely to Increase 14 Chip Improvements as Moore’s Law Slows 15 Transistor Improvements Continue, but are Slowing 16 Improved Transistor Density Enables Specialization 18 The AI Chip Zoo 19 AI Chip Types 20 AI Chip Benchmarks 22 The Value of State-of-the-Art AI Chips 23 The Efficiency of State-of-the-Art AI Chips Translates into Cost-Effectiveness 23 Compute-Intensive AI Algorithms are Bottlenecked by Chip Costs and Speed 26 U.S. and Chinese AI Chips and Implications for National Competitiveness 27 Appendix A: Basics of Semiconductors and Chips 31 Appendix B: How AI Chips Work 33 Parallel Computing 33 Low-Precision Computing 34 Memory Optimization 35 Domain-Specific Languages 36 Appendix C: AI Chip Benchmarking Studies 37 Appendix D: Chip Economics Model 39 Chip Transistor Density, Design Costs, and Energy Costs 40 Foundry, Assembly, Test and Packaging Costs 41 Acknowledgments 44 Center for Security and Emerging Technology | 2 Introduction and Summary Artificial intelligence will play an important role in national and international security in the years to come. -

GPU Developments 2017T

GPU Developments 2017 2018 GPU Developments 2017t © Copyright Jon Peddie Research 2018. All rights reserved. Reproduction in whole or in part is prohibited without written permission from Jon Peddie Research. This report is the property of Jon Peddie Research (JPR) and made available to a restricted number of clients only upon these terms and conditions. Agreement not to copy or disclose. This report and all future reports or other materials provided by JPR pursuant to this subscription (collectively, “Reports”) are protected by: (i) federal copyright, pursuant to the Copyright Act of 1976; and (ii) the nondisclosure provisions set forth immediately following. License, exclusive use, and agreement not to disclose. Reports are the trade secret property exclusively of JPR and are made available to a restricted number of clients, for their exclusive use and only upon the following terms and conditions. JPR grants site-wide license to read and utilize the information in the Reports, exclusively to the initial subscriber to the Reports, its subsidiaries, divisions, and employees (collectively, “Subscriber”). The Reports shall, at all times, be treated by Subscriber as proprietary and confidential documents, for internal use only. Subscriber agrees that it will not reproduce for or share any of the material in the Reports (“Material”) with any entity or individual other than Subscriber (“Shared Third Party”) (collectively, “Share” or “Sharing”), without the advance written permission of JPR. Subscriber shall be liable for any breach of this agreement and shall be subject to cancellation of its subscription to Reports. Without limiting this liability, Subscriber shall be liable for any damages suffered by JPR as a result of any Sharing of any Material, without advance written permission of JPR. -

AMD Firepro Accelerators for HPE Proliant Servers Overview

QuickSpecs AMD FirePro Accelerators for HPE ProLiant Servers Overview AMD Accelerators for HPE ProLiant Servers Hewlett Packard Enterprise supports, on select HPE ProLiant servers, computational accelerator modules based on AMD® FirePro™ Graphical Processing Unit (GPU) technology. The following AMD accelerators are available from HPE. • HPE AMD FirePro S9150 Accelerator Kit • HPE AMD FirePro S7150x2 Accelerator Kit • HPE AMD Radeon Pro WX2100 Graphics Accelerator • HPE AMD Radeon Instinct MI25 Graphics Accelerator • HPE AMD Radeon Pro WX7100 Accelerator Based on AMD’s Graphics Core Next (GCN) technology, the AMD FirePro GPUs enable seamless integration of accelerated computing and digital rendering with HPE ProLiant servers for high-performance computing and large data center, scale-out deployments. The AMD GPUs support AMD STREAM technology, a set of GPU hardware and software features designed specifically to address high-performance workloads and workflows, including application requirements for high single and double floating point performance, ECC Memory support for increased computational accuracy, bi-directional low latency data transfers, and more. AMD cards are optimized for OpenCL™, an open and cross-platform programming standard used for general-purpose computations. When combined with the AMD APP Acceleration Software Development Kit and AMD supported development tools such as compilers and libraries, developers and customers can take full advantage of AMD for GPU compute. The AMD cards also support OpenGL and other rendering applications for full graphics processing of complex 3D models. The AMD accelerators provide all of the standard benefits of GPU computing while enabling maximum reliability and tight integration with system monitoring and management tools such as HPE Insight Cluster Management Utility. -

AMD EPYC + Radeon Instinct Platform Configuration

Business Overview AMD Server and Workstation GPUs Enterprise Sales Team July 13, 2017 JULY 2017 | AMD CONFIDENTIAL 1 COMPUTE JULY 2017 | AMD CONFIDENTIAL 23 Machine Intelligence Compute Datacenter Infrastructure Today Homogenous Processors Network Infrastructure Open Source Software Open Interconnect Some installations of: Proprietary Accelerators Proprietary Accelerator Software Proprietary Accelerator Interconnect User JULY 2017 | AMD CONFIDENTIAL 25 Machine Intelligence Compute Datacenter Infrastructure Tomorrow Heterogeneous Processors Network Infrastructure Open Source Software Open Interconnect Open Accelerators User JULY 2017 | AMD CONFIDENTIAL 26 Radeon Instinct™ Cloud / Hyperscale Financial Services Energy Life Sciences Automotive Optimized Machine Learning / Deep Learning Frameworks and Applications ROCm Open Software Platform Radeon Instinct Hardware Platform Address market verticals that use a common infrastructure to leverage the investments and scale fast across multiple industries JULY 2017 | AMD CONFIDENTIAL 27 Radeon Instinct Differentiation FP16 and FP32 Performance Leadership ROCm Open Software Platform Flexible AMD EPYC + Radeon Instinct Platform Configuration Enhanced GPU-to-GPU Communication for Lower Latency Leading MxGPU Security & Determinism with Hardware SR-IOV JULY 2017 | AMD CONFIDENTIAL 28 Radeon Instinct Line Up for 2017 Radeon Instinct™ MI25 Radeon Instinct™ MI6 Radeon Instinct™ MI8 World’s Fastest Training Accelerator Versatile Accelerator Compact Inference Accelerator “Vega” GPU Architecture “Polaris” -

AMD EPYC Cpus, AMD Radeon Instinct Gpus and Rocm Open Source Software to Power World’S Fastest Supercomputer at Oak Ridge National Laboratory

May 7, 2019 AMD EPYC CPUs, AMD Radeon Instinct GPUs and ROCm Open Source Software to Power World’s Fastest Supercomputer at Oak Ridge National Laboratory Collaboration with Cray targets over 1.5 exaflops of next-generation AI and HPC processing performance in Frontier system by 2021 SANTA CLARA, Calif., May 07, 2019 (GLOBE NEWSWIRE) -- AMD (NASDAQ: AMD) today joined the U.S. Department of Energy (DOE), Oak Ridge National Laboratory (ORNL) and Cray Inc. in announcing what is expected to be the world’s fastest exascale-class supercomputer, scheduled to be delivered to ORNL in 2021. To deliver what is expected to be more than 1.5 exaflops of expected processing performance, the Frontier system is designed to use future generation High Performance Computing (HPC) and Artificial Intelligence (AI) optimized, custom AMD EPYC™ CPU, and AMD Radeon™ Instinct GPU processors. Researchers at ORNL will use the Frontier system’s unprecedented computing power and next generation AI techniques to simulate, model and advance understanding of the interactions underlying the science of weather, sub-atomic structures, genomics, physics, and other important scientific fields. “AMD is proud to partner with Cray and ORNL to deliver what is expected to be the world’s most powerful supercomputer,” said Forrest Norrod, senior vice president and general manager, AMD Datacenter and Embedded Systems Group. “Frontier will feature custom CPU and GPU technology from AMD and represents the latest achievement on a long list of technology innovations AMD has contributed -

ORNL Advance Galaxy Simulations with AMD Instinct™ MI100 Gpus

ORNL Advance Galaxy Simulations with AMD Instinct™ MI100 GPUs Accelerating galaxy formation research at unprecedented scale and resolution using AMD powered supercomputing CUSTOMER Supercomputing is revolutionizing and one of the chief architects of CHOLLA. science, with the fastest systems in the “But a revolution in astronomy over the last world providing unparalleled path to 40 years has been our ability to use numerical discovery. Oak Ridge National Laboratory simulations to try to understand how the (ORNL) is at the forefront of this trend, universe is evolving. Unlike most physical and already hosts one of the fastest sciences where you can conduct experiments, supercomputer in the world. But ORNL and the time scales of the experiments INDUSTRY has commissioned a new supercomputer happen in relevant human lifetimes, in for its Leadership Computing Facility astronomy, things change on much longer Scientific research (OLCF). Called Frontier, it’s timescales. The only way we expected to be the fastest “Having access to this can get a moving picture of CHALLENGES open science supercomputer exascale machine is a things is by conducting Increasing scale and resolution with in the world when it arrives in game changer for the numerical simulations.” numerical simulation of galactic evolution 2021, and one of the first to kinds of problems that we CHOLLA was created to with CHOLLA software offer exascale computing can simulate.” provide this time-based power of 1 exaFLOPS or more. It analysis, particularly will also have both AMD CPUs Evan Schneider, Assistant SOLUTION focusing on galaxy and AMD GPUs at its heart. Professor of Physics and Deploy AMD Instinct MI100 GPUs with formation, with its Astronomy at the ROCm open software to prepare for ORNL is preparing eight key processing accelerated by University of Pittsburgh Frontier supercomputer scientific applications for GPUs. -

AMD Takes High-Performance Datacenter Computing to the Next Horizon

November 6, 2018 AMD Takes High-Performance Datacenter Computing to the Next Horizon — Launches World’s first 7nm High-performance GPU for Machine Learning and AI; Demonstrates World’s First High-performance 7nm x86 CPU Powered by “Zen 2” Processor Core and Breakthrough Chiplet Design — Codenamed “Rome,” the world’s first high- performance 7nm datacenter CPU is powered by up to 64 “Zen 2” processor cores and a breakthrough chiplet design. — Amazon Web Services Announces Immediate Availability of AMD EPYC processor- powered Versions of Its Popular Instance Families — SAN FRANCISCO, Nov. 06, 2018 (GLOBE NEWSWIRE) -- AMD (NASDAQ: AMD) today demonstrated its total commitment to datacenter computing innovation at its Next Horizon event in San Francisco by detailing its upcoming 7nm compute and graphics product portfolio designed to extend the capabilities of the modern datacenter. During the event, AMD shared new specifics on its upcoming “Zen 2” processor core architecture, detailed its revolutionary chiplet-based x86 CPU design, launched the 7nm AMD Radeon Instinct™ MI60 graphics accelerator and provided the first public demonstration of its next-generation 7nm EPYC™ server processor codenamed “Rome”. Amazon Web Services (AWS), the world’s most comprehensive and broadly adopted cloud platform company, joined AMD at the event to announce the availability of three of its popular instance families on the Amazon Elastic Compute Cloud (EC2) powered by the AMD EPYC™ processor. “The multi-year investments we have made in our datacenter hardware and software roadmaps are driving growing adoption of our CPUs and GPUs across cloud, enterprise and HPC customers,” said Dr. Lisa Su, president and CEO, AMD. -

Passmark Software - Video Card (GPU) Benchmark Charts - Video Ca

PassMark Software - Video Card (GPU) Benchmark Charts - Video Ca... https://www.videocardbenchmark.net/gpu_list.php Videocard Benchmarks Over 1,000,000 Video Cards Benchmarked Below is an alphabetical list of all Video Card types that appear in the charts. Clicking on a specific Video Card will take you to the chart it appears in and will highlight it for you. Passmark G3D Mark Rank Videocard Value Price Videocard Name (higher is better) (lower is better) (higher is better) (USD) Radeon RX 6900 XT 25988 1 11.30 $2,300.00 GeForce RTX 3090 25747 2 10.96 $2,349.99* RTX A5000 24590 3 NA NA GeForce RTX 3080 24337 4 27.04 $899.99* Radeon RX 6800 XT 23606 5 12.34 $1,913.29 RTX A6000 22719 6 NA NA GeForce RTX 3070 21781 7 27.23 $799.99 GeForce RTX 2080 Ti 21689 8 9.08 $2,389.99 Radeon RX 6800 20780 9 11.54 $1,799.99 RX6800 XT 20391 10 NA NA Quadro RTX 6000 19878 11 3.16 $6,300.00* TITAN RTX 19868 12 7.95 $2,499.00* GeForce RTX 3060 Ti 19703 13 38.64 $509.99 1 z 66 28.05.2021, 10:09 PassMark Software - Video Card (GPU) Benchmark Charts - Video Ca... https://www.videocardbenchmark.net/gpu_list.php Passmark G3D Mark Rank Videocard Value Price Videocard Name (higher is better) (lower is better) (higher is better) (USD) TITAN V 19377 16 5.72 $3,390.00 Radeon RX 6700 XT 18783 17 15.11 $1,243.00 GeForce RTX 2080 18604 18 18.60 $999.99 TITAN Xp 18584 19 NA NA NVIDIA TITAN Xp 18280 20 10.21 $1,790.00 GeForce RTX 2070 SUPER 18118 21 16.62 $1,089.99 GeForce GTX 1080 Ti 17995 22 16.36 $1,099.99 TITAN Xp COLLECTORS EDITION 17860 23 NA NA Radeon Pro VII 17404 -

Cpus, Gpus and Accelerators X86 Intel Server Micro-Architectures (1/2)

CPUs, GPUs and accelerators x86 Intel server micro-architectures (1/2) Microarchitecture Technology Launch year Highlights Skylake-SP 14nm 2017 Improved frontend and execution units More load/store bandwidth Improved hyperthreading AVX-512 Cascade Lake 14nm++ 2019 Vector Neural Network Instructions (VNNI) to improve inference performance Support 3D XPoint-based memory modules and Optane DC Security mitigations Cooper Lake 14nm++ 2020 bfloat16 (brain floating point format) S o Intel server micro-architectures (2/2) ur c e: Microarchitecture Technology Launch Highlights A CPU codename year n Sunny Cove 10nm+ 2019 Single threaded performance a Ice Lake Scalable New instructions n Tiger Lake? Improved scalability dt Larger L1, L2, μop caches and 2nd levele TLB More execution ports AVX-512 c h Willow Cove 10nm 2020? Cache redesign ? New transistor optimization Security Features Golden Cove 7/10nm? 2021? Single threaded performance ? AI Performance Networking/5G Performance Security Features Other Intel CPU architectures ● Intel Nervana AI Processor NNP-L-1000 (H2 2019-) ○ Accelerates AI inference for companies with high workload demands ○ Optimized across memory, bandwidth, utilization and power ○ Spring Crest 3-4x faster training than Lake Crest, introduced in 2017 ○ Supports bfloat16 ● Hybrid CPUs ○ Will be enabled by Foveros, the 3D chip stacking technology recently demonstrated ● Itanium ○ It will be finally discontinued in 2021 (the only remaining customer is HP) Other Intel-related news ● Record Q3 2018 results ○ Data-centric revenue