A Low-Power Field-Programmable Gate Array Routing Fabric Mingjie Lin, Member, IEEE, and Abbas El Gamal, Fellow, IEEE

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Switched-Capacitor Circuits

Switched-Capacitor Circuits David Johns and Ken Martin University of Toronto ([email protected]) ([email protected]) University of Toronto 1 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Opamps • Ideal opamps usually assumed. • Important non-idealities — dc gain: sets the accuracy of charge transfer, hence, transfer-function accuracy. — unity-gain freq, phase margin & slew-rate: sets the max clocking frequency. A general rule is that unity-gain freq should be 5 times (or more) higher than the clock-freq. — dc offset: Can create dc offset at output. Circuit techniques to combat this which also reduce 1/f noise. University of Toronto 2 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Double-Poly Capacitors metal C1 metal poly1 Cp1 thin oxide bottom plate C1 poly2 Cp2 thick oxide C p1 Cp2 (substrate - ac ground) cross-section view equivalent circuit • Substantial parasitics with large bottom plate capacitance (20 percent of C1) • Also, metal-metal capacitors are used but have even larger parasitic capacitances. University of Toronto 3 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Switches I I Symbol n-channel v1 v2 v1 v2 I transmission I I gate v1 v p-channel v 2 1 v2 I • Mosfet switches are good switches. — off-resistance near G: range — on-resistance in 100: to 5k: range (depends on transistor sizing) • However, have non-linear parasitic capacitances. University of Toronto 4 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Non-Overlapping Clocks I1 T Von I I1 Voff n – 2 n – 1 n n + 1 tTe delay 1 I fs { --- delay V 2 T on I Voff 2 n – 32e n – 12e n + 12e tTe • Non-overlapping clocks — both clocks are never on at same time • Needed to ensure charge is not inadvertently lost. -

Switched Capacitor Concepts & Circuits

Switched Capacitor Concepts & Circuits Outline • Why Switched Capacitor circuits? – Historical Perspective – Basic Building Blocks • Switched Capacitors as Resistors • Switched Capacitor Integrators – Discrete time & charge transfer concepts – Parasitic insensitive circuits • Signal Flow Graphs • Switched Capacitor Filters – Comparison to Active RC filters – Advantages of Fully Differential filters • Switched Capacitor Gain Circuits • Reducing the Effects of Charge Injection • Tradeoff between Speed and Charge Injection Why Switched Capacitor Circuits? • Historical Perspective – As MOS processes came to the forefront in the late 1970s and early 1980s, the advantages of integrating analog blocks such as active filters on the same chip with digital logic became a driving force for inovation. – Integrating active filters using resistors and capacitors to acturately set time constants has always been difficult, because of large process variations (> +/- 30%) and the fact that resistors and capacitors don’t naturally match each other. – So, analog engineers turned to the building blocks native to MOS processes to build their circuits, switches & capacitors. Since time constants can be set by the ratio of capacitors, very accurate filter responses became possible using switched capacitor techniques Æ Mixed-Signal Design was born! Switched Capacitor Building Blocks • Capacitors: poly-poly, MiM, metal sandwich & finger caps • Switches: NMOS, PMOS, T-gate • Op Amps: at first all NMOS designs, now CMOS Non-Overlapping Clocks • Non-overlapping clocks are used to insure that one set of switches turns off before the next set turns on, so that charge only flows where intended. (“break before make”) • Note the notation used to indicate time based on clock periods: ... (n-1)T, (n-½)T, nT, (n+½)T, (n+1)T .. -

Printed Circuit Board Mount Switches Shock Proof • Waterproof • Explosion

shock proof • waterproof • explosion proof Printed Circuit Board Mount Switches These versatile switches are a great choice for many applications due to their small size and variety of connection styles. Although these switches are built to connect to a printed circuit board, they can also be retrotted for nearly any application by connecting wire leads. These switches can sense a pressure ranging from 6 inches of water all the way up to 65 PSI. For a frame of reference, a trumpet player blows 55 inches of water (or 2 PSI) on average, so these switches have a broad range. They can also be used to sense a vacuum ranging between 6 inches of water to 65 inches of water. Therefore, these miniature single pole and double pole switches are used as pressure, vacuum, or dierential pressure switches where moderate accuracy is sucient. Presair switches deliver critical benefits: CSPSSGA - PC Mount Switch SAFE: Presair switches deliver complete electrical isolation with zero voltage at the actuator to shock the user or spark an explosion. 1”x1”x1.5” ECONOMICAL:Presair’s switching system costs are comparable or lower than digital controls meeting the needs of original equipment manufacturers. ACCURATE: All switches are 100% tested to meet 100,000+ cycle life. General Specification: RATING: 1 amp resistive 250 VAC Ratings are dependent on actuation pressure and must be derated at lower pressures. APPROVAL: UL Recognized, CUL Recognized. File #E80254 MATERIAL: Lower body: Rynite w/ pin terminals molded Upper body: Acetal Diaphram material is dependent on application. PRESSURE RANGE: When used as a pressure or vacuum switch the actuation point must be factory set. -

Switched-Capacitor Integrator

EE247 Lecture 10 • Switched-capacitor filters (continued) – Switched-capacitor integrators • DDI & LDI integrators – Effect of parasitic capacitance – Bottom-plate integrator topology – Switched-capacitor resonators – Bandpass filters – Lowpass filters – Switched-capacitor filter design considerations • Termination implementation • Transmission zero implementation • Limitations imposed by non-idealities EECS 247 Lecture 10 Switched-Capacitor Filters © 2008 H. K. Page 1 Switched-Capacitor Integrator C φ φ I φ 1 2 1 Vin - φ 2 Cs Vo + T=1/fs C C φ I φ I 1 2 Vin Vin - - C C s s Vo Vo + + φ High φ 1 2 High Æ C Charged to Vin s ÆCharge transferred from Cs to CI EECS 247 Lecture 10 Switched-Capacitor Filters © 2008 H. K. Page 2 Switched-Capacitor Integrator Output Sampled on φ1 φ φ 1 2 Vin CI φ - 1 Cs Vo Vo1 + φ φ φ φ φ Clock 1 2 1 2 1 Vin VCs Vo Vo1 EECS 247 Lecture 10 Switched-Capacitor Filters © 2008 H. K. Page 3 Switched-Capacitor Integrator ( (n-1)T n-3/2)Ts s (n-1/2)Ts nTs (n+1/2)Ts (n+1)Ts φ φ φ φ φ Clock 1 2 1 2 1 Vin Vs Vo Vo1 Φ 1 Æ Qs [(n-1)Ts]= Cs Vi [(n-1)Ts] , QI [(n-1)Ts] = QI [(n-3/2)Ts] Φ 2 Æ Qs [(n-1/2) Ts] = 0 , QI [(n-1/2) Ts] = QI [(n-1) Ts] + Qs [(n-1) Ts] Φ 1 _Æ Qs [nTs ] = Cs Vi [nTs ] , QI [nTs ] = QI[(n-1) Ts ] + Qs [(n-1) Ts] Since Vo1= - QI /CI & Vi = Qs / Cs Æ CI Vo1(nTs) = CI Vo1 [(n-1) Ts ] -Cs Vi [(n-1) Ts ] EECS 247 Lecture 10 Switched-Capacitor Filters © 2008 H. -

Practical Issues Designing Switched-Capacitor Circuit

Practical Issues Designing Switched-Capacitor Circuit ECEN 622 (ESS) Fall 2011 Practical Issues Designing Switched-Capacitor Circuit Material partially prepared by Sang Wook Park and Shouli Yan ELEN 622 Fall 2011 1 / 27 Switched-Capacitor practical issues Practical Issues Designing Switched-Capacitor Circuit MOS switch G G S Cov Cox Cov D S D Ron o Excellent Roff o Non-idea Effect Charge injection, Clock feed-through Finite and nonlinear Ron ELEN 622 Fall 2011 2 / 27 Switched-Capacitor practical issues Practical Issues Designing Switched-Capacitor Circuit Charge Injection G Qch1 Qch2 C VS o During TR. is turned on, Qch is formed at channel surface Qch = WLC OX (VGS −Vth ) When TR. is off, Qch1 is absorbed by Vs, but Qch2 is injected to C o Charge injected through overlap capacitor o Appeared as an offset voltage error on C ELEN 622 Fall 2011 3 / 27 Switched-Capacitor practical issues Practical Issues Designing Switched-Capacitor Circuit Charge Injection Effect CLK Ideal sw. Vout MOS sw. 0.1pF 1V CLK o When clock changes from high to low, Qch2 is injected to C o Compared to ideal sw., MOS sw. creates voltage error on Vout ELEN 622 Fall 2011 4 / 27 Switched-Capacitor practical issues Practical Issues Designing Switched-Capacitor Circuit Decrease Charge Injection Effect (1) CLK Vout W/L = 1/0.4 0.1pF 1V W/L = 10/0.4 o Decrease the effect of Qch o Use either bigger C or small TR. (small ratio of Cox/C) o Increased Ron ELEN 622 Fall 2011 5 / 27 Switched-Capacitor practical issues Practical Issues Designing Switched-Capacitor Circuit Decrease Charge Injection Effect (2) CLK CLKb 10/0.4 3.1/0.4 Vout With dummy sw. -

Introduction How Circuit Protection Devices Work?

Introduction Adding extra strain to any person or object can be a recipe for disaster. This is especially the case for electrical circuits. When they’re tasked with carrying more current than they were designed to handle, the added burden can lead to detrimental and dangerous circumstances. Not only could overloading your circuits damage or destroy your sensitive electronic equipment, but it could also generate extra heat in wires that weren’t meant to carry the load. If this happens, it can cause a fire in a matter of seconds. This is where an overcurrent protection device, such as a fused disconnect switch or a circuit breaker, comes in. Though they serve a similar purpose, these two components each have a unique design. Today, we’re sharing how they work and how to choose the right one for your project. Ready to learn more? Let’s dive in. How Circuit Protection Devices Work? The field of circuit protection technology is vast, designed to prevent circuits from risks associated with overvoltage, overcurrent, reverse-bias, electrostatic-discharge (ESD) and overtemperature events. Such risks include: • High-voltage transients • Capacitive coupling • Inductive kickback • Ground faults • High inrush currents From your smartphone battery to your steering wheel, these components are necessary to ensure safe and reliable electronics. While they all serve a valuable purpose, we’re delving deeper today into the specific field of overcurrent protection. Overcurrent protection devices are designed to disconnect or open a circuit quickly in the event that an overload or short-circuit occurs. This helps to mitigate any damage to the connected equipment and can also reduce the risk of electrical fires. -

Power Sense Switch & Fan Control Thermostat

Speed Controllers & Switches_8_DR_ref.qxd 6/11/2015 10:34 AM Page 17 POWER SENSE SWITCH & FAN CONTROL THERMOSTAT POWER SENSE SWITCH TYPE - VZ-IISNSE TECHNICAL DATA Switched Output Model Number Load Sense Range Max. Amps Enclosure Size, mm On = 2.5 - 15 amp VZ-ISNSE 5 153W x 110H x 60D Off = 0 - 1.5 amps SUGGESTED WIRING ARRANGEMENT The VZ-ISNSE is a 240V AC power sense switch that provides automatic on/off control of a fan or exhaust fan system. The unit detects the current of an appliance such as a clothes dryer, closing and opening the switched output 240V relay when the load sense range Switched Output parameters are met. Can be used with the VZ2-10TS, VZM0-28TS, VZ6-4PL or as a stand alone unit. In LED’s indicate when load is activated. 3-pin Socket Warning Not to be used with fans with EC motors Appliance or inverters. FAN CONTROL THERMOSTAT TECHNICAL DATA Model Temperature Maximum Number range Mounting Amps Dimensions, mm TFC6 5ºC to 30ºC Wall mountable 6.0 86W x 86H x 33D SELECTION TABLE The TFC6 is suitable for most 240-volt fans. The TFC6 can be set in two modes: Cool mode - will start the fan when the room temperature is higher than the set point. The Fantech Fan Control Thermostat has Heat mode - will start the fan when the room temperature is lower than the set point. been developed to control the operation of a 240-volt fan based on the setting made on the thermostat dial. It can be set to turn on a fan when the WIRING DIAGRAM room temperature is either higher or lower than the set point. -

FSW Fuse-Switch-Disconnectors

Motors | Automation | Energy | Transmission & Distribution | Coatings FSW Fuse-Switch-Disconnectors www.weg.net Fuse-Switch-Disconnectors The FSW Fuse-Switch-Disconnectors, developed according to International Standard IEC 60947-3 and bearing CE certification, are applied in electric circuits in general so as to provide the disconnection and protection against short circuits and overloads by means of NH blade contact fuses. In order to ensure a long lifespan, the FSW Fuse-Switch-Disconnectors are manufactured with reinforced thermoplastic materials and flame retardant. Additionaly, they feature contacts with silver coating, providing low power losses. Safety and Simplicity WEG switch-disconnector has several characteristics which aim at increasing security for operation and maintenance of the equipment, simplifying diagnoses and fuse replacement: g The switch-disconnector allows checking the state of the fuses through a transparent cover, besides featuring small openings which allow making electrical measurements without interrupting the operation. g As per IEC 60947-3, the switch-disconnector can perform the non- frequent opening under load. The FSW series has arc chambers for the extinction of the electric arc and disconnects all the phases together, ensuring full insulation between the load circuit and power supply. g In the opening of the switch-disconnector, the fuses remain fixed to the cover, preventing their drop or accidental contact between the energized parts. Furthermore, the cover is totally removable, allowing simple fuse replacement in a simple and safe area out of the electrical panel. g The switch-disconnectors also feature a built-in auxiliary contact in order to indicate when they are open or not properly closed. -

Thermostats, Thermal Cutoffs & Fuses

Temperature Controllers Bulb and Capillary Thermostats Thermostat Styles and Selection Construction Characteristics This type of control operates by expansion and contraction of causing the opening and closing of a snap-action switch. For heat- a liquid in response to temperature change. Liquid contained ing applications the contacts are normally closed and open on within the sensing bulb and capillary flexes a diaphragm, temperature rise. See Page 13-77 for typical wiring diagrams. Style A Style B Single-Pole Thermostat Bulb Double-Pole Thermostat ✴ General purpose ✴ Recommended for directly thermostat recommended Pilot Lamp controlling high wattage for most applications. (Optional on loads due to its Style B & ✴ Capable of controlling heavy duty contacts. C ONLY) loads from 120V/30A up ✴ Capable of controlling loads to 480V/20A Knob up to 30 Amps at 277 VAC and (Optional on 10 Amps at 480 VAC all Styles except F) Bezel Capillary (Optional on Style B & C ONLY Thermostat Electrical Ratings: Normally Closed Contacts, Open on Temperature Rise – Adjustable Stock Items Are Shown In RED Temp Ampacity at Bulb Bulb Capillary Thermostat Optional Thermostat Parts Instruction Control Range Line Voltage Dia. Length Length Part Sheet Type Style °F 120V 240V 277V 480V in in in Terminals Number Knob Bezel Pilot Lamp P/N 60–250 30 30 30 — 0.27 6.00 12 #10 screw TST-101-137 TST-104-103 n/a n/a IDP-119-102 60–250 30 30 30 — 0.38 4.63 48 #10 screw TST-101-131 TST-104-103 n/a n/a IDP-119-102 SPST A 70–245 30 30 15 15 0.25 5.50 12 #10 screw TST-101-130 Included -

TCI-W-U Series Wall Mounted Controller IOM-525 Installation and Operation Manual Installation and Set up Overview

TCI-W-U Series Wall Mounted Controller IOM-525 Installation and Operation Manual Installation and Set Up Overview Features......................................3 Duct Application............................4 Room Application...........................5 Wiring Schematics.....................6-12 Operation...............................13-14 Features Universal PID and/or binary control for any analog input/output signal and range. Multiple auxiliary functions: automatic enable, set point configuration Averaging, min and max functions Alarm monitoring of low and high limits Accuracy of +/- 2% RH Large Backlit display Displays Actual RH% and setpoint RH% Analog output displayed by a vertical bar Jumper selectable 0-10VDC or 4-20mA The Armstrong TCI-W-U controller can be used for either duct or room applications. 3 Duct Application The Armstrong D51772 is used in a duct application and includes the parts listed below: Armstrong Part number: D50390 (TCI-W-U Controller) Armstrong Part number: D50388 (SDC-H1 Transmitter) Please refer to your humidifiers IOM for proper placement of the D50388. (The D50388 will be referred to as a sensor in the IOM) The D50390 can be mounted in any location because the sensing of relative humidity is being done by the D50388. Max wire length from sensor to controller is 200 feet. 4 Room Application The Armstrong D51768 is a stand alone controller used in room applications, see below: Armstrong Part number: D51768 (TCI-W-U Controller) Please refer to your humidifiers IOM for mounting locations of the humidistat/controller as well as set up of the humidifier. This is only installation and set up for the controller. 5 Wiring Schematics HC6000 Series Humidifiers: Supply 2 24V Main Stat / Sensor In 6 A01 Modulating High Limit Sensor Armstrong 0-10 Vdc Stat Outdoor Temp. -

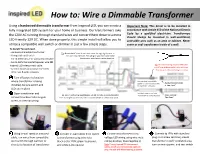

How To: Wire a Dimmable Transformer

How to: Wire a Dimmable Transformer Using a hardwired dimmable transformer from Inspired LED, you can create a Important Note: This driver is to be installed in accordance with Article 450 of the National Electric fully integrated LED system for your home or business. Our transformers take the 120V AC running through standard wires and convert them down to a more Code by a qualified electrician. Transformers should always be mounted in well-ventilated, LED friendly 12V DC. When done properly, this simple install will allow you to accessible area such as an attic or cabinet. Never utilize a compatible wall switch or dimmer in just a few simple steps… cover or seal transformer inside of a wall. To Install: You will need… - Hardwire dimmable transformer Tip: Route the AC wires from transformer through rigid spacer to - Compatible wall switch the open box extender. This will give you more room to tie 12VDC - 14-16 AWG Class 2 in-wall/armored cable transformer and dimmer wiring together. - 16-22 AWG thermostat/speaker wire OR Tip: To connect using Inspired LED cable, Inspired LED interconnect cable cut off one end connector, split and strip. - Junction box(es) (optional if needed) The side with white lettering is positive. - Wire nuts & cable strippers 1. Turn off power to location Use standard Inspired LED where transformer is being cables to run from transformer Standard end connectors installed, be sure switch and to standard 3.5mm jacks or Tiger Paws® LEDs are in place Use bulk cable to run from 2. Open transformer and Tip: For in-wall wiring applications, use 18-22 AWG 2-conductor cable transformer to screw terminals Screw Terminal remove knockout holes to gain Class 2 or higher (commonly sold as in-wall speaker or thermostat wire). -

Choosing the Best Capability Switch –

Choosing the Best Capability Switch – Capability Switches are designed for people with physical disabilities, providing them an alternative means to interact with speech generating devices, switch adapted devices including adapted therapeutic learning products, appliance controllers, and computers. Enabling Devices manufactures hundreds of switches but they operate in one of three ways: momentary, latch (i.e. on/off), and timed: Momentary – When you press a momentary switch, the device stays on as long as you maintain pressure on the switch. Latch – Turns on the device when the switch is pressed once and turns off the device when the switch is pressed again. An example of a latch switch is the On/Off Jumbo Switch (#791). Timed – When you press, it turns on a device for a preset amount of time (0 to 120 seconds). Enabling Devices also has a switch that allows you to choose either Momentary or Latched: Two Function Jumbo Switch (#7910). We also have a Switch Modifier (#605) that will change any momentary switch into a latch or timed switch. Which One Is Right For You? Enabling Devices takes pride in manufacturing hundreds of durable yet extremely sensitive capability switches at reasonable prices. However, it can be difficult to decide which switch would work best for your particular set of circumstances. In this article, we set forth important factors to consider when choosing a switch. Of course, our technical staff is available to address any additional questions or concerns you may have at [email protected]. 800-832-8697 www.enablingdevices.com When selecting a switch, there are several important factors to consider: Actions What actions can the person who will use the switch reliably perform? Activating the switch should not cause a person undue fatigue or pain, or compromise good muscle tone.