Polymorphic Blocks: Unifying High-Level Specification and Low

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Toastboard: Ubiquitous Instrumentation and Automated Checking of Breadboarded Circuits

The Toastboard: Ubiquitous Instrumentation and Automated Checking of Breadboarded Circuits Daniel Drew†, Julie L. Newcomb‡, William McGrath?, Filip Maksimovic†, David Mellis†, Bjoern Hartmann† †: UC Berkeley EECS, ‡: University of Washington PLSE, ? : Stanford University HCI Group ddrew73,fil,mellis,[email protected], [email protected], [email protected] ABSTRACT The recent proliferation of easy to use electronic components and toolkits has introduced a large number of novices to de- signing and building electronic projects. Nevertheless, debug- ging circuits remains a difficult and time-consuming task. This paper presents a novel debugging tool for electronic design projects, the Toastboard, that aims to reduce debugging time by improving upon the standard paradigm of point-wise circuit measurements. Ubiquitous instrumentation allows for imme- diate visualization of an entire breadboard’s state, meaning users can diagnose problems based on a wealth of data instead Figure 1. The Toastboard device and accompanying software. (1) LED bars indicate power, ground, or other voltage. (2) A push button triggers of having to form a single hypothesis and plan before taking a scan. (3) Quantitative voltage data is displayed in the accompanying a measurement. Basic connectivity information is displayed software. (4) Components are associated with testers that run on every visually on the circuit itself and quantitative data is displayed scan. (5) The voltage at a selected row can be viewed over time as a on the accompanying web interface. Software-based testing graph. functions further lower the expertise threshold for efficient debugging by diagnosing classes of circuit errors automati- cally. In an informal study, participants found the detailed, frustrating, and time-consuming to debug. -

Electronic and Electromechanical Prototyping

Electronic and electromechanical prototyping Introduction - ECAD Corso LM ‘Materiali Intelligenti e Biomimetici’ – Prof. A. Ahluwalia 4/05/2017 [email protected] After Breadboards: Matrix Boards We use breadboards for quick construction, Matrix Boards for laying out a project so it can be copied to make a Printed Circuit Board. This is a prototyping board, with copper pads in a matrix layout. You solder the components in place, and then simply cut pieces of wire, and solder them to make the circuit Printed Circuit Board The PCB is the physical board that holds and connects all of the electronic components. The circuits are formed by a thin layer of conducting material deposited, or "printed," on the surface of an insulating board known as the substrate. Individual electronic components are placed on the surface of the substrate and soldered to the interconnecting circuits. ECAD Electronic computer-aided design (ECAD) or Electronic design automation (EDA) is a category of software tools for designing electronic systems such as integrated circuits and printed circuit boards. The tools work together in a design flow that chip designers use to design and analyze entire semiconductor chips. Before EDA, integrated circuits were designed by hand and manually laid out. By the mid-1970s, developers started to automate the design along with the drafting. The first placement and routing tools were developed. Printed Circuit Board Design PCB ECAD Software (Ex. Eagle): PCB design in EAGLE is a two-step process. First you design your schematic, then you lay out a PCB based on that schematic. PCB Design (2) Your circuit design software will allow you to output the PCB layout in a format called Gerber with one file for each PCB layer (copper layers, solder mask, legend or silk) to allow manufacturing. -

Electronic Circuit Simulation and PCB Design

COURSE CODE COURSE TITLE L T P C ELECTRONICS CIRCUIT SIMULATION AND PCB 1152EC239 1 0 4 3 DESIGN a. Course Category: Program Elective b. Preamble: The course is aimed at making the students to understand electronic circuit simulation process for better understanding and designing of cost effective Printed Circuit Boards. Emphasizing the students to understand how to design a PCB layout of given circuit using available circuit simulation and PCB layout design CAD tools (free or licensed) .This course helps the student to simulate the circuit, develop the complete hardware circuit on PCB and assemble the components using SMD soldering technique c. Prerequisite Courses: Nil d. Related Courses: Analog Electronics, Linear Integrated Circuits e. Course Outcomes : Upon the successful completion of the course, students will be able to: Skill Level CO Course Outcomes (Based on Dave’s Nos. Taxonomy) Simulate and perform various analysis for the given Electronic CO1 S3 Circuit. CO2 Design a PCB Layout for the given circuit S4 CO3 Fabricate the PCB and assemble the components. S2 f. Correlation of COs with POs PO1 PO2 PO3 PO4 PO5 PO6 PO7 PO8 PO9 PO10 PO11 PO12 PSO1 PSO2 CO1 L M H - H - - - M - - M H H CO2 L M H - H - - - M - - M H H CO3 L M H - H - - - M - - M H H g. Examination scheme Examination Scheme for practical dominated course Internal evaluation Semester end evaluation (40M) (60M) Laboratory experiment Model laboratory test Part-A Part-B (15M) (25M) (20M) (40M) Performa Result Viv Reco Performa Result Viv Theory Performa Result Viv nce in and a rd nce in and a questions nce in and a- conductin analys Voc (4) conductin analys Voc to evaluate conductin analys Voc g is e g is e the g is e experime (3 ) ( 3) experime (5) ( 5) knowledge experime (10) (5) nt nt and nt ( 5 ) ( 15 ) understand (25) ing (20) h. -

Metadefender Core V4.12.2

MetaDefender Core v4.12.2 © 2018 OPSWAT, Inc. All rights reserved. OPSWAT®, MetadefenderTM and the OPSWAT logo are trademarks of OPSWAT, Inc. All other trademarks, trade names, service marks, service names, and images mentioned and/or used herein belong to their respective owners. Table of Contents About This Guide 13 Key Features of Metadefender Core 14 1. Quick Start with Metadefender Core 15 1.1. Installation 15 Operating system invariant initial steps 15 Basic setup 16 1.1.1. Configuration wizard 16 1.2. License Activation 21 1.3. Scan Files with Metadefender Core 21 2. Installing or Upgrading Metadefender Core 22 2.1. Recommended System Requirements 22 System Requirements For Server 22 Browser Requirements for the Metadefender Core Management Console 24 2.2. Installing Metadefender 25 Installation 25 Installation notes 25 2.2.1. Installing Metadefender Core using command line 26 2.2.2. Installing Metadefender Core using the Install Wizard 27 2.3. Upgrading MetaDefender Core 27 Upgrading from MetaDefender Core 3.x 27 Upgrading from MetaDefender Core 4.x 28 2.4. Metadefender Core Licensing 28 2.4.1. Activating Metadefender Licenses 28 2.4.2. Checking Your Metadefender Core License 35 2.5. Performance and Load Estimation 36 What to know before reading the results: Some factors that affect performance 36 How test results are calculated 37 Test Reports 37 Performance Report - Multi-Scanning On Linux 37 Performance Report - Multi-Scanning On Windows 41 2.6. Special installation options 46 Use RAMDISK for the tempdirectory 46 3. Configuring Metadefender Core 50 3.1. Management Console 50 3.2. -

Alexis Rodriguez Jr

Alexis Rodriguez Jr. 701 SW 62nd Blvd - Apt 104 - Gainesville - FL - 32604 Cell: 305-370-8334 Email: [email protected] Education: University of Florida Gainesville, FL Current M.S. Computer and Electrical Engineering University of Florida Gainesville, FL 2018 B.S. Electrical Engineering - Cum Laude Miami Dade College Miami, FL 2013 A.A. Engineering - Computer Projects: FPGA Networking Research Current Nallatech 385a Communication Research Current Glove Controlled Drone Design 2 Fall 2017 32-bit ARM Cortex (TI MSP432) used to interpret hand gestures via sensors for drone flight, transmit user intended controls to the drone via RF communication, and detect and display communication errors and react accordingly for safety 32-bit MIPS Emulated Processor Digital Design Spring 2017 Altera Cyclone-III FPGA used to emulate MIPS processor via VHDL Guitar Tuner Design 1 Spring 2017 Microchip PIC18F4620 microcontroller and discrete analog components used to determine correct input frequency via analog filtering and DSP techniques Employment: University of Florida - ARC Lab Gainesville, FL Current Research Assistant - FPGA ❖ Research systems integration of Nallatech 385a FPGA card and its components including the Intel Arria 10 FPGA, Intel’s Avalon bus, and PCIe communication via Linux ❖ Create partial reconfiguration region for Nallatech 385a for general use in research lab ❖ Research cloud and network implementations of FPGAs Intel San Jose, CA Summer 2019/2020 Programmable Solutions Group Intern ❖ Assisted with Agilex Linux driver development ❖ ITU G spec testing compliance and characterization for IEEE 1588 on Intel N3000 ❖ Developed automated tools for ITU network timestamp testing ❖ System validation of IEEE 1588 for Wireless 5G technology and communicated need and data across many teams ❖ Developed Arduino workshop for hobbyists Alexis Rodriguez Jr. -

Altium's Journey and Its Vision of Industry Transformation

A Winning Strategy for Value-Creation ALTIUM’S JOURNEY AND ITS VISION OF INDUSTRY TRANSFORMATION 18 June 2021 Agenda 1 Altium’s Journey of Transformation 2 Uniqueness of Altium in the Engineering Software Ecosystem 3 Altium’s Confidence in its Ability to Execute 4 Our Flight Path to Dominance Outstanding Value-Creation Track-Record Over Time ALU Set in 2019 and confident of achieving $500M * Stock Price Revenue Target Set in 2016 and fell short with COVID, $189M ** Delivering Value for our Shareholders $200M is a Hallmark of Altium… Revenue Target • A history of setting and over-achieving Set in 2014 and overachieved, $110M $100M aggressive long-term financial targets Revenue Target • Eight consecutive years of double-digit revenue growth & expanding margin ? • Focused execution with the “ingenuity of and” A$41.60 delivering strong operating leverage A$10.15 • Transparency for stakeholders and all-in reporting (no capitalization of R&D expenses) A$4.36 • Value creation at every stage from leadership to dominance to industry transformation A$0.76 Performing Leading Dominating Transforming 2012 2015 2017 2020 2025 * The target revenue of $500M may include 10-20% from future acquisitions. 3 ** Three months out analysts’ consensus pointed to a revenue target of $208M for FY2020 Pursuing Dominance and Transformation from a Position of Strength Financial Altium Designer Altium 365 Performance Dominance Adoption Altium is the fastest growing EDA company Altium Designer is the most widespread The world’s first digital platform for with 8 consecutive -

Getting Started with PCB Design

Getting Started with PCB Design This introductory tutorial is designed to give you an overview Summary of how to create a schematic, update the design information to a PCB and generate manufacturing output files. It also Tutorial investigates the concept of projects and integrated libraries TU0117 (v2.0) February 12, 2008 and provides a summary of the 3D PCB environment and creating 3D bodies for component footprints. Welcome to the world of Altium Designer – a complete electronic product development environment. This tutorial will get you started with creating a PCB project based on an astable multivibrator design. If you are new to Altium Designer then you might like read the guide Welcome to the Altium Designer Environment for an explanation of the interface, information on how to use panels and managing design documents. Creating a New PCB Project A project in Altium Designer consists of links to all documents and setups related to a design. A project file, eg. xxx.PrjPCB, is an ASCII text file that lists which documents are in the project and related output setups, eg. for printing and CAM. Documents that are not associated with a project are called ‘free documents’. Links to schematic sheets and a target output, eg. PCB, FPGA, embedded (VHDL) or library package, are added to a project. Once the project is compiled, design verification, synchronization and comparison can take place. Any changes to the original schematics or PCB, for example, are updated in the project when compiled. The process of creating a new project is the same for all project types. -

A Credit Card Sized Ethernet Arduino Compatable Controller Board by Drj113 on July 4, 2010

Home Sign Up! Browse Community Submit All Art Craft Food Games Green Home Kids Life Music Offbeat Outdoors Pets Photo Ride Science Tech A credit card sized Ethernet Arduino compatable controller board by drj113 on July 4, 2010 Table of Contents A credit card sized Ethernet Arduino compatable controller board . 1 Intro: A credit card sized Ethernet Arduino compatable controller board . 2 Step 1: Here is the Schematic Diagram . 2 File Downloads . 3 Step 2: The PCB Layout . 3 File Downloads . 3 Step 3: Soldering the Components . 4 Step 4: Programming the Firmware . 5 File Downloads . 5 Step 5: But what does it do???? . 6 Step 6: Parts LIst . 6 Step 7: KiCad Files . 7 File Downloads . 7 Related Instructables . 7 Comments . 7 http://www.instructables.com/id/A-credit-card-sized-Ethernet-Arduino-compatable-co/ Author:drj113 I have a background in digital electronics, and am very interested in computers. I love things that blink, and am in awe of the physics associated with making blue LEDs. Intro: A credit card sized Ethernet Arduino compatable controller board I love the Arduino as a simple and accessible controller platform for many varied projects. A few months ago, a purchased an Ethernet shield for my Arduino controller to work on some projects with a mate of mine - it was a massive hit - for the first time, I could control my projects remotely using simple software. That got me thinking - The Arduino costs about $30AUD, and the Ethernet board cost about $30AUD as well. That is a lot of money - Could I make a simple, dedicated remote controller for much cheaper? Why Yes I could. -

Programming Resume

Thomas John Hastings Programming Resume Introduction: I am a highly motivated self-starter with a passion for problem solving. As the owner of a thriving entertainment agency, Big Top Entertainment, I used coding as a way to automate and improve our business processes. I also designed, built and programmed my own unique performance equipment. Since the pandemic and recurring lockdowns have put live entertainment on hold, I have repurposed my passion for programming into a full time focus. I am looking for a challenge, to be involved in building something, learning new technology and sharing the knowledge I have gained from my own projects. Programming – languages and frameworks: Processing I have extensive knowledge of this Java-based creative programming language. The great thing about Processing is the way you can deploy to Desktop, Mobile, and Cloud with only a few modifications to the same code base. Android (Java) I have seven Android apps published to the Google Play Store, five of which are written in Java. I have developed many more for personal use, including the most recent, CoronaVirusSA, an open source app which graphs reliable stats on the COVID-19 outbreak in South Africa. JavaScript Anyone developing for the web needs to know JavaScript. I am familiar with the Flask back end with Jinja, Bootstrap, JQuery, as well as the excellent Tabulator library for tables. Currently (2020/21) my free time is spent on a couple of entertainment related side projects using this stack. Linux I have been using Ubuntu as my main computing system for over 10 years, both in the cloud (DigitalOcean) and on my Laptop. -

Beyond Schematic Capture Meaningful Abstractions for Better Electronics Design Tools

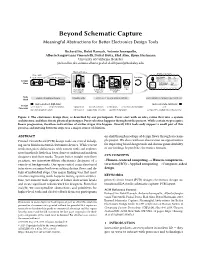

Beyond Schematic Capture Meaningful Abstractions for Better Electronics Design Tools Richard Lin, Rohit Ramesh, Antonio Iannopollo, Alberto Sangiovanni Vincentelli, Prabal Dutta, Elad Alon, Björn Hartmann University of California, Berkeley {richard.lin,rkr,antonio,alberto,prabal,elad,bjoern}@berkeley.edu Physical Device Parts Selection Ideas and ATmega Part Number Size Vf +3.3v Iteration Requirements System Architecture OVLFY3C7 5mm 2 V D0 APG1005SYC-T 0402 2.05 V Button J1 Design Micro- D1 5988140107F 0805 2 V D1 controller - or - ... SW1 Part Number Core LED Flow R1 U1 R2 ATmega32u4 AVR GND Micro- controller LPC1549 ARM CM3 Final FE310-G000 RV32IMAC Hand-built Schematic Prototype PCB Prototypes Capture PCB Tools paper, drawing software breadboards EDA suites: Altium, EAGLE, KiCAD parts libraries, catalogs, spreadsheets Used more abstract, high-level more concrete, low-level Design user stories implementation exploration documentation verification cost, manufacturability cost Concerns functional specification verification supporting circuitry system integration component availability and sourcing Figure 1: The electronics design flow, as described by our participants. Users start with an idea, refine that intoasystem architecture, and then iterate physical prototypes. Parts selection happens throughout the process. While certain steps require linear progression, iteration and revision of earlier stages also happen. Overall, EDA tools only support a small part of this process, and moving between steps was a major source of friction. ABSTRACT on clickthrough mockups of design flows through an exam- Printed Circuit Board (PCB) design tools are critical in help- ple project. We close with our observation on opportunities ing users build non-trivial electronics devices. While recent for improving board design tools and discuss generalizability work recognizes deficiencies with current tools and explores of our findings beyond the electronics domain. -

Module 11: PCB Design Flow, Transferring a Design and Navigation

Module 11: PCB Design Flow, Transferring a Design and Navigation Module 11: PCB Design Flow, Transferring a Design and Navigation 11.1 PCB design process....................................................................... 11-1 11.2 Transferring design information to the PCB.................................... 11-3 11.2.1 Design synchronization ................................................................................11-3 11.2.2 Resolving synchronization errors .................................................................11-4 11.2.3 Exercise – Transferring the design ..............................................................11-5 11.3 Using the PCB Panel ...................................................................... 11-7 11.3.1 PCB Panel....................................................................................................11-7 11.3.2 PCB Rules and Violations ..........................................................................11-14 11.3.3 Exercise – Browsing a PCB document ......................................................11-15 11.4 Project Navigation and Cross Probing ....................................... 11-16 11.4.1 Compiling the PCB project .........................................................................11-16 11.4.2 Navigating ..................................................................................................11-16 11.4.3 Cross probing from the schematic to the PCB...........................................11-17 11.4.4 Exercise — Navigation and Cross Probing................................................11-18 -

Ecebuntu - an Innovative and Multi-Purpose Educational Operating System for Electrical and Computer Engineering Undergraduate Courses

RESEARCH ARTICLE Electrica 2018; 18(2): 210-217 ECEbuntu - An Innovative and Multi-Purpose Educational Operating System for Electrical and Computer Engineering Undergraduate Courses Bilal Wajid1 , Ali Rıza Ekti2 , Mustafa Kamal AlShawaqfeh3 1Department of Electrical Engineering, University of Engineering and Technology, Lahore, Pakistan 2Department of Electrical-Electronics Engineering, Balıkesir University School of Engineering, Balıkesir, Turkey 3School of Electrical Engineering and Information Technology, German Jordanian University, Amman, Jordan Cite this article as: B. Wajid, A. R. Ekti, M. K. AlShawaqfeh, “ECEbuntu - An Innovative and Multi-Purpose Educational Operating System for Electrical and Computer Engineering Undergraduate Courses”, Electrica, vol. 18, no: 2, pp. 210-217, 2018. ABSTRACT ECEbuntu is a free, easily distributable, customized operating system based on Ubuntu 12.04 long term support (LTS) designed for electrical/electronic and computer engineering (ECE) students. ECEbuntu is aimed at universities and students as it represents a cohesive environment integrating more than 30 pre-installed software and packages all catering to undergraduate coursework offered in ECE and Computer Science (CS) programs. ECEbuntu supports a wide range of tools for programming, circuit analysis, printed circuit board design, mathematical and numerical analysis, network analysis, and RF and microwave transmitter design. ECEbuntu is free and effective alternative to the existing costly and copyrighted software packages. ECEbuntu attempts