Hardware Description Language Modelling and Synthesis of Superconducting Digital Circuits

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Amateur Radio Software Distributed with (X)Ubuntu LTS Serge Stroobandt, ON4AA

Amateur Radio Software Distributed with (X)Ubuntu LTS Serge Stroobandt, ON4AA Copyright 2014–2018, licensed under Creative Commons BY-NC-SA Introduction Amateur radio (also called “ham radio”), is a technical hobby Many ham radio stations are highly integrated with computers. Radios are interfaced with com- puters to aid with contact logging, propagation prediction, station spotting, antenna steering, signal (de)modulation and filtering. For many years, amateur radio software has been a bastion of Windows™ ap- plications developed by However, with the advent of the Rasperry Pi, amateur radio hobbyists are slowly but surely discovering GNU/Linux. Most of the software for GNU/Linux is available through package repositories. Such package repositories come by default with the GNU/Linux distribution of your choice. Package management systems offer many benefits in the form of security (you know what you are getting from whom) and ease-of-use (packages are upgraded automatically). No longer does one need to wander the back corners of the internet to find wne or updated software, exposing oneself to the risk of catching a computer virus. A number of GNU/Linux distributions offer freely installable ham-related packages under the “Amateur Radio” section of their main repository. The largest collection of ham radio packages is offeredy b OpenSuse and De- bian-derived distributions like Xubuntu LTS and Linux Mint, to name but a few. Arch Linux may also have whole bunch of ham related software in the Arch User Repository (AUR). 1 Synaptic One way to find and tallins ham radio packages on Debian-derived distros is by using the Synaptic graphical package manager (see Figure 1). -

The Toastboard: Ubiquitous Instrumentation and Automated Checking of Breadboarded Circuits

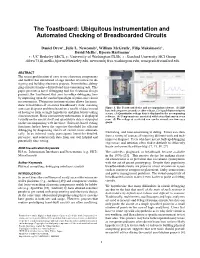

The Toastboard: Ubiquitous Instrumentation and Automated Checking of Breadboarded Circuits Daniel Drew†, Julie L. Newcomb‡, William McGrath?, Filip Maksimovic†, David Mellis†, Bjoern Hartmann† †: UC Berkeley EECS, ‡: University of Washington PLSE, ? : Stanford University HCI Group ddrew73,fil,mellis,[email protected], [email protected], [email protected] ABSTRACT The recent proliferation of easy to use electronic components and toolkits has introduced a large number of novices to de- signing and building electronic projects. Nevertheless, debug- ging circuits remains a difficult and time-consuming task. This paper presents a novel debugging tool for electronic design projects, the Toastboard, that aims to reduce debugging time by improving upon the standard paradigm of point-wise circuit measurements. Ubiquitous instrumentation allows for imme- diate visualization of an entire breadboard’s state, meaning users can diagnose problems based on a wealth of data instead Figure 1. The Toastboard device and accompanying software. (1) LED bars indicate power, ground, or other voltage. (2) A push button triggers of having to form a single hypothesis and plan before taking a scan. (3) Quantitative voltage data is displayed in the accompanying a measurement. Basic connectivity information is displayed software. (4) Components are associated with testers that run on every visually on the circuit itself and quantitative data is displayed scan. (5) The voltage at a selected row can be viewed over time as a on the accompanying web interface. Software-based testing graph. functions further lower the expertise threshold for efficient debugging by diagnosing classes of circuit errors automati- cally. In an informal study, participants found the detailed, frustrating, and time-consuming to debug. -

Development of Systemc Modules from HDL for System-On-Chip Applications

University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange Masters Theses Graduate School 8-2004 Development of SystemC Modules from HDL for System-on-Chip Applications Siddhartha Devalapalli University of Tennessee - Knoxville Follow this and additional works at: https://trace.tennessee.edu/utk_gradthes Part of the Electrical and Computer Engineering Commons Recommended Citation Devalapalli, Siddhartha, "Development of SystemC Modules from HDL for System-on-Chip Applications. " Master's Thesis, University of Tennessee, 2004. https://trace.tennessee.edu/utk_gradthes/2119 This Thesis is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. To the Graduate Council: I am submitting herewith a thesis written by Siddhartha Devalapalli entitled "Development of SystemC Modules from HDL for System-on-Chip Applications." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the equirr ements for the degree of Master of Science, with a major in Electrical Engineering. Dr. Donald W. Bouldin, Major Professor We have read this thesis and recommend its acceptance: Dr. Gregory D. Peterson, Dr. Chandra Tan Accepted for the Council: Carolyn R. Hodges Vice Provost and Dean of the Graduate School (Original signatures are on file with official studentecor r ds.) To the Graduate Council: I am submitting herewith a thesis written by Siddhartha Devalapalli entitled "Development of SystemC Modules from HDL for System-on-Chip Applications". -

A Fedora Electronic Lab Presentation

Chitlesh GOORAH Design & Verification Club Bristol 2010 FUDConBrussels 2007 - [email protected] [ Free Electronic Lab ] (formerly Fedora Electronic Lab) An opensource Design and Simulation platform for Micro-Electronics A one-stop linux distribution for hardware design Marketing means for opensource EDA developers (Networking) From SPEC, Model, Frontend Design, Backend, Development boards to embedded software. FUDConBrussels 2007 - [email protected] Electronic Designers Problems Approx. 6 month design development cycle Tackling Design Complexity Lower Power, Lower Cost and Smaller Space Semiconductor Industry's neck squeezed in 2008 Management (digital/analog) IP Portfolio FUDConBrussels 2007 - [email protected] FUDConBrussels 2007 - [email protected] A basic Design Flow FUDConBrussels 2007 - [email protected] TIP: Use verilator to lint your verilog files. Most of the Veripool tools are available under FEL. They are in sync with Wilson Snyder's releases. FUDConBrussels 2007 - [email protected] FUDConBrussels 2007 - [email protected] GTKWaveGTKWave Don'tDon't forgetforget itsits TCLTCL backendbackend WidelyWidely usedused togethertogether withwith SystemCSystemC FUDConBrussels 2007 - [email protected] Tools Standard Cell libraries FUDConBrussels 2007 - [email protected] BackendBackend designdesign Open Circuit Design, Electric FUDConBrussels 2007 - [email protected], Toped gEDA/gafgEDA/gaf Well known and famous. A very good example of opensource -

Simulator for the RV32-Versat Architecture

Simulator for the RV32-Versat Architecture João César Martins Moutoso Ratinho Thesis to obtain the Master of Science Degree in Electrical and Computer Engineering Supervisor(s): Prof. José João Henriques Teixeira de Sousa Examination Committee Chairperson: Prof. Francisco André Corrêa Alegria Supervisor: Prof. José João Henriques Teixeira de Sousa Member of the Committee: Prof. Marcelino Bicho dos Santos November 2019 ii Declaration I declare that this document is an original work of my own authorship and that it fulfills all the require- ments of the Code of Conduct and Good Practices of the Universidade de Lisboa. iii iv Acknowledgments I want to thank my supervisor, Professor Jose´ Teixeira de Sousa, for the opportunity to develop this work and for his guidance and support during that process. His help was fundamental to overcome the multiple obstacles that I faced during this work. I also want to acknowledge Professor Horacio´ Neto for providing a simple Convolutional Neural Net- work application, used as a basis for the application developed for the RV32-Versat architecture. A special acknowledgement goes to my friends, for their continuous support, and Valter,´ that is developing a multi-layer architecture for RV32-Versat. When everything seemed to be doomed he always had a miraculous solution. Finally, I want to express my sincere gratitude to my family for giving me all the support and encour- agement that I needed throughout my years of study and through the process of researching and writing this thesis. They are also part of this work. Thank you. v vi Resumo Esta tese apresenta um novo ambiente de simulac¸ao˜ para a arquitectura RV32-Versat baseado na ferramenta de simulac¸ao˜ Verilator. -

Electronic and Electromechanical Prototyping

Electronic and electromechanical prototyping Introduction - ECAD Corso LM ‘Materiali Intelligenti e Biomimetici’ – Prof. A. Ahluwalia 4/05/2017 [email protected] After Breadboards: Matrix Boards We use breadboards for quick construction, Matrix Boards for laying out a project so it can be copied to make a Printed Circuit Board. This is a prototyping board, with copper pads in a matrix layout. You solder the components in place, and then simply cut pieces of wire, and solder them to make the circuit Printed Circuit Board The PCB is the physical board that holds and connects all of the electronic components. The circuits are formed by a thin layer of conducting material deposited, or "printed," on the surface of an insulating board known as the substrate. Individual electronic components are placed on the surface of the substrate and soldered to the interconnecting circuits. ECAD Electronic computer-aided design (ECAD) or Electronic design automation (EDA) is a category of software tools for designing electronic systems such as integrated circuits and printed circuit boards. The tools work together in a design flow that chip designers use to design and analyze entire semiconductor chips. Before EDA, integrated circuits were designed by hand and manually laid out. By the mid-1970s, developers started to automate the design along with the drafting. The first placement and routing tools were developed. Printed Circuit Board Design PCB ECAD Software (Ex. Eagle): PCB design in EAGLE is a two-step process. First you design your schematic, then you lay out a PCB based on that schematic. PCB Design (2) Your circuit design software will allow you to output the PCB layout in a format called Gerber with one file for each PCB layer (copper layers, solder mask, legend or silk) to allow manufacturing. -

Metadefender Core V4.12.2

MetaDefender Core v4.12.2 © 2018 OPSWAT, Inc. All rights reserved. OPSWAT®, MetadefenderTM and the OPSWAT logo are trademarks of OPSWAT, Inc. All other trademarks, trade names, service marks, service names, and images mentioned and/or used herein belong to their respective owners. Table of Contents About This Guide 13 Key Features of Metadefender Core 14 1. Quick Start with Metadefender Core 15 1.1. Installation 15 Operating system invariant initial steps 15 Basic setup 16 1.1.1. Configuration wizard 16 1.2. License Activation 21 1.3. Scan Files with Metadefender Core 21 2. Installing or Upgrading Metadefender Core 22 2.1. Recommended System Requirements 22 System Requirements For Server 22 Browser Requirements for the Metadefender Core Management Console 24 2.2. Installing Metadefender 25 Installation 25 Installation notes 25 2.2.1. Installing Metadefender Core using command line 26 2.2.2. Installing Metadefender Core using the Install Wizard 27 2.3. Upgrading MetaDefender Core 27 Upgrading from MetaDefender Core 3.x 27 Upgrading from MetaDefender Core 4.x 28 2.4. Metadefender Core Licensing 28 2.4.1. Activating Metadefender Licenses 28 2.4.2. Checking Your Metadefender Core License 35 2.5. Performance and Load Estimation 36 What to know before reading the results: Some factors that affect performance 36 How test results are calculated 37 Test Reports 37 Performance Report - Multi-Scanning On Linux 37 Performance Report - Multi-Scanning On Windows 41 2.6. Special installation options 46 Use RAMDISK for the tempdirectory 46 3. Configuring Metadefender Core 50 3.1. Management Console 50 3.2. -

Circuit Design and Analysis Temel Elektrik Mühendisli Ği, Cilt 1 , Fitzgerald

Course Plan Ankara University Credit: 4 ECTS Engineering Faculty Class: Lecture: 3 hours Department of Engineering Physics Problem Hours: 0 Lab: 0 PEN207 Class Hours: Monday 09:30-12:15 (3 hours) CIRCUIT DESIGN AND Classroom: Seminar Hall (Seminer Salonu) ANALYSIS Office Hours: Friday 11:00-12:00 (Circuit Theory) Attendance: Mandatory Exams: Midterm (one midterm exam) % 30 Prof. Dr. Hüseyin Sarı Final Exam % 80 Passing Grade: 60 (C3) or higher 3 Course Materials and Textbook(s) Ankara University Engineering Faculty, Lecture notes (Ppoint): Dept. of Engineering Physics huseyinsari.net.tr Desler Circuit Design & Analysis (http://huseyinsari.net.tr/ders-pen207.htm) 2019 Fall Main book: PEN207 Circuit Design and Analysis Temel Elektrik Mühendisli ği, Cilt 1 , Fitzgerald. A. E. Higginbotham D. E.,Grabel A. Instructor : Prof. Dr. Hüseyin Sarı (Editor: Prof. Dr. Kerim Kıymaç, 3.Edition) A.U. Engineering Faculty, Dept. of Eng. Physics Office: Department of Eng. Phy., B-Block, Room:105 E-mail: [email protected] ● [email protected] web: www.huseyinsari.net.tr Phone: (312) 203 3424 (office) ● 536 295 3555 (cell) 2 4 PEN207-Circuit Design & Analysis:Introduction 1 Textbooks Textbooks-Turkish Recommended Textbooks-1: Recommended (Turkish)Textbooks-3: Introductory Electric Circuits Schaum's Outline of Basic Circuit Elektrik Devreleri Elektrik Devreleri Elektrik Devreleri-I Circuit Analysis James W. Nilsson, James W. Nilsson, (Ders Kitabı ) - Teori ve Çözümlü Robert L. Boylestad Susan Riedel Analysis, 2nd Edition John O'Malley Susan Riedel Problem Çözümleri Örnekler Pearson Int. Edition 6th Ed. Palme Yayınevi (In library) (In library) (In library) Turgut İkiz , Ali Bekir Yıldız Papatya Bilim Yayınları Volga Yayıncılık 5 7 Textbooks Textbooks-Turkish Recommended Textbooks-2: Recommended (Turkish)Textbooks-4: Introduction to Electrical Schaum's Outline of Do ğru Akım Devreleri ve Electric Circuits Engineering: 3000 Solved Problem Çözümleri Richard C. -

Elementary Filter Circuits

Modular Electronics Learning (ModEL) project * SPICE ckt v1 1 0 dc 12 v2 2 1 dc 15 r1 2 3 4700 r2 3 0 7100 .dc v1 12 12 1 .print dc v(2,3) .print dc i(v2) .end V = I R Elementary Filter Circuits c 2018-2021 by Tony R. Kuphaldt – under the terms and conditions of the Creative Commons Attribution 4.0 International Public License Last update = 13 September 2021 This is a copyrighted work, but licensed under the Creative Commons Attribution 4.0 International Public License. A copy of this license is found in the last Appendix of this document. Alternatively, you may visit http://creativecommons.org/licenses/by/4.0/ or send a letter to Creative Commons: 171 Second Street, Suite 300, San Francisco, California, 94105, USA. The terms and conditions of this license allow for free copying, distribution, and/or modification of all licensed works by the general public. ii Contents 1 Introduction 3 2 Case Tutorial 5 2.1 Example: RC filter design ................................. 6 3 Tutorial 9 3.1 Signal separation ...................................... 9 3.2 Reactive filtering ...................................... 10 3.3 Bode plots .......................................... 14 3.4 LC resonant filters ..................................... 15 3.5 Roll-off ........................................... 17 3.6 Mechanical-electrical filters ................................ 18 3.7 Summary .......................................... 20 4 Historical References 25 4.1 Wave screens ........................................ 26 5 Derivations and Technical References 29 5.1 Decibels ........................................... 30 6 Programming References 41 6.1 Programming in C++ ................................... 42 6.2 Programming in Python .................................. 46 6.3 Modeling low-pass filters using C++ ........................... 51 7 Questions 63 7.1 Conceptual reasoning ................................... -

Getting Started in High Performance Electronic Design

Getting started in high performance electronic design Wojtek Skulski Department of Physics and Astronomy University of Rochester Rochester, NY 14627-0171 skulski _at_ pas.rochester.edu First presented May/23/2002 Updated for the web July/03/2004 Wojtek Skulski May/2002 Department of Physics and Astronomy, University of Rochester Getting started with High performance electronic design • 3-hour class • Designing high performance surface mount and multilayer boards. • What tools and resources are available? • How to get my design manufactured and assembled? • Board design with OrCAD Capture and Layout. • When and where: • Thursday, May/23/2002, 9-12am, Bausch&Lomb room 106 (1st floor). • Slides updated for the web July/03/2004. • Reserve your handout. • Send e-mail to [email protected] if you plan to attend. • Walk-ins are invited, but there may be no handouts if you do not register. • See you there! Wojtek Skulski May/2002 Department of Physics and Astronomy, University of Rochester The goal and outline of this class • Goal: • Describe the tools available to us for designing high performance electronic instruments. • Outline • Why do we need surface mount and multilayer boards? • What tools and resources are available? • How to get my PCB manufactured? • How to get my board assembled? • Designing with OrCAD Capture and OrCAD Layout. • The audience • You know the basics of electronics. • … and you need to get going quickly with your design. Wojtek Skulski May/2002 Department of Physics and Astronomy, University of Rochester Disclaimer • I am describing tools and methods which work for me. • I do not claim that this information is complete. -

Linuxvilag-66.Pdf 8791KB 11 2012-05-28 10:27:18

Magazin Hírek Java telefon másképp Huszonegyedik századi autótolvajok Samsung okostelefon Linuxszal Magyarországon még nem jellemzõ, Kínában már kapható de tõlünk nyugatabbra már nem tol- a Samsung SCH-i819 mo- vajkulccsal vagy feszítõvassal, hanem biltelefonja, amely Prizm laptoppal járnak az autótolvajok. 2.5-ös Linuxot futtat. Ot- Mindezt azt teszi lehetõvé, hogy tani nyaralás esetén nyu- a gyújtás, a riasztó és az ajtózárak is godtan vásárolhatunk távirányíthatóak, így egy megfelelõen belõle, hiszen a CDMA felszerelt laptoppal is irányíthatóak 800 MHz-e mellett az ezek a rendszerek. európai 900/1800 MHz-et http://www.leftlanenews.com/2006/ is támogatja. A kommunikációt egy 05/03/gone-in-20-minutes-using- Qualcomm MSM6300-as áramkör bo- laptops-to-steal-cars/ nyolítja, míg az alkalmazások egy 416 MHz-es Intel PXA270-es processzoron A Lucent Technologies és a SUN Elephants Dream futnak. A készülék Class 10-es GPRS elkészítette a Jasper S20-at, ami adatátvitelre képes, illetve tartalmaz alapvetõen más koncepcióval GPS (globális helymeghatározó) vevõt © Kiskapu Kft. Minden jog fenntartva használja a Java-t, mint a mostani is. Az eszköz 64 megabájt SDRAM-ot és telefonok. Joggal kérdezheti a kedves 128 megabájt nem felejtõ flash memóri- Olvasó, hogy megéri-e, van-e hely át kapott, de micro-SD memóriakártyá- a jelenlegi Symbian, Windows Mobile val ezt tovább bõvíthetjük. A kijelzõje és Linux trió mellett. A jelenlegi 2.4 hüvelykes, felbontása pedig „csak” telefonoknál kétféleképpen futhat 240x320 képpont 65 ezer színnel. egy program: natív vagy Java mód- Május 19-én elérhetõvé tette az Orange Természetesen a trendeknek megfele- ban. A Java mód ott szükségessé Open Movie Project elsõ rövidfilmjét lõen nem maradt ki a 2 megapixeles tesz pár olyan szintet, amely Creative Commons jogállással. -

A Credit Card Sized Ethernet Arduino Compatable Controller Board by Drj113 on July 4, 2010

Home Sign Up! Browse Community Submit All Art Craft Food Games Green Home Kids Life Music Offbeat Outdoors Pets Photo Ride Science Tech A credit card sized Ethernet Arduino compatable controller board by drj113 on July 4, 2010 Table of Contents A credit card sized Ethernet Arduino compatable controller board . 1 Intro: A credit card sized Ethernet Arduino compatable controller board . 2 Step 1: Here is the Schematic Diagram . 2 File Downloads . 3 Step 2: The PCB Layout . 3 File Downloads . 3 Step 3: Soldering the Components . 4 Step 4: Programming the Firmware . 5 File Downloads . 5 Step 5: But what does it do???? . 6 Step 6: Parts LIst . 6 Step 7: KiCad Files . 7 File Downloads . 7 Related Instructables . 7 Comments . 7 http://www.instructables.com/id/A-credit-card-sized-Ethernet-Arduino-compatable-co/ Author:drj113 I have a background in digital electronics, and am very interested in computers. I love things that blink, and am in awe of the physics associated with making blue LEDs. Intro: A credit card sized Ethernet Arduino compatable controller board I love the Arduino as a simple and accessible controller platform for many varied projects. A few months ago, a purchased an Ethernet shield for my Arduino controller to work on some projects with a mate of mine - it was a massive hit - for the first time, I could control my projects remotely using simple software. That got me thinking - The Arduino costs about $30AUD, and the Ethernet board cost about $30AUD as well. That is a lot of money - Could I make a simple, dedicated remote controller for much cheaper? Why Yes I could.