Vxworks ® Programmer’S Guide

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Wind River Vxworks Platforms 3.8

Wind River VxWorks Platforms 3.8 The market for secure, intelligent, Table of Contents Build System ................................ 24 connected devices is constantly expand- Command-Line Project Platforms Available in ing. Embedded devices are becoming and Build System .......................... 24 VxWorks Edition .................................2 more complex to meet market demands. Workbench Debugger .................. 24 New in VxWorks Platforms 3.8 ............2 Internet connectivity allows new levels of VxWorks Simulator ....................... 24 remote management but also calls for VxWorks Platforms Features ...............3 Workbench VxWorks Source increased levels of security. VxWorks Real-Time Operating Build Configuration ...................... 25 System ...........................................3 More powerful processors are being VxWorks 6.x Kernel Compatibility .............................3 considered to drive intelligence and Configurator ................................. 25 higher functionality into devices. Because State-of-the-Art Memory Host Shell ..................................... 25 Protection ..................................3 real-time and performance requirements Kernel Shell .................................. 25 are nonnegotiable, manufacturers are VxBus Framework ......................4 Run-Time Analysis Tools ............... 26 cautious about incorporating new Core Dump File Generation technologies into proven systems. To and Analysis ...............................4 System Viewer ........................ -

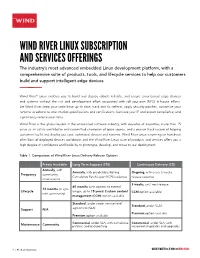

Wind River Linux Subscription and Services Offerings

WIND RIVER LINUX SUBSCRIPTION AND SERVICES OFFERINGS The industry’s most advanced embedded Linux development platform, with a comprehensive suite of products, tools, and lifecycle services to help our customers build and support intelligent edge devices Wind River® Linux enables you to build and deploy robust, reliable, and secure Linux-based edge devices and systems without the risk and development effort associated with roll-your-own (RYO) in-house efforts. Let Wind River keep your code base up to date, track and fix defects, apply security patches, customize your runtime to adhere to strict market specifications and certifications, facilitate your IP and export compliance, and significantly reduce your costs. Wind River is the global leader in the embedded software industry, with decades of expertise, more than 15 years as an active contributor and committed champion of open source, and a proven track record of helping customers build and deploy use case–optimized devices and systems. Wind River Linux is running on hundreds of millions of deployed devices worldwide, and the Wind River Linux suite of products and services offers you a high degree of confidence and flexibility to prototype, develop, and move to real deployment. Table 1. Comparison of Wind River Linux Delivery Release Options Freely Available Long Term Support (LTS) Continuous Delivery (CD) Annually, with Annually, with predictable Rolling Ongoing, with every-3-weeks Frequency community Cumulative Patch Layer (RCPL) cadence release cadence maintenance 3 weeks, until next -

Comparison of Contemporary Real Time Operating Systems

ISSN (Online) 2278-1021 IJARCCE ISSN (Print) 2319 5940 International Journal of Advanced Research in Computer and Communication Engineering Vol. 4, Issue 11, November 2015 Comparison of Contemporary Real Time Operating Systems Mr. Sagar Jape1, Mr. Mihir Kulkarni2, Prof.Dipti Pawade3 Student, Bachelors of Engineering, Department of Information Technology, K J Somaiya College of Engineering, Mumbai1,2 Assistant Professor, Department of Information Technology, K J Somaiya College of Engineering, Mumbai3 Abstract: With the advancement in embedded area, importance of real time operating system (RTOS) has been increased to greater extent. Now days for every embedded application low latency, efficient memory utilization and effective scheduling techniques are the basic requirements. Thus in this paper we have attempted to compare some of the real time operating systems. The systems (viz. VxWorks, QNX, Ecos, RTLinux, Windows CE and FreeRTOS) have been selected according to the highest user base criterion. We enlist the peculiar features of the systems with respect to the parameters like scheduling policies, licensing, memory management techniques, etc. and further, compare the selected systems over these parameters. Our effort to formulate the often confused, complex and contradictory pieces of information on contemporary RTOSs into simple, analytical organized structure will provide decisive insights to the reader on the selection process of an RTOS as per his requirements. Keywords:RTOS, VxWorks, QNX, eCOS, RTLinux,Windows CE, FreeRTOS I. INTRODUCTION An operating system (OS) is a set of software that handles designed known as Real Time Operating System (RTOS). computer hardware. Basically it acts as an interface The motive behind RTOS development is to process data between user program and computer hardware. -

Evidence Company Description …And Future Challenges

1 Evidence Company description …and future challenges Paolo Gai, [email protected] IWES Workshop Pisa, 21 September 2016 2 The company Founded in 2002 as spin-off company of the Real-Time Systems Lab at Scuola Superiore S.Anna ~20 qualified people with an average age of 34 years 10+ years of experience in academic and industrial projects One third of the company has a PhD degree Our Mission : design and development software for small electronic devices 3 The company Partner in several European and Italian research projects (FP6, FP7, Ind.2015, Reg. Tuscany, H2020) Founded SSG Srl in November 2011 http://www.ssginnovation.com/ - (link to SSG slides) Evidence won the first prize at Start Cup Pisa 2005 March 12, 2007 - selected by ”Corriere della Sera ” as one of the most innovative Italian young entrepreneurs 4 (some) customers OSEK, microcontrollers, schedulability analysis, code generation Linux, SW devel. Listed as 3 rd party 5 products and services RTOS , Firmware, Embedded Linux Model-based design • OSEK/VDX, • Matlab/Simulink/Stateflow AUTOSAR, device drivers • Embedded Linux: 8 Yrs experience • National Instruments custom BSPs, GCC, U-Boot, LabView Kernel drivers • Initial developers of the • E4Coder toolset for code SCHED_DEADLINE patch generation • QEMU and emulators • UML/SYSML/Ecore/ Application Development Eclipse/Acceleo 6 Something about ERIKA Enterprise http://erika.tuxfamily.org • ERIKA Enterprise is an RTOS OSEK/VDX certified • ERIKA Enterprise implements an API inspired to a subset of the AUTOSAR API • open-source license -

RT-ROS: a Real-Time ROS Architecture on Multi-Core Processors

Future Generation Computer Systems 56 (2016) 171–178 Contents lists available at ScienceDirect Future Generation Computer Systems journal homepage: www.elsevier.com/locate/fgcs RT-ROS: A real-time ROS architecture on multi-core processors Hongxing Wei a,1, Zhenzhou Shao b, Zhen Huang a, Renhai Chen d, Yong Guan b, Jindong Tan c,1, Zili Shao d,∗,1 a School of Mechanical Engineering and Automation, Beihang University, Beijing, 100191, PR China b College of Information Engineering, Capital Normal University, Beijing, 100048, PR China c Department of Mechanical, Aerospace, and Biomedical Engineering, The University of Tennessee, Knoxville, TN, 37996-2110, USA d Department of Computing, The Hong Kong Polytechnic University, Hong Kong, China article info a b s t r a c t Article history: ROS, an open-source robot operating system, is widely used and rapidly developed in the robotics Received 6 February 2015 community. However, running on Linux, ROS does not provide real-time guarantees, while real-time tasks Received in revised form are required in many robot applications such as robot motion control. This paper for the first time presents 20 April 2015 a real-time ROS architecture called RT-RTOS on multi-core processors. RT-ROS provides an integrated Accepted 12 May 2015 real-time/non-real-time task execution environment so real-time and non-real-time ROS nodes can be Available online 9 June 2015 separately run on a real-time OS and Linux, respectively, with different processor cores. In such a way, real-time tasks can be supported by real-time ROS nodes on a real-time OS, while non-real-time ROS nodes Keywords: Real-time operating systems on Linux can provide other functions of ROS. -

Vxworks - Real Time Operating System

VxWorks - Real Time Operating System General Purpose Platform, VxWorks Edition, is a complete, flexible, optimized COTS development and run-time platform that works out of the box and across the enterprise. The platform provides a powerful, scalable development environment built on open standards and industry-leading tools; the industry’s most trusted commercial-grade RTOS; and tightly integrated run-time technologies. This proven technology package comes wrapped in a 20+-year track record, an exceptional ecosystem of hardware and software partners, and the industry’s most comprehensive support organization. General Purpose Platform is an optimized develop and run solution for a range of devices, from A&D applications to networking and consumer electronics, robotics and industrial applications, precision medical instruments, and car navigation and telematics systems. The platform provides a robust foundation for companies that need to leverage their investment in proprietary intellectual property. It has been deployed successfully in millions of devices worldwide. General Purpose Platform is based on the world’s most widely adopted RTOS. Built on a highly scalable, deterministic, hard real-time kernel, VxWorks enables companies to scale and optimize their run-time environment using only the specific technologies required by their device. From the smallest footprint requirement to the highest performance level, VxWorks gives developers the flexibility to build their optimal solution quickly and easily while meeting cost, quality, and functionality requirements. VxWorks supports POSIX and industry-standard protocols such as TIPC and IPv6, ensuring maximum code portability and interoperability. VxWorks 6.x is backward compatible with previous releases, so developers can leverage and reuse existing projects, intellectual property, BSPs, and drivers, as well as open-source applications. -

Ece585 Lec2.Pdf

ECE 485/585 Microprocessor System Design Lecture 2: Memory Addressing 8086 Basics and Bus Timing Asynchronous I/O Signaling Zeshan Chishti Electrical and Computer Engineering Dept Maseeh College of Engineering and Computer Science Source: Lecture based on materials provided by Mark F. Basic I/O – Part I ECE 485/585 Outline for next few lectures Simple model of computation Memory Addressing (Alignment, Byte Order) 8088/8086 Bus Asynchronous I/O Signaling Review of Basic I/O How is I/O performed Dedicated/Isolated /Direct I/O Ports Memory Mapped I/O How do we tell when I/O device is ready or command complete? Polling Interrupts How do we transfer data? Programmed I/O DMA ECE 485/585 Simplified Model of a Computer Control Control Data, Address, Memory Data Path Microprocessor Keyboard Mouse [Fetch] Video display [Decode] Printer [Execute] I/O Device Hard disk drive Audio card Ethernet WiFi CD R/W DVD ECE 485/585 Memory Addressing Size of operands Bytes, words, long/double words, quadwords 16-bit half word (Intel: word) 32-bit word (Intel: doubleword, dword) 0x107 64-bit double word (Intel: quadword, qword) 0x106 Note: names are non-standard 0x105 SUN Sparc word is 32-bits, double is 64-bits 0x104 0x103 Alignment 0x102 Can multi-byte operands begin at any byte address? 0x101 Yes: non-aligned 0x100 No: aligned. Low order address bit(s) will be zero ECE 485/585 Memory Operand Alignment …Intel IA speak (i.e. word = 16-bits = 2 bytes) 0x107 0x106 0x105 0x104 0x103 0x102 0x101 0x100 Aligned Unaligned Aligned Unaligned Aligned Unaligned word word Double Double Quad Quad address address word word word word -----0 address address address address -----00 ----000 ECE 485/585 Memory Operand Alignment Why do we care? Unaligned memory references Can cause multiple memory bus cycles for a single operand May also span cache lines Requiring multiple evictions, multiple cache line fills Complicates memory system and cache controller design Some architectures restrict addresses to be aligned Even in architectures without alignment restrictions (e.g. -

OPERATING SYSTEMS.Ai

Introduction Aeroflex Gaisler provides LEON and ERC32 users with a wide range of popular embedded operating systems. Ranging from very small footprint task handlers to full featured Real-Time Operating System (RTOS). A summary of available operating systems and their characteristics is outlined below. VxWorks The VxWorks SPARC port supports LEON3/4 and LEON2. Drivers for standard on-chip peripherals are included. The port supports both non-MMU and MMU systems allowing users to program fast and secure applications. Along with the graphical Eclipse based workbench comes the extensive VxWorks documentation. • MMU and non-MMU system support • SMP support (in 6.7 and later) • Networking support (Ethernet 10/100/1000) • UART, Timer, and interrupt controller support • PCI, SpaceWire, CAN, MIL-STD-1553B, I2C and USB host controller support • Eclipse based Workbench • Commercial license ThreadX The ThreadX SPARC port supports LEON3/4 and its standard on-chip peripherals. ThreadX is an easy to learn and understand advanced pico-kernel real-time operating system designed specifically for deeply embedded applications. ThreadX has a rich set of system services for memory allocation and threading. • Non-MMU system support • Bundled with newlib C library • Support for NetX, and USBX ® • Very small footprint • Commercial license Nucleus Nucleus is a real time operating system which offers a rich set of features in a scalable and configurable manner. • UART, Timer, Interrupt controller, Ethernet (10/100/1000) • TCP offloading and zero copy TCP/IP stack (using GRETH GBIT MAC) • USB 2.0 host controller and function controller driver • Small footprint • Commercial license LynxOS LynxOS is an advanced RTOS suitable for high reliability environments. -

Avaya Aura® Communication Manager Hardware Description and Reference

Avaya Aura® Communication Manager Hardware Description and Reference Release 7.0.1 555-245-207 Issue 2 May 2016 © 2015-2016, Avaya, Inc. Link disclaimer All Rights Reserved. Avaya is not responsible for the contents or reliability of any linked Notice websites referenced within this site or Documentation provided by Avaya. Avaya is not responsible for the accuracy of any information, While reasonable efforts have been made to ensure that the statement or content provided on these sites and does not information in this document is complete and accurate at the time of necessarily endorse the products, services, or information described printing, Avaya assumes no liability for any errors. Avaya reserves or offered within them. Avaya does not guarantee that these links will the right to make changes and corrections to the information in this work all the time and has no control over the availability of the linked document without the obligation to notify any person or organization pages. of such changes. Licenses Warranty THE SOFTWARE LICENSE TERMS AVAILABLE ON THE AVAYA Avaya provides a limited warranty on Avaya hardware and software. WEBSITE, HTTPS://SUPPORT.AVAYA.COM/LICENSEINFO, Refer to your sales agreement to establish the terms of the limited UNDER THE LINK “AVAYA SOFTWARE LICENSE TERMS (Avaya warranty. In addition, Avaya’s standard warranty language, as well as Products)” OR SUCH SUCCESSOR SITE AS DESIGNATED BY information regarding support for this product while under warranty is AVAYA, ARE APPLICABLE TO ANYONE WHO DOWNLOADS, available to Avaya customers and other parties through the Avaya USES AND/OR INSTALLS AVAYA SOFTWARE, PURCHASED Support website: https://support.avaya.com/helpcenter/ FROM AVAYA INC., ANY AVAYA AFFILIATE, OR AN AVAYA getGenericDetails?detailId=C20091120112456651010 under the link CHANNEL PARTNER (AS APPLICABLE) UNDER A COMMERCIAL “Warranty & Product Lifecycle” or such successor site as designated AGREEMENT WITH AVAYA OR AN AVAYA CHANNEL PARTNER. -

Reverse Engineering X86 Processor Microcode

Reverse Engineering x86 Processor Microcode Philipp Koppe, Benjamin Kollenda, Marc Fyrbiak, Christian Kison, Robert Gawlik, Christof Paar, and Thorsten Holz, Ruhr-University Bochum https://www.usenix.org/conference/usenixsecurity17/technical-sessions/presentation/koppe This paper is included in the Proceedings of the 26th USENIX Security Symposium August 16–18, 2017 • Vancouver, BC, Canada ISBN 978-1-931971-40-9 Open access to the Proceedings of the 26th USENIX Security Symposium is sponsored by USENIX Reverse Engineering x86 Processor Microcode Philipp Koppe, Benjamin Kollenda, Marc Fyrbiak, Christian Kison, Robert Gawlik, Christof Paar, and Thorsten Holz Ruhr-Universitat¨ Bochum Abstract hardware modifications [48]. Dedicated hardware units to counter bugs are imperfect [36, 49] and involve non- Microcode is an abstraction layer on top of the phys- negligible hardware costs [8]. The infamous Pentium fdiv ical components of a CPU and present in most general- bug [62] illustrated a clear economic need for field up- purpose CPUs today. In addition to facilitate complex and dates after deployment in order to turn off defective parts vast instruction sets, it also provides an update mechanism and patch erroneous behavior. Note that the implementa- that allows CPUs to be patched in-place without requiring tion of a modern processor involves millions of lines of any special hardware. While it is well-known that CPUs HDL code [55] and verification of functional correctness are regularly updated with this mechanism, very little is for such processors is still an unsolved problem [4, 29]. known about its inner workings given that microcode and the update mechanism are proprietary and have not been Since the 1970s, x86 processor manufacturers have throughly analyzed yet. -

WIND RIVER INTELLIGENT DEVICE PLATFORM XT the Foundation for Building Devices That Connect to the Internet of Things

WIND RIVER INTELLIGENT DEVICE PLATFORM XT The Foundation for Building Devices That Connect to the Internet of Things The opportunities presented by the burgeoning Internet of Things (IoT) may be new, but Wind River® has been providing the intelligence that powers interconnected, automated systems for decades. Wind River Intelligent Device Platform XT is a scalable, sustainable, and secure development environment that simplifies the development, integration, and deployment of IoT gateways. It is based on Wind River industry-leading operating systems, which are standards-compliant and fully tested, as well as Wind River development tools. The platform provides device security, smart connectivity, rich network options, and device management; and it includes ready-to-use components built exclusively for developing IoT gateway applications. Intelligent Device Platform XT provides outstanding software and expertise to fuel the rapid innovation and deployment of safe, secure, and reliable intel- ligent devices through more efficient development cycles, standards-based data connec- tions, and intuitive management tools. CONNECTIVITY TOOLS ZigBee Bluetooth WWAN VPN MQTT Cloud Connector Wi MANAGEMENT nd River Integrated Development Environment T Secure Updates OMA DM, TR-069 Device Authentication Web Interface Application Signing API OpenJDK Lua VM SQLite OSGi To SECURITY ol TCG Standards Role Based Access Control Integrity Monitoring Signed Software ool s WIND RIVER OPERATING ENVIRONMENTS Trusted Secure Boot Wind River Intelligent Device Operating Platform Feature Environment Base Figure 1: Wind River Intelligent Device Platform architecture Product Note INNOVATORS START HERE. WIND RIVER INTELLIGENT DEVICE PLATFORM XT INTEL, MCAFEE, AND WIND RIVER, BETTER TOGETHER Intelligent Device Platform XT is part of Intel® Gateway Solutions for Internet of Things (IoT), a family of platforms that enables companies to seamlessly interconnect indus- trial devices and other systems into a system of systems. -

Computer Architectures an Overview

Computer Architectures An Overview PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 25 Feb 2012 22:35:32 UTC Contents Articles Microarchitecture 1 x86 7 PowerPC 23 IBM POWER 33 MIPS architecture 39 SPARC 57 ARM architecture 65 DEC Alpha 80 AlphaStation 92 AlphaServer 95 Very long instruction word 103 Instruction-level parallelism 107 Explicitly parallel instruction computing 108 References Article Sources and Contributors 111 Image Sources, Licenses and Contributors 113 Article Licenses License 114 Microarchitecture 1 Microarchitecture In computer engineering, microarchitecture (sometimes abbreviated to µarch or uarch), also called computer organization, is the way a given instruction set architecture (ISA) is implemented on a processor. A given ISA may be implemented with different microarchitectures.[1] Implementations might vary due to different goals of a given design or due to shifts in technology.[2] Computer architecture is the combination of microarchitecture and instruction set design. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers, address and data formats among other things. The Intel Core microarchitecture microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALU)s and even larger elements.