Quadrature Amplitude Modulation and Demodulation Techniques

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Lecture 25 Demodulation and the Superheterodyne Receiver EE445-10

EE447 Lecture 6 Lecture 25 Demodulation and the Superheterodyne Receiver EE445-10 HW7;5-4,5-7,5-13a-d,5-23,5-31 Due next Monday, 29th 1 Figure 4–29 Superheterodyne receiver. m(t) 2 Couch, Digital and Analog Communication Systems, Seventh Edition ©2007 Pearson Education, Inc. All rights reserved. 0-13-142492-0 1 EE447 Lecture 6 Synchronous Demodulation s(t) LPF m(t) 2Cos(2πfct) •Only method for DSB-SC, USB-SC, LSB-SC •AM with carrier •Envelope Detection – Input SNR >~10 dB required •Synchronous Detection – (no threshold effect) •Note the 2 on the LO normalizes the output amplitude 3 Figure 4–24 PLL used for coherent detection of AM. 4 Couch, Digital and Analog Communication Systems, Seventh Edition ©2007 Pearson Education, Inc. All rights reserved. 0-13-142492-0 2 EE447 Lecture 6 Envelope Detector C • Ac • (1+ a • m(t)) Where C is a constant C • Ac • a • m(t)) 5 Envelope Detector Distortion Hi Frequency m(t) Slope overload IF Frequency Present in Output signal 6 3 EE447 Lecture 6 Superheterodyne Receiver EE445-09 7 8 4 EE447 Lecture 6 9 Super-Heterodyne AM Receiver 10 5 EE447 Lecture 6 Super-Heterodyne AM Receiver 11 RF Filter • Provides Image Rejection fimage=fLO+fif • Reduces amplitude of interfering signals far from the carrier frequency • Reduces the amount of LO signal that radiates from the Antenna stop 2/22 12 6 EE447 Lecture 6 Figure 4–30 Spectra of signals and transfer function of an RF amplifier in a superheterodyne receiver. 13 Couch, Digital and Analog Communication Systems, Seventh Edition ©2007 Pearson Education, Inc. -

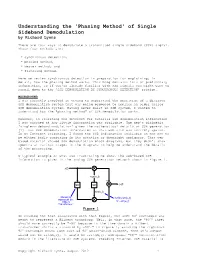

Of Single Sideband Demodulation by Richard Lyons

Understanding the 'Phasing Method' of Single Sideband Demodulation by Richard Lyons There are four ways to demodulate a transmitted single sideband (SSB) signal. Those four methods are: • synchronous detection, • phasing method, • Weaver method, and • filtering method. Here we review synchronous detection in preparation for explaining, in detail, how the phasing method works. This blog contains lots of preliminary information, so if you're already familiar with SSB signals you might want to scroll down to the 'SSB DEMODULATION BY SYNCHRONOUS DETECTION' section. BACKGROUND I was recently involved in trying to understand the operation of a discrete SSB demodulation system that was being proposed to replace an older analog SSB demodulation system. Having never built an SSB system, I wanted to understand how the "phasing method" of SSB demodulation works. However, in searching the Internet for tutorial SSB demodulation information I was shocked at how little information was available. The web's wikipedia 'single-sideband modulation' gives the mathematical details of SSB generation [1]. But SSB demodulation information at that web site was terribly sparse. In my Internet searching, I found the SSB information available on the net to be either badly confusing in its notation or downright ambiguous. That web- based material showed SSB demodulation block diagrams, but they didn't show spectra at various stages in the diagrams to help me understand the details of the processing. A typical example of what was frustrating me about the web-based SSB information is given in the analog SSB generation network shown in Figure 1. x(t) cos(ωct) + 90o 90o y(t) – sin(ωct) Meant to Is this sin(ω t) represent the c Hilbert or –sin(ωct) Transformer. -

An Analysis of a Quadrature Double-Sideband/Frequency Modulated Communication System

Scholars' Mine Masters Theses Student Theses and Dissertations 1970 An analysis of a quadrature double-sideband/frequency modulated communication system Denny Ray Townson Follow this and additional works at: https://scholarsmine.mst.edu/masters_theses Part of the Electrical and Computer Engineering Commons Department: Recommended Citation Townson, Denny Ray, "An analysis of a quadrature double-sideband/frequency modulated communication system" (1970). Masters Theses. 7225. https://scholarsmine.mst.edu/masters_theses/7225 This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact [email protected]. AN ANALYSIS OF A QUADRATURE DOUBLE- SIDEBAND/FREQUENCY MODULATED COMMUNICATION SYSTEM BY DENNY RAY TOWNSON, 1947- A THESIS Presented to the Faculty of the Graduate School of the UNIVERSITY OF MISSOURI - ROLLA In Partial Fulfillment of the Requirements for the Degree MASTER OF SCIENCE IN ELECTRICAL ENGINEERING 1970 ii ABSTRACT A QDSB/FM communication system is analyzed with emphasis placed on the QDSB demodulation process and the AGC action in the FM transmitter. The effect of noise in both the pilot and message signals is investigated. The detection gain and mean square error is calculated for the QDSB baseband demodulation process. The mean square error is also evaluated for the QDSB/FM system. The AGC circuit is simulated on a digital computer. Errors introduced into the AGC system are analyzed with emphasis placed on nonlinear gain functions for the voltage con trolled amplifier. -

E2L005 ROTCH a Day in the Life of the RF Spectrum

A Day in the Life of the RF Spectrum by James E. Cooley B.S., Computer Engineering Northwestern University (1999) Submitted to the Program of Media Arts and Sciences, School of Architecture and Planning, In partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN MEDIA ARTS AND SCIENCES at the MASSACHUSETTS INSTITUTE OF TECHNOLOGY September 2005 © Massachusetts Institute of Technology, 2005. All rights reserved. Signature of Author: Program in Media Arts and Sciences August 5, 2005 Certified by: Andrew B. Lippman Senior Research Scientist of Media Arts and Sciences Program in Media Arts and Sciences Thesis Supervisor Accepted by: Andrew B. Lippman Chairman, Departmental Committee on Graduate Studies Program in Media Arts and Sciences tMASSACHUSETT NSE IT 'F TECHNOLOG Y E2L005 ROTCH A Day in the Life of the RF Spectrum by James E. Cooley Submitted to the Program of Media Arts and Sciences, School of Architecture and Planning, September 2005 in partial fulfillment of the requirement for the degree of Master of Science in Media Arts and Sciences Abstract There is a misguided perception that RF spectrum space is fully allocated and fully used though even a superficial study of actual spectrum usage by measuring local RF energy shows it largely empty of radiation. Traditional regulation uses a fence-off policy, in which competing uses are isolated by frequency and/or geography. We seek to modernize this strategy. Given advances in radio technology that can lead to fully cooperative broadcast, relay, and reception designs, we begin by studying the existing radio environment in a qualitative manner. -

![Arxiv:1306.0942V2 [Cond-Mat.Mtrl-Sci] 7 Jun 2013](https://docslib.b-cdn.net/cover/1341/arxiv-1306-0942v2-cond-mat-mtrl-sci-7-jun-2013-1331341.webp)

Arxiv:1306.0942V2 [Cond-Mat.Mtrl-Sci] 7 Jun 2013

Bipolar electrical switching in metal-metal contacts Gaurav Gandhi1, a) and Varun Aggarwal1, b) mLabs, New Delhi, India Electrical switching has been observed in carefully designed metal-insulator-metal devices built at small geometries. These devices are also commonly known as mem- ristors and consist of specific materials such as transition metal oxides, chalcogenides, perovskites, oxides with valence defects, or a combination of an inert and an electro- chemically active electrode. No simple physical device has been reported to exhibit electrical switching. We have discovered that a simple point-contact or a granu- lar arrangement formed of metal pieces exhibits bipolar switching. These devices, referred to as coherers, were considered as one-way electrical fuses. We have identi- fied the state variable governing the resistance state and can program the device to switch between multiple stable resistance states. Our observations render previously postulated thermal mechanisms for their resistance-change as inadequate. These de- vices constitute the missing canonical physical implementations for memristor, often referred as the fourth passive element. Apart from the theoretical advance in un- derstanding metallic contacts, the current discovery provides a simple memristor to physicists and engineers for widespread experimentation, hitherto impossible. arXiv:1306.0942v2 [cond-mat.mtrl-sci] 7 Jun 2013 a)Electronic mail: [email protected] b)Electronic mail: [email protected] 1 I. INTRODUCTION Leon Chua defines a memristor as any two-terminal electronic device that is devoid of an internal power-source and is capable of switching between two resistance states upon application of an appropriate voltage or current signal that can be sensed by applying a relatively much smaller sensing signal1. -

Fm Demodulation Using a Digital Radio and Digital Signal Processing

FM DEMODULATION USING A DIGITAL RADIO AND DIGITAL SIGNAL PROCESSING By JAMES MICHAEL SHIMA A THESIS PRESENTED TO THE GRADUATE SCHOOL OF THE UNIVERSITY OF FLORIDA IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE UNIVERSITY OF FLORIDA 1995 Copyright 1995 by James Michael Shima To my mother, Roslyn Szego, and To the memory of my grandmother, Evelyn Richmond. ACKNOWLEDGMENTS First, I would like to thank Mike Dollard and John Abaunza for their extended support of my research. Moreover, their guidance and constant tutoring were unilaterally responsible for the origin of this thesis. I am also grateful to Dr. Scott Miller, Dr. Jose Principe, and Dr. Michel Lynch for their support of my research and their help with my thesis. I appreciate their investment of time to be on my supervisory committee. Mostly, I must greatly thank and acknowledge my mother and father, Ronald and Roslyn Szego. Without their unending help in every facet of life, I would not be where I am today. I also acknowledge and greatly appreciate the financial help of my grandmother, Mae Shima. iv TABLE OF CONTENTS ACKNOWLEDGMENTS ................................................................................................. iv CHAPTER 1 ........................................................................................................................1 INTRODUCTION................................................................................................................1 1.1 Background Overview ............................................................................................1 -

Amplitude Modulation

ENSC327 Communications Systems 3. Amplitude Modulation School of Engineering Science Simon Fraser University 1 Outline Some Required Background Overview of Modulation What is modulation? Why modulation? Overview of analog modulation History of AM & FM Radio Broadcast Linear Modulation: Amplitude modulation 2 Some Required Background Basics of sinusoidal signals: amplitude, frequency, phase. RC Circuits, Natural Response. Assume initial voltage to be ( ). Recall from ENSC-220, what is ( )? 0 Fourier Transform of cos 2 or a complex exponential. Properties of FT, e.g., shift in frequency, Parseval’s theorem. Definition of Bandwidth (BW) (see Lecture 2) 3 Overview of Modulation What is modulation? The process of varying a carrier signal in order to use that signal to convey information. Why modulation? 1. Reducing the size of the antennas: The optimal antenna size is related to wavelength: Voice signal: 3 kHz 4 Overview of Modulation Why modulation? 2. Allowing transmission of more than one signal in the same channel (multiplexing) 3. Allowing better trade-off between bandwidth and signal-to-noise ratio (SNR) 5 Analog modulation The input message is continuous in time and value Continuous-wave modulation (focus of this course) A parameter of a high-freq carrier is varied in accordance with the message signal If a sinusoidal carrier is used, the modulated carrier is: Linear modulation: A(t) is linearly related to the message. AM, DSB, SSB Angle modulation: Phase modulation: Φ(t) is linearly related the message. Freq. -

Real-Time Photon-Noise Limited Optical Coherence Tomography Based on Pixel-Level Analog Signal Processing

Real-Time Photon-Noise Limited Optical Coherence Tomography Based on Pixel-Level Analog Signal Processing A dissertation submitted to the Faculty of Science of the University of Neuchâtel for the degree of Doctor of Science presented by Stephan Beer column bus OC sub/int S/H pixel follower buffer sub/int S/H PD pixel follower 0.8 0.6 4 0.4 0.2 2 5 4 3 2 0 1 0 2006 ii iv f¨urmeine geliebte Frau Christine vi Abstract This thesis presents the development of a CMOS smart imager for real-time optical coherency tomography (OCT). OCT is a measuring technique that allows the acquisi- tion of three-dimensional pictures of discontinuities in the refractive index and phase steps in the sample. This technique has gained a lot of impact not only for many bio- medical but also for industrial applications over the last few years, especially due to the achieved depth resolution in the micrometer range. It allows topographic imaging and the determination of surfaces as well as the tomographic acquisition of transpa- rent and turbid objects. This method features an outstanding depth resolution in the sub-micrometer scale over a depth range of up to some millimeters. OCT is based on the low-coherence interferometry (white-light interferometry) with light in the visible or near infrared spectrum. The underlying physical principle allows the suppression of multiply-scattered photons in order to detect mainly ballistic photons, i.e. direct re- flected photons. The goal of this thesis was to realize a very fast, robust 3D OCT system performing close to the physical limit. -

ES442 Lab 6 Frequency Modulation and Demodulation

ES442 Lab#6 ES442 Lab 6 Frequency Modulation and Demodulation Objective 1. Build simple FM demodulator by using frequency discriminator 2. Build simple envelope detector for FM demodulation. 3. Using MATLAB m-file and simulink to implement FM modulation and demodulation. Part List 1uF capacitor (2); 10.0Kohm resistor, 1.0Kohm resistor, Power supply with +/-5V, Scope and frequency analyzer, FM signal Generator. Estimated Time About 90 minutes. Introduction Frequency modulation is a form of modulation, which represents information as variations in the instantaneous frequency of a carrier wave. In analog applications, the carrier frequency is varied in direct proportion to changes in the amplitude of an input signal. This is shown in Fig. 1. Figure 1, Frequency modulation. The FM-modulated signal has its instantaneous frequency that varies linearly with the amplitude of the message signal. Now we can get the FM-modulation by the following: where Kƒ is the sensitivity factor, and represents the frequency deviation rate as a result of message amplitude change. The instantaneous frequency is: Ver 2. 1 ES442 Lab#6 The maximum deviation of Fc (which represents the max. shift away from Fc in one direction) is: Note that The FM-modulation is implemented by controlling the instantaneous frequency of a voltage-controlled oscillator(VCO). The amplitude of the input signal controls the oscillation frequency of the VCO output signal. In the FM demodulation what we need to recover is the variation of the instantaneous frequency of the carrier, either above or below the center frequency. The detecting device must be constructed so that its output amplitude will vary linearly according to the instantaneous freq. -

Quadrature Amplitude Modulation (QAM)

Quadrature Amplitude Modulation (QAM) PAM signals occupy twice the bandwidth required for the baseband Transmit two PAM signals using carriers of the same frequency but in phase and quadrature Demodulation: QAM Transmitter Implementation QAM is widely used method for transmitting digital data over bandpass channels A basic QAM transmitter Inphase component Pulse a Impulse a*(t) a(t) n Shaping Modulator + d Map to Filter sin w t n Serial to c Constellation g (t) s(t) Parallel T Point * Pulse 1 Impulse b (t) b(t) Shaping - J Modulator bn Filter quadrature component gT(t) cos wct Using complex notation = − = ℜ s(t) a(t)cos wct b(t)sin wct s(t) {s+ (t)} which is the preenvelope of QAM ∞ ∞ − = + − jwct = jwckT − jwc (t kT ) s+ (t) (ak jbk )gT (t kT )e s+ (t) (ck e )gT (t kT)e −∞ −∞ Complex Symbols Quadriphase-Shift Keying (QPSK) 4-QAM Transmitted signal is contained in the phase imaginary imaginary real real M-ary PSK QPSK is a special case of M-ary PSK, where the phase of the carrier takes on one of M possible values imaginary real Pulse Shaping Filters The real pulse shaping g (t) filter response T = jwct = + Let h(t) gT (t)e hI (t) jhQ (t) = hI (t) gT (t)cos wct = where hQ (t) gT (t)sin wct = − This filter is a bandpass H (w) GT (w wc ) filter with the frequency response Transmitted Sequences Modulated sequences before passband shaping ' = ℜ jwc kT = − ak {ck e } ak cos wc kT bk sin wc kT ' = ℑ jwc kT = + bk {ck e } ak sin wc kT bk cos wc kT Using these definitions ∞ = ℜ = ' − − ' − s(t) {s+ (t)} ak hI (t kT) bk hQ (t kT) -

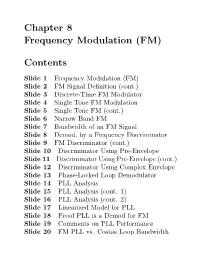

Chapter 8 Frequency Modulation (FM) Contents

Chapter 8 Frequency Modulation (FM) Contents Slide 1 Frequency Modulation (FM) Slide 2 FM Signal Definition (cont.) Slide 3 Discrete-Time FM Modulator Slide 4 Single Tone FM Modulation Slide 5 Single Tone FM (cont.) Slide 6 Narrow Band FM Slide 7 Bandwidth of an FM Signal Slide 8 Demod. by a Frequency Discriminator Slide 9 FM Discriminator (cont.) Slide 10 Discriminator Using Pre-Envelope Slide 11 Discriminator Using Pre-Envelope (cont.) Slide 12 Discriminator Using Complex Envelope Slide 13 Phase-Locked Loop Demodulator Slide 14 PLL Analysis Slide 15 PLL Analysis (cont. 1) Slide 16 PLL Analysis (cont. 2) Slide 17 Linearized Model for PLL Slide 18 Proof PLL is a Demod for FM Slide 19 Comments on PLL Performance Slide 20 FM PLL vs. Costas Loop Bandwidth Slide 21 Laboratory Experiments for FM Slide 21 Experiment 8.1 Making an FM Modulator Slide 22 Experiment 8.1 FM Modulator (cont. 1) Slide 23 Experiment 8.2 Spectrum of an FM Signal Slide 24 Experiment 8.2 FM Spectrum (cont. 1) Slide 25 Experiment 8.2 FM Spectrum (cont. 1) Slide 26 Experiment 8.2 FM Spectrum (cont. 3) Slide 26 Experiment 8.3 Demodulation by a Discriminator Slide 27 Experiment 8.3 Discriminator (cont. 1) Slide 28 Experiment 8.3 Discriminator (cont. 2) Slide 29 Experiment 8.4 Demodulation by a PLL Slide 30 Experiment 8.4 PLL (cont.) 8-ii ✬ Chapter 8 ✩ Frequency Modulation (FM) FM was invented and commercialized after AM. Its main advantage is that it is more resistant to additive noise than AM. Instantaneous Frequency The instantaneous frequency of cos θ(t) is d ω(t)= θ(t) (1) dt Motivational Example Let θ(t) = ωct. -

QAM Demodulation 0 QAM Demodulation

S. Brand, Philips Semiconductors, PCALE QAM Demodulation 0 QAM Demodulation o Application area o What is QAM? o What are QAM Demodulation Functions? o General block diagram of QAM demodulator o Explanation of the main function (Nyquist shaping, Clock & Carrier Recovery, AGC, Adaptive Equaliser) o Performance o Conclusion Wireless Communications S. Brand, Philips Semiconductors, PCALE QAM Demodulation 1 Example Application Area “Wireless Cable” Digital TV using Microwave Transmission QAM Modulation Set-top Box Multiplexing Radio Channel Compression · Compression = bit rate reduction · Multiplexing = assembly of multiple programs · Modulation = conversion to transmission format · Set-top Box = Integrated Receiver Decoder (IRD), provides a subscriber access to a wide range of programs Wireless Communications S. Brand, Philips Semiconductors, PCALE QAM Demodulation 2 What is QAM? o Amplitude Modulation of 2E 2E o Two Orthogonal Carriers o o xi (t) = ---------ai cos(wct) + ---------bi sin (wct) Ts Ts a =+3 a =+1 a =-7 +7 i-1 i i+1 Q +5 +3 7 +1 -1 I 5 -3 -5 Ts 3 -7 ÖEo bi-1=-5 bi=+5 bi+1=-1 1 I +7 ÖEo +5 Tc -1 +3 +1 -1 Q -3 -3 -5 -5 -7 -7 time -7 -5 -3 -1 1 3 5 7 64QAM in time domain 64QAM Constellation diagram Wireless Communications S. Brand, Philips Semiconductors, PCALE QAM Demodulation 3 M-ary QAM { { I Q Satellite Cable b5b4b3b2b1b0 b1b0 Noise power signal power S/N > 3 dB for M=4 S/N > 21 dB for M=64 S/N > 27 dB for M=256 Wireless Communications S. Brand, Philips Semiconductors, PCALE QAM Demodulation 4 What to do to recover the information? Functions Result Automatic Gain Control Optimal position of constellation diagram in reception window Quadrature I & Q base band signals down conversion (Half) Nyquist Filtering Pulse shaping Clock Recovery Sampling reference for A/D Converter Carrier Recovery Carrier frequency reference Adaptive Equaliser Compensate for channel distortion Demapping Representation of received data in bits Wireless Communications S.