Profiling Tools for FPGA-Based Embedded

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Atmosphere Inside a Bag of Potato Chips.Pdf

THE A T M O S P H E R I C R E S E R V O I R Examining the Atmosphere and Atmospheric Resource Management The Atmosphere Inside a Bag of Potato Chips AIR By Mark D. Schneider Changes in atmospheric pressure occur all around us and in Potato Chips North Dakota our gusty winds are the most obvious example. When we fly in a commercial jet or drive over a mountain Potato Chips pass, our ears tell us about a pressure change by popping. Potato Chips Suppose that you’re a potato chip company wanting to distribute your product to many locations across the country. Some of these locations are at high altitudes which can cause your potato chip bags to expand and possibly burst open due During MAP, nitrogen gas is repeatedly injected and to a change in atmospheric pressure. How do you package removed from food packaging to eliminate oxygen. This and ship your chips without damaging them? Certainly process can reduce the oxygen content to 3% or less. The end climate-controlled trucks or containers are one part of the result is increased shelf-life with a longer expiration date for solution. By keeping your product at a constant temperature, consumers. you’re eliminating a change in pressure due to either heating or cooling. Once a bag of potato chips is opened, the inevitable mixing of outside air begins to oxidize the contents and degrade The initial packaging process before the potato chips are the freshness. The 21 percent oxygen gas now introduced shipped plays the largest role in successful distribution to the bag begins its work breaking down the oils that help though. -

NBC TICKET OPTIONS July 29Th – August 13Th 2016

NBC TICKET OPTIONS July 29th – August 13th 2016 Skybox Value # Allocated Min # Max # Ticket Includes All 16 Days $4,000 25 $1000 Food and Beverage Credit Included Friday-Saturday $750 25 $250 Food and Beverage Credit Included Sunday - Thursday $600 25 $200 Food and Beverage Credit Included Group Field Pass - Friday - Saturday $250 15 30 Adult Beverages and $50 Concession Credit Field Pass - Sunday - Thursday $200 15 30 Adult Beverages and $40 Concession Credit $40 Food and Adult Beverage, $30 Food Only, $20 3-12 years old. All you can Eat! Includes slow-smoked pulled pork, all beef hot dogs, brats, baked beans, kettle chips, popcorn, peanuts, soda, water, beer, and wine. Beer and Wine are limited. Includes a Party Deck (All Inclusive) $20-$40 20-70 20 70 reserved lower seat ticket. The Home Run - Includes all beef hot dogs, baked beans, kettle chips, soda & water. $15/person. Includes reserved lower seat ticket. The Grand Slam - Includes all beef hot dogs, cheeseburgers w/fixins, baked beans, kettle chips, soda & water. $20/person. Includes reserved lower seat ticket. Pre-game Picnic The "BBQ" Slam - Includes slow-smoked pulled pork, all beef hot dogs, baked beans, Hard Ball Café – 200 people Max kettle chips, soda, water, lemonade & tea. $22/person. Includes reserved lower seat Miller Lite Pavilion – 500 People Max $15,20,22 20 500 ticket. Individual Session Tickets—All Day Lower Box Seats (Lower Section) $11 Upper Box Seats & GA Bleachers (Upper Section) $7 Ticket Packages World Series Pass-Lower Box (Lower Section) $140 World Series -

Applications of Microfluidic Chips in Optical Manipulation Photoporation

APPLICATIONS OF MICROFLUIDIC CHIPS IN OPTICAL MANIPULATION & PHOTOPORATION Robert Frank Marchington A Thesis Submitted for the Degree of PhD at the University of St. Andrews 2010 Full metadata for this item is available in Research@StAndrews:FullText at: https://research-repository.st-andrews.ac.uk/ Please use this identifier to cite or link to this item: http://hdl.handle.net/10023/1633 This item is protected by original copyright Applications of Microfluidic Chips in Optical Manipulation & Photoporation Robert Frank Marchington A thesis presented for the degree of Doctor of Philosophy Optical Trapping & Microphotonics Groups School of Physics & Astronomy University of St Andrews June 2010 Dedicated to Mum & Mike Joe & Xanthoula Applications of Microfluidic Chips in Optical Manipulation and Photoporation Robert Frank Marchington Submitted for the degree of Doctor of Philosophy June 2010 Abstract Integration and miniaturisation in electronics has undoubtedly revolutionised the modern world. In biotechnology, emerging lab-on-a-chip (LOC) methodologies pro- mise all-integrated laboratory processes, to perform complete biochemical or medical synthesis and analysis encapsulated on small microchips. The integration of electri- cal, optical and physical sensors, and control devices, with fluid handling, is creating a new class of functional chip-based systems. Scaled down onto a chip, reagent and sample consumption is reduced, point-of-care or in-the-field usage is enabled through portability, costs are reduced, automation increases the ease of use, and favourable scaling laws can be exploited, such as improved fluid control. The capacity to mani- pulate single cells on-chip has applications across the life sciences, in biotechnology, pharmacology, medical diagnostics and drug discovery. -

Flavor Enhancement in Chips, Crisps & Savory Applications

Flavor enhancement in Chips, Crisps & Savory Applications Manufacturers of chips, crisps and savory foodstuffs are working hard to replace the old ingredients in their formulations by new and natural ones in order to respond to the consumers’ need for healthy and tasty snacks. Although snacks are inexpensive, tasty and easily available, they are known to have a negative impact on health due to the use of some harmful additives, such as BHA and BHT, or monosodium glutamate, used for flavor enhancement. Since consumers are now more and more health-aware, chips manufacturers must come up with healthier alternatives. Based on this particular need, Galactic has Advantages developed Galacid™ Powder 60, an effective solution that will make chips, ✓ Enhancement of meat salty biscuits, etc. both tasty and safer for flavors consumption. It consists of 60% free L(+) ✓ Enhance cheese and lactic acid and calcium lactate as carrier, herb flavors is highly stable and has a minimal hygroscopic behavior. The general ✓ Low hygroscopicity functionalities of lactic acid powder are pH regulator and flavor enhancer in ✓ various savory products. In snacks applications, Galacid™ Powder 60 enhances flavors such as meat, dairy and herbs. For example, barbecue flavor chips, cheese & onion flavors crisps, barbecue biscuits, etc. The calcium lactate contained in Galacid™ Powder 60 helps increase the crispiness and reduce the fat absorbed by the product if it is fried. RECOMMENDED USE AND FUNCTIONALITIES: Flavor enhancement by lactic acid Dosage range in finished product Functionality Savory (flavoring) by application Declaration Cheese Examples of dosage in Cream Galacid™ crisps flavorings: Pepper 1,0% - 4,0% E 327 (Calcium lactate) Tomato Powder 60 1-3% in cheese & onion E 270 (Lactic acid) Onion 2-4% in salt & vinegar Soy In general, 6% w/w of Chili flavoring Ginger Galactic Our FOOD Development team remains at your disposal for further trials, Innovation Campus information, training etc. -

Appendix A: Non-Executive Directors of Channel 4 1981–92

Appendix A: Non-Executive Directors of Channel 4 1981–92 The Rt. Hon. Edmund Dell (Chairman 1981–87) Sir Richard Attenborough (Deputy Chairman 1981–86) (Director 1987) (Chairman 1988–91) George Russell (Deputy Chairman 1 Jan 1987–88) Sir Brian Bailey (1 July 1985–89) (Deputy Chairman 1990) Sir Michael Bishop CBE (Deputy Chairman 1991) (Chairman 1992–) David Plowright (Deputy Chairman 1992–) Lord Blake (1 Sept 1983–87) William Brown (1981–85) Carmen Callil (1 July 1985–90) Jennifer d’Abo (1 April 1986–87) Richard Dunn (1 Jan 1989–90) Greg Dyke (11 April 1988–90) Paul Fox (1 July 1985–87) James Gatward (1 July 1984–89) John Gau (1 July 1984–88) Roger Graef (1981–85) Bert Hardy (1992–) Dr Glyn Tegai Hughes (1983–86) Eleri Wynne Jones (22 Jan 1987–90) Anne Lapping (1 Jan 1989–) Mary McAleese (1992–) David McCall (1981–85) John McGrath (1990–) The Hon. Mrs Sara Morrison (1983–85) Sir David Nicholas CBE (1992–) Anthony Pragnell (1 July 1983–88) Usha Prashar (1991–) Peter Rogers (1982–91) Michael Scott (1 July 1984–87) Anthony Smith (1981–84) Anne Sofer (1981–84) Brian Tesler (1981–85) Professor David Vines (1 Jan 1987–91) Joy Whitby (1981–84) 435 Appendix B: Channel 4 Major Programme Awards 1983–92 British Academy of Film and Television Arts (BAFTA) 1983: The Snowman – Best Children’s Programme – Drama 1984: Another Audience With Dame Edna – Best Light Entertainment 1987: Channel 4 News – Best News or Outside Broadcast Coverage 1987: The Lowest of the Low – Special Award for Foreign Documentary 1987: Network 7 – Special Award for Originality -

R-44 Instruct ID 08-01-04

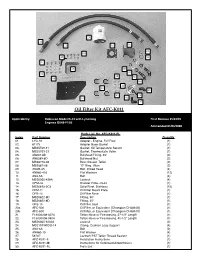

20 22 21 02 01 03 09 10 04 11 15 08 07 12 25 06 14 05 26 24 18 23 19 13 16 17 Oil Filter Kit AFC-K011 Applicability: Robinson Model R-44 with Lycoming First Release 05/24/95 Engines O540-F1B5 Ammended 01/08/2000 Parts List No. AFC-K011-PL Index Part Number Description Quantity 01. LYC-10 Adapter - Engine, Full Flow (1) 02. 61173 Adapter Base Gasket (1) 03. MS35769-11 Gasket, Oil Temperature Sensor (1) 04. MS35769-21 Gasket, Thermostatic Valve (1) 05. AN837-8D Bulkhead Fitting, 45° (2) 06. AN6289-8D Bulkhead Nut (2) 07. MS28773-08 Boss Gasket, Teflon (2) 08. MS9387-08 “O” Ring, Viton (2) 09. AN4H-4A Bolt, Drilled Head (4) 10. AN960-416 Flat Washers (12) 11. AN4-5A Bolt (4) 12. MS20365-428A Locknut (4) 13. OFM-16 Doubler Plate - R-44 (1) 14. MS20613-3C3 Solid Rivet, Stainless (15) 15. OFM-11 Oil FIlter Mount Plate (1) 16. OFB-10 Oil Filter Base (1) 17. MS20822-8D Fitting, 90° (1) 18. MS20823-8D Fitting, 45° (1) 19. OFS-10 Oil Filter Stud (1) 20a. AFC-500 Oil Filter, or Equivalent [Champion CH48108] (1) 20b. AFC-600 Oil Filter, or Equivalent [Champion CH48109] (1) 21. F13000008-0274 Teflon Hose w/ Firesleeving, 27-1/2" Length (1) 22. F13000008-0404 Teflon Hose w/ Firesleeving, 40-1/2" Length (1) 23. MS20365-1032A Locknut (2) 24. MS21919WDG-14 Clamp, Cushion Loop Support (4) 25. AN3-4A Bolt (2) 26. AN960-10 Flat Washer (4) 27. 56707 Loctite® PST Teflon Thread Sealant (1) 28. -

Northern Virginia (VSGA Northern Sections) Interclub "A" Team Matches 2019 Rules Sheet

Northern Virginia (VSGA Northern Sections) Interclub "A" Team Matches 2019 Rules Sheet Teams and Schedule: To be determined shortly after entries close on March 1st, 2019. Schedule will be posted to web site (www.vsgane.com) as well as e-mailed to contact points (A-Team captains and club professionals) at participating clubs. Matches are open to member clubs of the VSGA Northern Virginia Sections (Northeast, Northcentral, Northwest and Fredericksburg Sections). Starting Times: 11:30 a.m. Matches may begin as early as 11:00 a.m. or as late as 12:00 noon, provided that the visiting team is notified at least 72 hours in advance. Team captains are responsible for coordinating starting times for the matches. The captain of the team unable to start at 11:30 a.m. is responsible for contacting the captain of the opposing team. Please coordinate! Rules: Whether play is to be by summer or winter rules is to be determined by the host superintendent. One professional (head or staff) from each club will be eligible to play on the A-Team. Any member of the professional staff may participate and must play in the first group, either home or away. A professional does not have to play, but the opponent may still utilize a professional. The host (non-playing) professional will make any necessary rulings and will have the final word. Team captains are responsible for making their professionals aware of this task. Format: A twelve-member team plays three two-man matches at home and three two- man matches away. Each team competes in a better ball format (four-ball competition) at each club. -

Volkswagen Cabriolets on Television

Volkswagen Cabriolets on Television (Separated by genre. Not in alphabetical order, so use Ctrl+F to find a specific title. Some have embedded links to external videos/photos. Key to star ratings is on last page. Made-for-TV movies are listed in the equivalent film document.) Genre: Documentary/Informational/News Motorweek 20 Cars That Changed The World What Would You Do? 1989 2001; Episode 3 ABC News Special Telemotor Autotest Telemotor Autotest 60 Jahre Volkswagen 1979/1980 ca. 1988 2009 Genre: Mini-series The Man Who Made Husbands Jealous Floodtide Un été de canicule 1997 1987; Episode: 1.03 2003; Episode: 3 Goltuppen Devices & Desires Den Svarta Cirkeln 1991; Episode: 3 1991; Episode: 2 1990; Episode: 1 © 2015 KamzKreationz 1 Cabriolets on TV Genre: Comedy/Sitcom/Dramedy Chuck Chuck Curb Your Enthusiasm 2007; Episode 1.07 2008; Episode 2.04 2004; Episode 4.08 Dharma & Greg Doogie Howser, M.D. 2001; Episode 5.04 1989; Episode 1.01 Grace Under Fire Hannah Montana Hannah Montana 1996; Episode 4.17 2006; Episode 1.02 2006; Episode 1.14 King of Queens King of Queens King of Queens 1998; Episode 1.__ 1999; Episode 2.09 2000; Episode 3.01 1999; Episode 2.22 2000; Episode 3.08 Malcolm In The Middle Malcolm In The Middle My Name Is Earl 2001; Episode 2.09 2001; Episode 2.01 2006; Episode 2.07 © 2015 KamzKreationz 2 Cabriolets on TV Reno 911! Saved By The Bell Seinfeld 2003; Episode 1.05 Seasons 3 & 4 DVD cover 1991; Episode 3.06 Seinfeld Seinfeld Step By Step 1992; Episode 4.22 1993; Episode 5.03 1991; Episode 1.16 That '70s Show The Big Bang -

Data Sheets PIN Diode Chips Supplied on Film Frame

DATA SHEET PIN Diode Chips Supplied on Film Frame Applications Switches Attenuators Features Preferred device for module applications PIN diodes supplied are 100% tested, saw cut, and mounted on film frame Description Low cost The PIN diodes that comprise this family of diodes supplied on film frames are designed for high-volume applications from 10 MHz to over 3 GHz. This family contains three groups of PIN diodes: Skyworks GreenTM products are compliant with 1. Low-capacitance, low-resistance PIN diodes designed primarily all applicable legislation and are halogen-free. for RF switching applications: For additional information, refer to Skyworks SMP1320-099 Definition of GreenTM, document number SMP1321-099 SQ04–0074. SMP1322-099 SMP1340-099 2. PIN diodes with mid-range I-layers and resistance designed for either RF switching or attenuator applications: SMP1302-099 SMP1331-099 SMP1353-099 3. PIN diodes with thick I-layers designed for low-distortion RF variable attenuator applications: SMP1304-099 SMP1307-099 These PIN diodes are provided as 100 percent tested, diced wafers mounted on film frames for optimal compatibility with high-volume pick-and-place assembly techniques. Absolute maximum ratings are provided in Table 1. Electrical specifications are provided in Table 2. Chip dimensions are shown in Table 3. Typical performance characteristics are illustrated in Figures 1 through 5. Figure 6 describes the wafer film frame. Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • [email protected] • www.skyworksinc.com 200140M • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • June 24, 2016 1 DATA SHEET • PIN DIODE CHIPS SUPPLIED ON FILM FRAME Table 1. -

Thin Film Resistor Chips

Thin Film Resistor Chips Resistor Ordering System 4) Is the resistor value total % + tolerance See chart below 5) Is the 2nd resistor value total % ±tolerance (if applicable) Example 1 2 3 4 5 6 7 8 A + 0.5 Ohm F + 1% MTR - 2R2K - SR2 - K - NA - G - 1 - T B + 1.0 Ohm G + 2% C + 2.5 Ohm J + 5% D + .01% K + 10% E + .1% M + 20% 1) Is the three letter device type designation NA Not applicable A) On Dual Value Resistors, (MCR), this is the res. ratio of the 2nd resistor MTR Single Value through Chip Resistor (Resistance top to bottom) (Ratio Res.) To value of the 1st resistor (Prime Res.). B) On Multi Tap Resistors (MMR). This is the tolerance of each of the small value Resistor Taps. The large value Resistor Taps are called out on (4) MIR Single Value Pad to Pad Chip Resistor (Resistance Top pad to Top pad) MCR Dual Value Center Tap Ratio Chip Resistor (Res. #1 = Prime 6) Backing Value / Res. #2 = Ratio Value) G Solderable Gold MMR MultiTap Chip Resistor. GS Gold Silicon eutectic attachment B Bare XXX as needed. 7) The temperature coefficient (TCR) of the resistor, in PPM 2) Is the resistance value in ohms 0 + 150 PPM 1 + 100 PPM 2R2K 2,200 Ohms 2 + 50 PPM 200R 200 Ohms 3 + 10 PPM 20R 20 Ohms 2R2M 2,200,000 Ohms 8) Resistor Material 20R2K 20,200 Ohms 200RK 200,000 Ohms T Tantalum Nitride TaN (Self Passivating) 2R 2.0 Ohms N NiChrome NiCr 3) is the chip substrate material and Example: part no. -

CHIPS): Studying the Interstellar Medium

FS-2002-11-048-GSFC Cosmic Hot Interstellar Plasma Spectrometer (CHIPS): Studying the Interstellar Medium The Cosmic Hot Interstellar Plasma extreme ultraviolet region of the electromag- Spectrometer satellite is the first NASA netic spectrum, centered around 170 University-Class Explorer mission. The Angstroms (Å). This is a relatively unsurveyed CHIPS mission is studying the very hot, very band and the emissions at this wavelength low-density gas in the vast spaces between may contain important clues about the the stars in our local astronomical neighbor- process of cooling that takes place in the hood. The majority of the power radiated by Local Bubble of the Interstellar Medium. this hot gas occurs in the short-wavelength, In our galaxy alone, there are several hun- About 99% of the ISM is gas (hydrogen and dred billion stars. Nearby stars are easy to helium), the remaining one percent consists see, although most of the stars in the Milky of heavier elements and dust. The gas is Way are so distant that their combined light extremely dilute, with an average density of appears as a fuzzy band stretching across about 1 atom per cubic centimeter. The air we the sky on a clear night. Equally easy to see breathe is approximately 30 quintillion is the space between the stars - but how often (30,000,000,000,000,000,000) times more do you wonder about this space? Most of us dense than the ISM. Picture this: an "empty" have an idea that these vast spaces are coffee mug in the ISM would contain about empty, a perfect vacuum. -

Grade 4 Math Answer Key

Grade 4 Math Answer Key Grade 4 Standards Operations and Algebraic Thinking Measurement and Data 4.OA.A.01 4.MD.A.01 4.OA.A.02 4.MD.A.02 4.OA.A.03 4.MD.A.03 4.OA.B.04a 4.MD.B.04 4.OA.B.04b 4.MD.C.05b 4.OA.B.04c 4.MD.C.05c 4.OA.C.05 4.MD.C.06 4.MD.C.07 Number and Operations in Base Ten 4.MD.D.08 4.NBT.A.01 4.NBT.A.02 Geometry 4.NBT.A.03 4.G.A.01 4.NBT.B.04 4.G.A.02 4.NBT.B.05 4.G.A.03 4.NBT.B.06 Number and Operations—Fractions 4.NF.A.01 4.NF.A.02 4.NF.B.03a 4.NF.B.03b 4.NF.B.03c 4.NF.B.03d 4.NF.B.04a 4.NF.B.04b 4.NF.B.04c 4.NF.C.05 4.NF.C.06 4.NF.C.07 These items may be used by Louisiana educators for educational purposes. Operations and Algebraic Thinking 4.OA.A.01 Items 1 – 6 ITEM 1 Which statement is a correct interpretation of the equation? 14 × 3 = 42 A. 14 is 3 more than 42. B. 42 is 14 more than 3. C. 14 is 3 times as many as 42. D. 42 is 3 times as many as 14. These items may be used by Louisiana educators for educational purposes. ITEM 2 Which statement best describes the equation? 120 = 6 x 20 A.