Introduction Aux Systèmes Informatiques Introduction Générale

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Passmark Intel Vs AMD CPU Benchmarks - High End

PassMark Intel vs AMD CPU Benchmarks - High End http://www.cpubenchmark.net/high_end_cpus.html Shopping cart | Search Home Software Hardware Benchmarks Services Store Support Forums About Us Home » CPU Benchmarks » High End CPU's CPU Benchmarks Video Card Benchmarks Hard Drive Benchmarks RAM PC Systems Android iOS / iPhone CPU Benchmarks Over 600,000 CPUs Benchmarked High End CPU's - Intel vs AMD How does your CPU compare? This chart comparing high end CPU's is made using thousands of PerformanceTest benchmark Add your CPU to our benchmark results and is updated daily. These are the high end AMD and Intel CPUs are typically those chart with PerformanceTest V8 found in newer computers. The chart below compares the performance of Intel Xeon CPUs, Intel Core i7 CPUs, AMD Phenom II CPUs and AMD Opterons with multiple cores. Intel processors vs ---- Select A Page ---- AMD chips - find out which CPU's performance is best for your new gaming rig or server! CPU Mark | Price Performance (Click to select desired chart) PassMark - CPU Mark High End CPUs - Updated 26th of August 2013 Price (USD) Intel Xeon E5-2687W @ 3.10GHz 14,564 $1,929.99 Intel Xeon E5-2690 @ 2.90GHz 14,511 $1,920.99 Intel Xeon E5-2680 @ 2.70GHz 13,949 $1,725.99 Intel Xeon E5-2689 @ 2.60GHz 13,444 NA Intel Xeon E5-2670 @ 2.60GHz 13,312 $1,509.00 Intel Core i7-3970X @ 3.50GHz 12,873 $1,006.99 Intel Core i7-3960X @ 3.30GHz 12,749 $965.99 Intel Xeon E5-1660 @ 3.30GHz 12,457 $1,086.99 Intel Xeon E5-2665 @ 2.40GHz 12,453 $1,499.99 Intel Core i7-3930K @ 3.20GHz 12,086 $567.27 Intel Xeon -

Components © 2017

PCDS.fi Components Mini-ITX SFF Gaming & HTPC Chassis 1/11 2017 AKASA Mini-ITX Compact Thin Cypher Black ALU 1x2.5” VESA 120W Power Adapter 99€ S ILVERSTONE Mini-ITX SFF Slim HTPC Milo ML0 5 Black Slot Loading 1x5.25” 4x2.5” Audio USB 69€ Milo ML0 6 ALU Black Slot Loading 1x5.25” 4x2.5” Audio USB 82€ NEW Milo ML0 9 Black Slim 1x5.25” 4x2.5” Audio USB 82€ NEW Milo ML0 6-E ALU Black Slot Loading 1x5.25” 4x2.5” Audio USB 115€ FRACTAL DESIGN Mini-ITX SFF Slim Gaming & VR NEW Node 202 Black 2x2.5” CC56mm Audio USB Filter 109€ NEW Node 20 2 Integra Black 2x2.5” CC56mm Audio USB Filter Integra 450 PSU 165€ PHANTEKS Mini-ITX SFF Tower NEW ENTHOO EVOLV SHIFT Black 2x3.5” 1x2.5” Audio USB 200mm Fan 135€ S ILVERSTONE Mini-ITX SFF Slim Gaming & VR Milo ML0 7 Black Slot Loading 1x5.25” 1x3.5” 3x2.5” Audio USB 82€ NEW Milo ML0 8 Black Slim 1x5.25” 1x3.5” 2x2.5” CC58mm Audio USB Filter 115€ R AVEN RVZ01 Black Slot Loading 1x5.25” 1x3.5” 3x2.5” Audio USB 2x120mm Fans 129€ NEW R AVEN RVZ01- E Black 3x2.5” CC83mm Audio USB 2x120mm Fans 129€ NEW RAVEN RVZ03 Black 4x2.5” CC83mm Audio USB 2x120mm Fans 135€ NEW R AVEN RVZ0 2 Black Slim 1x5.25” 1x3.5” 2x2.5” Audio USB 115€ NEW R AVEN RVZ0 2 Window Black Slim 1x5.25” 1x3.5” 2x2.5” Audio USB Filter 125€ NEW Fortress FTZ 01 Black / Silver Slot Loading 1x5.25” 1x3.5” 3x2.5” Audio USB 3x120mm Fans 155€ Mini-ITX SFF Cube Chassis 1/11 2017 COOLER MASTER Mini-ITX SFF Cube Elite 1 3 0 Black 1x5.25” 2x3.5” 3x2.5” Audio USB 80+120mm Fans 69€ Elite 1 2 0 Black 1x5.25” 3x3.5”/2.5” Audio USB 80+120mm Fans 71€ Elite 110 Black -

System Builder's Guide for D-Series

Matrox® Display Wall Mura™ IPX Series • D-Series™ System Builder’s Guide 20315-101-0110 2021.07.28 www.matrox.com/video Contents Product overview .....................................................................................................................................................4 Hardware summary – Mura IPX Series.....................................................................................................................................................................4 MURAIPXI-E4SF/MURAIPXI-E4SHF ...............................................................................................................................................4 MURAIPXI-E2MF/MURAIPXI-E2MHF ...........................................................................................................................................5 MURAIPXI-D2MF/MURAIPXI-D2MHF..................................................................................................................................................6 MURAIPXI-E4JF/MURAIPXI-E4JHF ................................................................................................................................................7 MURAIPXI-D4JF/MURAIPXI-D4JHF ..............................................................................................................................................8 Hardware summary – Matrox D-Series ....................................................................................................................................................................9 -

I Processori Amd Trinity

UNIVERSITA’ DEGLI STUDI DI PADOVA __________________________________________________ Facoltà di Ingegneria Corso di laurea in Ingegneria Informatica I PROCESSORI AMD TRINITY Laureando Relatore Luca Marzaro Prof. Sergio Congiu ___________________________________________________________ ANNO ACCADEMICO 2012/2013 ii iii A Giulia, mamma, papà e Diego iv Indice 1. Introduzione 1 1.1 Cenni storici AMD . 1 1.2 Evoluzione del processore: dall' Am386 alle APU Trinity . 2 2. Trinity: Architettura 5 2.1 Introduzione . 5 2.2 Da Llano a Trinity: architettura Piledriver . 6 2.3 Graphics Memory Controller: architettura VLIW4 . 8 2.4 Un nuovo socket: FM2 . 12 3. Specifiche tecniche 15 3.1 Modelli e dati tecnici . 15 3.2 Comparazione con Llano e Intel core i3 . 17 4. Prestazioni 19 4.1 Introduzione . 19 4.2 Applicazioni multimediali . 22 4.3 Calcolo e compressione . 25 4.4 Consumi . 30 5. Considerazioni finali 35 vi INDICE Bibliografia 37 Capitolo 1 Introduzione 1.1 Cenni storici AMD AMD (Advanced Micro Devices) è una multinazionale americana produttrice di semiconduttori la cui sede si trova a Sunnyvale in California. La peculiarità di tale azienda è la produzione di microprocessori, workstation e server, di chip grafici e di chipset. Si classifica seconda al mondo Figura 1.1: Jerry Sanders nella produzione di microprocessori con architettuta x86 dopo Intel. Il primo maggio 1969 Jerry Sanders (vedi Figura 1.1) e sette amici fondano la AMD. Sei anni più tardi, lanciano nel mercato la prima memoria RAM marchiata AMD, la Am9102 e presentano AMD 8080, una variante dell'INTEL 8080 che lancia l'azienda nel mondo dei microprocessori. Dal 1980 AMD si impone come uno dei principali concorrenti di Intel nel mercato dei processori x86- compatibili. -

Lista Sockets.Xlsx

Data de Processadores Socket Número de pinos lançamento compatíveis Socket 0 168 1989 486 DX 486 DX 486 DX2 Socket 1 169 ND 486 SX 486 SX2 486 DX 486 DX2 486 SX Socket 2 238 ND 486 SX2 Pentium Overdrive 486 DX 486 DX2 486 DX4 486 SX Socket 3 237 ND 486 SX2 Pentium Overdrive 5x86 Socket 4 273 março de 1993 Pentium-60 e Pentium-66 Pentium-75 até o Pentium- Socket 5 320 março de 1994 120 486 DX 486 DX2 486 DX4 Socket 6 235 nunca lançado 486 SX 486 SX2 Pentium Overdrive 5x86 Socket 463 463 1994 Nx586 Pentium-75 até o Pentium- 200 Pentium MMX K5 Socket 7 321 junho de 1995 K6 6x86 6x86MX MII Slot 1 Pentium II SC242 Pentium III (Cartucho) 242 maio de 1997 Celeron SEPP (Cartucho) K6-2 Socket Super 7 321 maio de 1998 K6-III Celeron (Socket 370) Pentium III FC-PGA Socket 370 370 agosto de 1998 Cyrix III C3 Slot A 242 junho de 1999 Athlon (Cartucho) Socket 462 Athlon (Socket 462) Socket A Athlon XP 453 junho de 2000 Athlon MP Duron Sempron (Socket 462) Socket 423 423 novembro de 2000 Pentium 4 (Socket 423) PGA423 Socket 478 Pentium 4 (Socket 478) mPGA478B Celeron (Socket 478) 478 agosto de 2001 Celeron D (Socket 478) Pentium 4 Extreme Edition (Socket 478) Athlon 64 (Socket 754) Socket 754 754 setembro de 2003 Sempron (Socket 754) Socket 940 940 setembro de 2003 Athlon 64 FX (Socket 940) Athlon 64 (Socket 939) Athlon 64 FX (Socket 939) Socket 939 939 junho de 2004 Athlon 64 X2 (Socket 939) Sempron (Socket 939) LGA775 Pentium 4 (LGA775) Pentium 4 Extreme Edition Socket T (LGA775) Pentium D Pentium Extreme Edition Celeron D (LGA 775) 775 agosto de -

Comparatif Des Processeurs

Comparatif des processeurs Le microprocesseur (ou processeur) est un composant essentiel de votre ordinateur. Pourtant sur les étiquettes, cet élément est rarement mis en avant, car commercialement ce n'est pas toujours vendeur, les gens font plus attention à la capacité du disque dur, au look de l'ordinateur, ou éventuellement à la puce vidéo. Alors attention quand même, le processeur ne fait pas tout. De la même façon qu'on ne choisit pas une voiture uniquement en fonction du moteur, on ne choisit pas non plus un ordinateur uniquement en fonction du processeur, mais c'est un élément qu'il faut savoir évaluer, au risque de se retrouver avec un ordinateur que vous trouverez toujours trop lent alors qu'il avait l'air très performant en rayon ;) Ce tableau vous aidera à évaluer une grande partie des processeurs existants. La liste des processeurs est triée par ordre alphabétique, et la colonne de droite indique le « score » du processeur. Le score à lui tout seul ne veut rien dire, mais c'est lui qui vous permettra de comparer un processeur par rapport à un autre. Plus le score est élevé, mieux c'est ! Le modèle de microprocesseur est affiché dans les propriétés système et sur l'étiquette en rayon Notez bien sa référence, une seule lettre peut tout changer ! Marque et modèle du processeur Score AMD A10 Micro-6700T APU 1875 AMD A10 PRO-7350B APU 3354 AMD A10 PRO-7800B APU 5313 AMD A10 PRO-7850B APU 5630 AMD A10-4600M APU 3121 AMD A10-4655M APU 2566 AMD A10-4657M APU 3449 AMD A10-5700 APU 4220 AMD A10-5745M APU 2788 AMD A10-5750M APU 3377 -

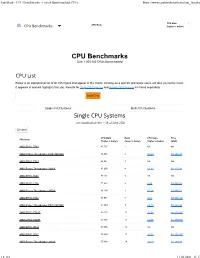

CPU Benchmarks Video Card Benchmarks Hard Drive Benchmarks RAM PC Systems Android Ios / Iphone

Software Hardware Benchmarks Services Store Support About Us Forums 0 CPU Benchmarks Video Card Benchmarks Hard Drive Benchmarks RAM PC Systems Android iOS / iPhone CPU Benchmarks Over 1,000,000 CPUs Benchmarked CPU List Below is an alphabetical list of all CPU types that appear in the charts. Clicking on a specific processor name will take you to the chart it appears in and will highlight it for you. Results for Single CPU Systems and Multiple CPU Systems are listed separately. Find CPU Single CPU Systems Multi CPU Systems CPUS High End Single CPU Systems High Mid Range Last updated on the 28th of May 2021 Low Mid Column Range Low End CPU Mark Rank CPU Value Price CPU Name (higher is (lower is (higher is (USD) better) better) better) Best Value (On Market) AArch64 rev 0 (aarch64) 2,335 1605 NA NA Best Value XY AArch64 rev 1 (aarch64) 2,325 1606 NA NA Scatter Best Value AArch64 rev 2 (aarch64) 1,937 1807 NA NA (All time) AArch64 rev 4 (aarch64) 1,676 1968 NA NA New Desktop AC8257V/WAB 693 2730 NA NA New Laptop AMD 3015e 2,678 1472 NA NA Single Thread AMD 3020e 2,637 1481 NA NA Systems with AMD 4700S 17,756 222 NA NA Multiple CPUs Overclocked AMD A4 Micro-6400T APU 1,004 2445 NA NA Power Performance AMD A4 PRO-3340B 1,706 1938 NA NA CPU Mark by AMD A4 PRO-7300B APU 1,481 2097 NA NA Socket Type Cross-Platform AMD A4 PRO-7350B 1,024 2428 NA NA CPU Performance AMD A4-1200 APU 445 2969 NA NA AMD A4-1250 APU 428 2987 NA NA CPU Mega List AMD A4-3300 APU 961 2494 53.40 $18.00* Search Model AMD A4-3300M APU 686 2740 22.86 $29.99* 0 Compare AMD -

Computer Organization and Assembly Language CSC-210 Laboratory

Department of Computer Science CSC-210 Computer Organization and Assembly Language Laboratory Manual, 3rd Edition/2017 Computer Organization and Assembly Language CSC-210 Laboratory Manual 3rd Edition 2017/2018 Name: Number: ٍ :Section Department: 1 Department of Computer Science CSC-210 Computer Organization and Assembly Language Laboratory Manual, 3rd Edition/2017 Table of Contents Lab (1): Computer Anatomy ....................................................................................................... 4 Objectives ............................................................................................................................... 4 What is a Computer? ............................................................................................................... 4 System ..................................................................................................................................... 4 1. Motherboard ............................................................................................................. 5 2. Central Processing Unit (CPU) ...................................................................................... 6 3. Memory .................................................................................................................... 6 4. Video Adapter ............................................................................................................ 7 5. Operating System ...................................................................................................... -

TUF X299 MARK 2 Specifications Summary

TUF X299 MARK 2 Motherboard E12906 First Edition June 2017 Copyright© 2017 ASUSTeK COMPUTER INC. All Rights Reserved. No part of this manual, including the products and software described in it, may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means, except documentation kept by the purchaser for backup purposes, without the express written permission of ASUSTeK COMPUTER INC. (“ASUS”). Product warranty or service will not be extended if: (1) the product is repaired, modified or altered, unless such repair, modification of alteration is authorized in writing by ASUS; or (2) the serial number of the product is defaced or missing. ASUS PROVIDES THIS MANUAL “AS IS” WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OR CONDITIONS OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT SHALL ASUS, ITS DIRECTORS, OFFICERS, EMPLOYEES OR AGENTS BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES (INCLUDING DAMAGES FOR LOSS OF PROFITS, LOSS OF BUSINESS, LOSS OF USE OR DATA, INTERRUPTION OF BUSINESS AND THE LIKE), EVEN IF ASUS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES ARISING FROM ANY DEFECT OR ERROR IN THIS MANUAL OR PRODUCT. SPECIFICATIONS AND INFORMATION CONTAINED IN THIS MANUAL ARE FURNISHED FOR INFORMATIONAL USE ONLY, AND ARE SUBJECT TO CHANGE AT ANY TIME WITHOUT NOTICE, AND SHOULD NOT BE CONSTRUED AS A COMMITMENT BY ASUS. ASUS ASSUMES NO RESPONSIBILITY OR LIABILITY FOR ANY ERRORS OR INACCURACIES THAT MAY APPEAR IN THIS MANUAL, INCLUDING THE PRODUCTS AND SOFTWARE DESCRIBED IN IT. -

Advantech SKY Series Industrial Server Solutions

Regional Service & Customization Centers China Kunshan Taiwan Taipei Netherlands Eindhoven Poland Warsaw USA Milpitas, CA 86-512-5777-5666 886-2-2792-7818 31-40-267-7000 00800-2426-8080 1-408-519-3898 Worldwide Offices Asia Asia Europe Americas Advantech SKY Series Taiwan Japan Netherlands North America Toll Free 0800-777-111 Toll Free 0800-500-1055 Eindhoven 31-40-267-7000 Toll Free 1-888-576-9668 Taipei & IoT Campus 886-2-2792-7818 Tokyo 81-3-6802-1021 Breda 31-76-523-3100 Cincinnati 1-513-742-8895 Taichung 886-4-2372-5058 Osaka 81-6-6267-1887 Milpitas 1-408-519-3898 Industrial Server Solutions Kaohsiung 886-7-392-3600 Nagoya 81-0800-500-1055 Germany Irvine 1-949-420-2500 Nogata 81-949-22-2890 Toll Free 00800-2426-8080/81 Ottawa 1-815-433-5100 China Munich 49-89-12599-0 GPU Server Toll Free 800-810-0345 Korea Düsseldorf 49-2103-97-855-0 Brazil High-Performance, Reliable, and Flexible Beijing 86-10-6298-4346 080-363-9494/5 Toll Free Toll Free 0800-770-5355 IoT Server Shanghai 86-21-3632-1616 82-2-3660-9255 Seoul France São Paulo 55-11-5592-5367 Shenzhen 86-755-8212-4222 Paris 33-1-4119-4666 Carrier-grade Server with Product Longevity Support Chengdu 86-28-8545-0198 Singapore Hong Kong 852-2720-5118 Singapore 65-6442-1000 Mexico Italy Toll Free 1-800-467-2415 Multi-node Server Malaysia Milan 39-02-9544-961 Mexico City 52-55-6275-2727 Kuala Lumpur 60-3-7725-4188 Server Board Penang 60-4-537-9188 UK Newcastle 44-0-191-262-4844 Middle East and Africa Server Chassis London 44-0-870-493-1433 Thailand Israel 072-2410527 Bangkok 66-02-2488306-9 Turkey 90-212-222-0422 Application Case Spain Vietnam Madrid 34-91-668-86-76 Solution Ready Platform Hanoi 84-24-3399-1155 Sweden Indonesia Stockholm 46-0-864-60-500 Jakarta 62-21-751-1939 Poland Australia Warsaw 48-22-31-51-100 Toll Free 1300-308-531 Melbourne 61-3-9797-0100 Russia Moscow 8-800-555-01-50 India St. -

ROG CROSSHAIR VII HERO Specifications Summary

ROG CROSSHAIR VII HERO Motherboard E13835 First Edition February 2018 Copyright © 2018 ASUSTeK COMPUTER INC. All Rights Reserved. No part of this manual, including the products and software described in it, may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means, except documentation kept by the purchaser for backup purposes, without the express written permission of ASUSTeK COMPUTER INC. (“ASUS”). Product warranty or serVice will not be extended if: (1) the product is repaired, modified or altered, unless such repair, modification of alteration is authorized in writing by ASUS; or (2) the serial number of the product is defaced or missing. ASUS PROViDES THIS MANUAL “AS IS” WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OR CONDITIONS OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT SHALL ASUS, ITS DIRECTORS, OFFICERS, EMPLOYEES OR AGENTS BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES (INCLUDING DAMAGES FOR LOSS OF PROFITS, LOSS OF BUSINESS, LOSS OF USE OR DATA, INTERRUPTION OF BUSINESS AND THE LIKE), EVEN IF ASUS HAS BEEN ADViSED OF THE POSSIBILITY OF SUCH DAMAGES ARISING FROM ANY DEFECT OR ERROR IN THIS MANUAL OR PRODUCT. SPECIFICATIONS AND INFORMATION CONTAINED IN THIS MANUAL ARE FURNISHED FOR INFORMATIONAL USE ONLY, AND ARE SUBJECT TO CHANGE AT ANY TIME WITHOUT NOTICE, AND SHOULD NOT BE CONSTRUED AS A COMMITMENT BY ASUS. ASUS ASSUMES NO RESPONSIBILITY OR LIABILITY FOR ANY ERRORS OR INACCURACIES THAT MAY APPEAR IN THIS MANUAL, INCLUDING THE PRODUCTS AND SOFTWARE DESCRIBED IN IT. -

Passmark - CPU Benchmarks - List of Benchmarked Cpus

PassMark - CPU Benchmarks - List of Benchmarked CPUs https://www.cpubenchmark.net/cpu_list.php CPU Mark Rank CPU Name CPU Benchmarks (higher is better) (lower is better) CPU Benchmarks Over 1,000,000 CPUs Benchmarked CPU List Below is an alphabetical list of all CPU types that appear in the charts. Clicking on a specific processor name will take you to the chart it appears in and will highlight it for you. Results for Single CPU Systems and Multiple CPU Systems are listed separately. Find CPU Single CPU Systems Multi CPU Systems Single CPU Systems Last updated on the 11th of June 2021 Column CPU Mark Rank CPU Value Price CPU Name (higher is better) (lower is better) (higher is better) (USD) AMD EPYC 7763 87,767 1 NA NA AMD Ryzen Threadripper PRO 3995WX 86,096 2 15.69 $5,486.99 AMD EPYC 7713 85,887 3 NA NA AMD Ryzen Threadripper 3990X 81,290 4 13.30 $6,110.99 AMD EPYC 7643 77,101 5 NA NA AMD EPYC 7702 71,686 6 8.43 $8,499.00 AMD Ryzen Threadripper 3970X 64,139 7 26.28 $2,440.51 AMD EPYC 7742 64,071 8 8.01 $7,995.94* AMD Ryzen Threadripper PRO 3975WX 61,259 9 22.70 $2,698.99 AMD EPYC 7702P 60,273 10 12.96 $4,650.00* AMD EPYC 7443P 58,896 11 44.05 $1,337.00* AMD EPYC 7R32 58,556 12 NA NA AMD EPYC 7542 56,809 13 13.53 $4,198.95* AMD Ryzen Threadripper 3960X 55,004 14 39.29 $1,399.99 1 z 112 11.06.2021, 11:17 PassMark - CPU Benchmarks - List of Benchmarked CPUs https://www.cpubenchmark.net/cpu_list.php CPU Mark Rank CPU Value Price CPU Name (higher is better) (lower is better) (higher is better) (USD) CPU Mark Rank CPU Name CPU Benchmarks (higher