PAL/NTSC/SECAM Video Decoder with Adaptive PAL/NTSC Comb Filter, VBI-Data Slicer and High Performance Scaler

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Console Comparison

CONSOLE COMPARISON CURRENT INTEGRITY Cybex 50L Console C Console X Console Discover ST Cybex 70T Discover SE3 Discover SE3HD SCREEN 21" 1080p Touch Screen (Tread) 19" 720p Touch Screen (Tread) 21" 1080p Touch Screen (Tread) Display LED LED LED 7" Touch LCD 16" 1080p Touch Screen (Tread, Bikes and Arcs) 16" 1080p Touch Screen (Non-Tread) 16" 720p Touch Screen (Non-Tread) 16" 1080p Touch Screen (Non-Tread) Navigation Membrane buttons Membrane Buttons Membrane Buttons Touch, Tactile Buttons Touch Screen Touch Screen Touch Screen Touch Screen Languages 9 Universal Universal 19 24 24 24 24 Speed, Distance, Distance Climbed, Average Pace, Average Speed, Speed, Incline, Heart Rate (current, average, max), Pace, Elapsed Speed, Incline, Heart Rate (current, average, max), Pace, Elapsed Speed, Incline, Heart Rate (current, average, max), Pace, Elapsed Speed, Incline, Heart Rate (current, average, max), Pace, Elapsed Speed, Incline, Heart Rate, Elapsed Time, Pace, Distance, Distance Display Readouts - Treadmills Speed, Time, Distance, HR, Calories, Incline, Pace Speed, Time, Distance, HR, Calories, Incline Total Cal Burned, Average METs, Average Watts, Average HR, Max Time, Time Remaining, Time in Zone, Time of Day, Distance, Distance Time, Time Remaining, Time in Zone, Time of Day, Distance, Distance Time, Time Remaining, Time in Zone, Time of Day, Distance, Distance Time, Time Remaining, Time in Zone, Time of Day, Distance, Distance Climbed, Calories, Calories/HR HR Climbed, Distance Remaining, Calories, Calories/HR Climbed, Distance Remaining, -

BA(Prog)III Yr 11/04/2020

BA(prog)III yr 11/04/2020 Analog Video • In an analog system, the output of the charge-coupled device (CCD) is processed by the camera into three channels of color information and synchronization pulses (sync) and the signals are recorded onto magnetic tape. • There are several video standards for managing analog CCD output, each dealing with the amount of separation between the components—the more separation of the color information, the higher the quality of the image (and the more expensive the equipment). • If each channel of color information is transmitted as aseparate signal on its own conductor, the signal output is called component (separate red, green, and blue channels), which is the preferred method for higher-quality and professional video work. • Lower in quality is the signal that makes up Separate Video (S-Video), using two channels that carry luminance and chrominance information. The least separation (and thus the lowest quality for a video signal) is composite, when all the signalsare mixed together and carried on a single cable as a composite of the three color channels and the sync signal. • The composite signal yields less-precise color definition, which cannot be manipulated or color-corrected as much as S-Video or component signals. • The analog video and audio signals are written to tape by a spinning recording head that changes the local magnetic properties of the tape’s surface in a series of long diagonal stripes. • Because the head is canted or tilted at a slight angle compared with the path of the tape, it follows a helical (spiral) path, which is called helical scan recording. -

NTE15039 Integrated Circuit VHS/VCR Chroma Signal Proessor for NTSC/PAL/SECAM Systems

NTE15039 Integrated Circuit VHS/VCR Chroma Signal Proessor for NTSC/PAL/SECAM Systems Description: The NTE15039 is a multifunctional IC in a 24–Lead DIP type package that contains VHS VCT chroma signal processing circuitry. Since the package is small and a minimum number of external compo- nents are required, the NTE15039 occupies much less space on the PC board thus facilitating VCR design. The chroma section is made adjustment–free (except REC chroma level) thus streamlining the manufacture of VCRs Features: D Designed for NTSC/PAL/MESECAM Systems D Adjustment–Free Chroma Section (Except REC Chroma Level) D Few External Components Required D LPF Usable for REC/PB D Multifunctional: 2fSC Generator for CCD Drive Function to Select APC Loop Input Signal Passed/Not Passed Through Comb Filter 3rd Lock Protector of VXO Absolute Maximum Ratings: (TA = +25°C unless otherwise specified) Maximum Supply Voltage, VCCmax. 7V Allowable Power Dissipation (TA ≤ +65°C), PDmax. 850mW Operating Temperature Range, Topg . –10° to +65°C Storage Temperature Range, Tstg . –40° to +125°C Recommended Operating Conditions: (TA = +25°C unless otherwise specified) Recommended Supply Voltage, VCC . 5V Operating Voltage Range, VCCop. 4.8 to 5.5V Electrical Characteristics: (TA = +25°C, VCC = 5V unless otherwise specified) Parameter Symbol Test Conditions Min Typ Max Unit REC Current Dissipation ICC(R) 49 62 75 mA REC Output Level VO(R) 75 110 145 mVP–P REC ACC Characteristics ∆VO(R) Input ± 6dB –0.5 ±0.1 +0.5 dB Electrical Characteristics (Cont’d): (TA = +25°C, VCC -

ATSC: Digital Television Update

ATSC: Digital Television Update Robert Graves Advanced Television Systems Committee ITU Interregional Seminar on the Transition from SECAM to Digital TV Broadcasting Kiev, Ukraine November 13, 2000 Advanced Television Systems Committee q Technical Standards for Digital Television (DTV) q DTV Implementation Activities q Membership Organization -- International – Open to all organizations with a related interest – Broad, cross-industry participation • Broadcasters, cable, satellite, computer, movie & telecom service providers • Consumer electronics, computer & professional equipment companies q Over 200 Members – Growing A2 Options for DTV Business Models q HDTV (one or two programs) q HDTV + SDTV (e.g., weather, news, alternative program) q Multiple programs of SDTV q Data services – Program-related or not – Interactive or one-way q Combinations of HDTV, SDTV, data services q Programs or data to mobile receivers? – Severe trade-off against deliverable bit rate q Broadcast to TVs, PCs, or convergence products q Free-to-air vs. pay services q Impact of potential government requirements – Minimum HDTV requirements? G2 DTV CHANNEL ASSIGNMENTS IN THE U.S. (VHF and UHF) Spectrum Efficiency CURRENT NTSC CHANNEL DISTRIBUTION 2-4 5-6 7 - 13 14 - 36 38 - 69 18 12 42 138 192 = DTV CHANNEL ALLOCATION - END OF TRANSITION CORE DTV SPECTRUM 2-4 5-6 7 - 13 14 - 36 38 - 51 52 – 69 (recovered) 18 12 42 138 84 = 294 MHz 108 MHz RECOVERED Progress in DTV Deployment qCurrent requirement: – 120 Stations – 30 Metropolitan Areas 10010101001101001110110 qActual -

Amateur Extra License Class

Amateur Extra License Class 1 Amateur Extra Class Chapter 8 Radio Modes and Equipment 2 1 Modulation Systems FCC Emission Designations and Terms • Specified by ITU. • Either 3 or 7 characters long. • If 3 characters: • 1st Character = The type of modulation of the main carrier. • 2nd Character = The nature of the signal(s) modulating the main carrier. • 3rd Character = The type of information to be transmitted. • If 7 characters, add a 4-character bandwidth designator in front of the 3-character designator. 3 Modulation Systems FCC Emission Designations and Terms • Type of Modulation. N Unmodulated Carrier A Amplitude Modulation R Single Sideband Reduced Carrier J Single Sideband Suppressed Carrier C Vestigial Sideband F Frequency Modulation G Phase Modulation P, K, L, M, Q, V, W, X Various Types of Pulse Modulation 4 2 Modulation Systems FCC Emission Designations and Terms • Type of Modulating Signal. 0 No modulating signal 1 A single channel containing quantized or digital information without the use of a modulating sub-carrier 2 A single channel containing quantized or digital information with the use of a modulating sub-carrier 3 A single channel containing analog information 7 Two or more channels containing quantized or digital information 8 Two or more channels containing analog information X Cases not otherwise covered 5 Modulation Systems FCC Emission Designations and Terms • Type of Transmitted Information. N No information transmitted A Telegraphy - for aural reception B Telegraphy - for automatic reception C Facsimile D Data transmission, telemetry, telecommand E Telephony (including sound broadcasting) F Television (video) W Combination of the above X Cases not otherwise covered 6 3 Modulation Systems FCC Emission Designations and Terms • 3-character designator examples: • A1A = CW. -

Predicting the Future of Broadcasting

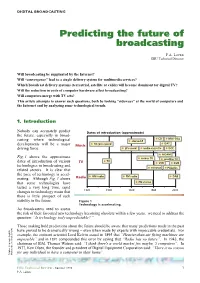

DIGITAL BROADCASTING Predicting the future of broadcasting P.A. Laven EBU Technical Director Will broadcasting be supplanted by the Internet? Will “convergence” lead to a single delivery system for multimedia services? Which broadcast delivery systems (terrestrial, satellite or cable) will become dominant for digital TV? Will the reduction in costs of computer hardware affect broadcasting? Will computers merge with TV sets? This article attempts to answer such questions, both by looking “sideways” at the world of computers and the Internet and by analyzing some technological trends. 1. Introduction Nobody can accurately predict Dates of introduction (approximate) the future, especially in broad- CD Mini-Disc casting where technological stereo LP DAT developments will be a major Music 78 rpm record driving force. LP record audio cassette DCC NICAM Fig. 1 shows the approximate colour TV satellite TV TV dates of introduction of various TV VCR DVB technologies in broadcasting and teletext PALplus related sectors. It is clear that the pace of technology is accel- AM radio FM radio DAB erating. Although Fig. 1 shows Radio that some technologies have FM stereo lasted a very long time, rapid changes in technology mean that 1920 1940 1960 1980 2000 there is little prospect of such stability in the future. Figure 1 Technology is accelerating. As broadcasters need to assess the risk of their favoured new technology becoming obsolete within a few years, we need to address the question: “Is technology truly unpredictable? ” Those making bold predictions about the future should be aware that many predictions made in the past have proved to be dramatically wrong – even when made by experts with impeccable credentials. -

Improved Television Systems: NTSC and Beyond

• Improved Television Systems: NTSC and Beyond By William F. Schreiber After a discussion ofthe limits to received image quality in NTSC and a excellent results. Demonstrations review of various proposals for improvement, it is concluded that the have been made showing good motion current system is capable ofsignificant increase in spatial and temporal rendition with very few frames per resolution. and that most of these improvements can be made in a second,2 elimination of interline flick er by up-conversion, 3 and improved compatible manner. Newly designed systems,for the sake ofmaximum separation of luminance and chromi utilization of channel capacity. should use many of the techniques nance by means of comb tilters. ~ proposedfor improving NTSC. such as high-rate cameras and displays, No doubt the most important ele but should use the component. rather than composite, technique for ment in creating interest in this sub color multiplexing. A preference is expressed for noncompatible new ject was the demonstration of the Jap systems, both for increased design flexibility and on the basis oflikely anese high-definition television consumer behaL'ior. Some sample systems are described that achieve system in 1981, a development that very high quality in the present 6-MHz channels, full "HDTV" at the took more than ten years.5 Orches CCIR rate of 216 Mbits/sec, or "better-than-35mm" at about 500 trated by NHK, with contributions Mbits/sec. Possibilities for even higher efficiency using motion compen from many Japanese companies, im sation are described. ages have been produced that are comparable to 35mm theater quality. -

Secam Decoder

MITSUBISHI LINEAR INTEGRATED CIRCUIT M52325AP SECAM DECODER [GENERAL DESCRIPTION] pin configuration The M52325AP is designed for SECAM chrominance decoding.The IC should preferably be used in conjunction with PAL / NTSC signal processor M52340SP and the fref / IDENT 1 16 CVBS IN switched capacitor baseband delay line. It consists of a bell filter,a demodulator and an identification BELL OUT 2 15 SAND IN circuit. The IC needs no adjustment and few external Vcc 3 M52325AP 14 BLACK ADJ. R components are required. A signal with highly stable BAND GAP 4 13 PLL auto 1 reference frequency is required for the calibration, and a three - level sandcastle pulse for blanking and burst gating. SACAM KILLER OUT 5 12 PLL auto2 GND 6 11 BLACK ADJ. B BELL ref. 7 10 - (B - Y ) OUT [FEATURES] PLL ref. 8 9 - (R - Y ) OUT • Fully integrated filters 16 PIN DIL PLASTIC PACKAGE • No adjustment • Few external compornents • Used with a switched capacitor baseband delay line [STRUCRURE] [APPLICATION] Bipolar Silicon Monolithic IC SECAM Color Television 16 PIN DIL PLASTIC PACKAGE [QUICK REFERENCE DATA] SYMBOL PARAMETER MIN. TYP. MAX. UNIT positive power supply Vcc pin3 7.5 8.0 8.5 V Icc supply current pin3 18 24 30 mA input dynamic range VDR - 1.0 1.4 Vp-p pin16 -(R-Y) output voltage amplitude VR-Y 0.85 1.00 1.15 Vp-p (peak to peak value) ;pin9 -(B-Y) output voltage amplitude VB-Y (peak to peak value) ;pin10 1.10 1.24 1.43 Vp-p MITSUBISHI 1 - 13 MITSUBISHI LINEAR INTEGRATED CIRCUIT M52325AP SECAM DECODER Vcc=8.0V 0.1µ F + BELL PLL PLL OUT 22µF auto2 auto1 0.1µF 2 12 13 3 BAND GAP BANDGAP 4 CVBS IN BELL ACC AMP PLL 16 FILTER B-Y 10 -(B-Y) BELL OUTPUT OUT ref. -

AVA 22D Data Sheet

DATA SHEET AVA 22d AUDIO / VIDEO ALIGNMENT DELAY SENSITIVITY SENSITIVITY STORE LINK BYPASS MEMORY MODE CHANNEL 1 BYPASS MEMORY MODE CHANNEL 2 1-10 dBV 2 -10 dBV AB AB -8 -8 -4 -12 -4 -12 NTSC NTSC AVA 22d 0 -16 0 -16 FIELDS FIELDS AUDIO / VIDEO ALIGNMENT +4 -20 +4 -20 6.5 6.5 DELAY dBu dBu CH 2 RECALL PAL RECALL PAL COPIES EDIT SECAM EDIT SECAM SIGNAL CLIP SIGNAL CLIP CH 1 FRAMES FRAMES General Description The Rane AVA 22d is a fully balanced two Input, two Out- without risk of changing them. Internal jumpers are available to put Audio / Video Alignment Delay providing a range of 0.0 to enable or disable Bypass while in Front Panel Lockout mode. The 9.5 NTSC or PAL/SECAM frames on each Output. 24-bit audio default setting of these jumpers disables Bypass in Front Panel converters provide excellent sound quality. Lockout mode. Each Output has two nonvolatile Memories (no batteries Independent bypass relays provide a fail safe, hard-wired required), A and B, for easy access to previously stored Delay bypass in case of power loss. values. Remote Recall screw terminals on the rear accept external The AVA 22d is a unity gain device with Sensitivity controls configuration switches, permitting independent remote recall of to provide proper internal levels for the audio converters. If the the Memories. input signal is nominally +4 dBu, set the Sensitivity control fully The AVA 22d features XLR Inputs and Outputs, and is counter clockwise (+4 dBu). For those unable to touch a cable CE certified for emissions. -

SAA7114 PAL/NTSC/SECAM Video Decoder with Adaptive PAL/NTSC Comb filter, VBI Data Slicer and High Performance Scaler Rev

SAA7114 PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC comb filter, VBI data slicer and high performance scaler Rev. 03 — 17 January 2006 Product data sheet 1. General description The SAA7114 is a video capture device for applications at the image port of Video Graphics Array (VGA) controllers. The SAA7114 is a combination of a two-channel analog preprocessing circuit including source selection, anti-aliasing filter and Analog-to-Digital Converter (ADC), an automatic clamp and gain control, a Clock Generation Circuit (CGC), a digital multistandard decoder containing two-dimensional chrominance/luminance separation by an adaptive comb filter and a high performance scaler, including variable horizontal and vertical up and downscaling and a brightness, contrast and saturation control circuit. It is a highly integrated circuit for desktop video and similar applications. The decoder is based on the principle of line-locked clock decoding and is able to decode the color of PAL, SECAM and NTSC signals into ITU 601 compatible color component values. The SAA7114 accepts CVBS or S-video (Y/C) as analog inputs from TV or VCR sources, including weak and distorted signals. An expansion port (X port) for digital video (bidirectional half duplex, D1 compatible) is also supported to connect to MPEG or a video phone codec. At the so called image port (I port) the SAA7114 supports 8-bit or 16-bit wide output data with auxiliary reference data for interfacing to VGA controllers. The target application for the SAA7114 is to capture and scale video images, to be provided as a digital video stream through the image port of a VGA controller, for display via the frame buffer of the VGA, or for capture to system memory. -

Options of Enhanced Secam Tv Transmission System

Gofaizen O.V. (UKRAINE, UNIIRT) OPTIONS OF ENHANCED SECAM TV TRANSMISSION SYSTEM Introduction The questions of transition from analogue to digital TV in countries, using analogue TV SECAM transmission system are discussed in this report with consideration of its enhancement in accor- dance with conception of EQTV systems. The transition period is characterized with that in its beginning infrastructure and park of TV sets are analogue. At the beginning of transition period TV broadcasting is mainly analogue, and a number of digital TV sets is minimal, and apparently for a long time analogue and digital TV will co-exist. Simultaneously with implementation of digital TV analogue TV has to be supported and enhanced [1]. The issues of compatibility of new digital and old analogue TV are extremely important, and here the main consideration is attended to them. 1 The position of analogue enhanced quality television in the period of transition to digi- tal television We have to take into consideration that the main event of the present in television is the transition to digital TV. Nevertheless, this transition may continue in some countries for long time enough. All this depends on many factors – relationship between the cost of digital sets (tuners, set top boxes) and of analog ones, real term for change from analog to digital infrastructure and the affordablence of this change, purchasing power of viewers community, presence and condition of used equipment. It is quite possible, that in some coun- tries this transition would come in a quite short time, in others this transition would continue for decades. -

NTE7150 Integrated Circuit Video, Chroma, and Sync. Signal

NTE7150 Integrated Circuit Video, Chroma, and Sync. Signal Processing Circuit for PAL/NTSC/SECAM System Color Televisions Description: The NTE7150 is an integrated circuit in a 64–Lead SIP type package designed for PAL/NTSC/SECAM system color televisions involving video, chroma, and sync. signal processing circuits. The video section contains a high–performance picture quality emphasis circuit, the chroma section contains a PAL/NTSC/SECAM system automatic identification circuit, and the sync. section contains a 50/60Hz automatic identification circuit. The PAL/SECAM demodulating circuit uses a baseband signal processing system, providing an adjustment–free demodulating circuit. User control functions, system switching, etc. are controlled via the I2C bus. Features: Video Section D Sharpness Control with Internal Delay Lines D Black Stretching Circuit D YNR D Variable DC Restoration Ratio D Gamma (g) Contrast Correction Chroma Section D PAL/SECAM baseband Demodulation System D Automatic Srystal Frequency Identification (4.43MHz/3.58MHz/M, N–PAL) D Automatic Chroma System Identification (PAL/NTSC/SECAM) D PLL SECAM Adjustment–Free Demodulation Circuit without and Tank Coils D Built–In SECAM BELL Filter Sync. Section D Adjnustment–Free Horizontal and Vertical Oscillation Circuits based on Countdown System D Automatic Vertical Frequency Identification (50/60Hz) Absolute Maximum Ratings: (TA = +25°C unless otherwise specified) Supply Voltage, VCC . 15V Power Dissipation, PDmax. 2660mW Derate Above 25°C. 21.2mW/°C Input Signal Amplitude, ein