Tps2583x-Q1 USB Type-C and BC1.2 5-V 3.5-A Output, 36-V Input Synchronous Step-Down DC/DC Regulator with Cable Compensation

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

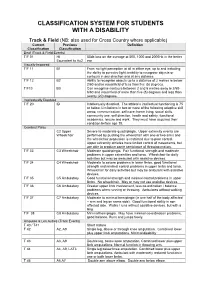

Disability Classification System

CLASSIFICATION SYSTEM FOR STUDENTS WITH A DISABILITY Track & Field (NB: also used for Cross Country where applicable) Current Previous Definition Classification Classification Deaf (Track & Field Events) T/F 01 HI 55db loss on the average at 500, 1000 and 2000Hz in the better Equivalent to Au2 ear Visually Impaired T/F 11 B1 From no light perception at all in either eye, up to and including the ability to perceive light; inability to recognise objects or contours in any direction and at any distance. T/F 12 B2 Ability to recognise objects up to a distance of 2 metres ie below 2/60 and/or visual field of less than five (5) degrees. T/F13 B3 Can recognise contours between 2 and 6 metres away ie 2/60- 6/60 and visual field of more than five (5) degrees and less than twenty (20) degrees. Intellectually Disabled T/F 20 ID Intellectually disabled. The athlete’s intellectual functioning is 75 or below. Limitations in two or more of the following adaptive skill areas; communication, self-care; home living, social skills, community use, self direction, health and safety, functional academics, leisure and work. They must have acquired their condition before age 18. Cerebral Palsy C2 Upper Severe to moderate quadriplegia. Upper extremity events are Wheelchair performed by pushing the wheelchair with one or two arms and the wheelchair propulsion is restricted due to poor control. Upper extremity athletes have limited control of movements, but are able to produce some semblance of throwing motion. T/F 33 C3 Wheelchair Moderate quadriplegia. Fair functional strength and moderate problems in upper extremities and torso. -

2007 Lake Monitoring Report Mecklenburg County Water Quality Program SWIM Phase I Part 2-CO

2007 Lake Monitoring Report Mecklenburg County Water Quality Program SWIM Phase I Part 2-CO Prepared by: David Buetow Final Report for FY2007-2008 PURPOSE AND BACKGROUND The Mecklenburg County Water Quality Program (MCWQP) has an ongoing program to monitor the water quality in the three Catawba Lakes bordering the county: Lake Norman, Mountain Island Lake and Lake Wylie. Samples are also routinely collected at the two water bodies in the northern end of Mecklenburg County cut off from Lake Norman proper by I-77: Lake Cornelius and Lake Davidson. Data collected from all lake sites are used to screen for environmental problems using MCWQP Action and Watch levels for various pollutants and also to rate the overall water quality at sampling locations in the lakes using a water quality index. Additional objectives are to describe seasonal trends and address spatial variability in the data. This report presents the lake monitoring data for the calendar year 2007 ACTIVITIES AND METHODS Regular monthly lake sampling was conducted at seven locations in Lake Norman and one location each on Lake Cornelius and Lake Davidson (Appendix A), ten locations in Mountain Island Lake (Appendix B) and eight sampling locations in Lake Wylie (Appendix C). In May 2007, the sampling program was changed in Lake Wylie to add several new cove monitoring sites. This resulted in an increase in regular sampling sites in Lake Wylie from eight to thirteen (Appendix D). Lakes Norman, Wylie and Mountain Island were sampled monthly from May through September and every other month during the rest of the year, i.e. -

Throwing Distance and Competitive Performance of Boccia Players

J. Phys. Ther. Sci. 32: 574–577, 2020 The Journal of Physical Therapy Science Original Article Throwing distance and competitive performance of Boccia players Masataka Kataoka, PhD1)*, Kuniharu Okuda, PhD1), Akira Iwata, PhD1), Shuji Imura, MS1), Kosuke Yahagi, MS1), Yohei Matsuo2) 1) Graduate School of Comprehensive Rehabilitation, Osaka Prefecture University: 3-7-30 Habikino, Habikino-city, Osaka 583-8555, Japan 2) Fukushima Rehabilitation Center for Children, Japan Abstract. [Purpose] This study aimed to clarify the relationship between throwing distance and competitive performance in Boccia players in order to establish a training program based on this evidence. [Participants and Methods] In total, 40 athletes, who competed in the Japan Boccia Championships and are certified players of the Japan Boccia Association, participated in the study. Participants threw the Boccia ball as far as possible, and throw- ing distances were compared between certified players (Group I, n=8), those who participated in the final round (Group II, n=9), and those who lost in the preliminary round (Group III, n=23). [Results] The maximum throwing distances were 16.38 ± 5.17 m (Group I), 10.67 ± 2.66 m (Group II), and 8.34 ± 2.73 m (Group III). Group I threw the ball significantly farther than Groups II and III. [Conclusion] Boccia is a target sport and throwing farther distances requires more effort. In addition, being able to throw at a longer distance means that Boccia players can throw a stronger ball and use this for various tactics. The results of this study suggest that long-distance throwing training would be effective in improving the competitive performance of Boccia players. -

Classification Made Easy Class 1

Classification Made Easy Class 1 (CP1) The most severely disabled athletes belong to this classification. These athletes are dependent on a power wheelchair or assistance for mobility. They have severe limitation in both the arms and the legs and have very poor trunk control. Sports Available: • Race Runner (RR1) – using the Race Runner frame to run, track events include 100m, 200m and 400m. • Boccia o Boccia Class 1 (BC1) – players who fit into this category can throw the ball onto the court or a CP2 Lower who chooses to push the ball with the foot. Each BC1 athlete has a sport assistant on court with them. o Boccia Class 3 (BC3) – players who fit into this category cannot throw the ball onto the court and have no sustained grasp or release action. They will use a “chute” or “ramp” with the help from their sport assistant to propel the ball. They may use head or arm pointers to hold and release the ball. Players with a impairment of a non cerebral origin, severely affecting all four limbs, are included in this class. Class 2 (CP2) These athletes have poor strength or control all limbs but are able to propel a wheelchair. Some Class 2 athletes can walk but can never run functionally. The class 2 athletes can throw a ball but demonstrates poor grasp and release. Sports Available: • Race Runner (RR2) - using the Race Runner frame to run, track events include 100m, 200m and 400m. • Boccia o Boccia Class 2 (BC2) – players can throw the ball into the court consistently and do not need on court assistance. -

Carbonaceous Aerosol Microphysics

Atmos. Chem. Phys. Discuss., 10, 4543–4592, 2010 Atmospheric www.atmos-chem-phys-discuss.net/10/4543/2010/ Chemistry ACPD © Author(s) 2010. This work is distributed under and Physics 10, 4543–4592, 2010 the Creative Commons Attribution 3.0 License. Discussions This discussion paper is/has been under review for the journal Atmospheric Chemistry Carbonaceous and Physics (ACP). Please refer to the corresponding final paper in ACP if available. aerosol microphysics S. E. Bauer et al. A global modeling study on Title Page carbonaceous aerosol microphysical Abstract Introduction Conclusions References characteristics and radiative forcing Tables Figures S. E. Bauer1,2, S. Menon3, D. Koch1,2, T. C. Bond4, and K. Tsigaridis1 J I 1NASA Goddard Institute for Space Studies, New York, NY, USA J I 2The Earth Institute, Columbia University, New York, NY, USA 3Lawrence Berkeley National Laboratory, Berkeley, CA, USA Back Close 4University of Illinois, Urbana-Champaign, IL, USA Full Screen / Esc Received: 20 January 2010 – Accepted: 8 February 2010 – Published: 15 February 2010 Correspondence to: S. E. Bauer ([email protected]) Printer-friendly Version Published by Copernicus Publications on behalf of the European Geosciences Union. Interactive Discussion 4543 Abstract ACPD Recently, attention has been drawn towards black carbon aerosols as a short-term cli- mate warming mitigation candidate. However the global and regional impacts of the 10, 4543–4592, 2010 direct, cloud-indirect and semi-direct forcing effects are highly uncertain, due to the 5 complex nature of aerosol evolution and the way that mixed, aged aerosols interact Carbonaceous with clouds and radiation. A detailed aerosol microphysical scheme, MATRIX, em- aerosol microphysics bedded within the GISS climate model is used in this study to present a quantitative assessment of the impact of microphysical processes involving black carbon, such as S. -

List Biathlon Middle Distance

BIATHLON MIDDLE DISTANCE START LIST As of 27 JAN 2018 NPC Sport Start IPCNS WC Bib Name Code Class % Time S1 S2 S3 S4 T Points Points Time Women Middle,Visually Impaired 1 REMIZOVA Elena NPA B3 100 09:30:30 111.04 320 Guide: TOKAREV Andrei 2 GALITSYNA Marina NPA B1 88 09:31:00 106.81 223 Guide: PIROGOV Maksim 3 HOSCH Vivian GER B1 88 09:31:30 91.68 280 Guide: SCHILLINGER F 4 RUBANOVSKA Natalia UKR B2 99 09:32:00 70.17 85 Guide: NESTERENKO Lada 5 KLUG Clara GER B1 88 09:32:30 13.64 280 Guide: HARTL Martin 6 SHYSHKOVA Oksana UKR B2 99 09:33:00 0.00 90 Guide: KAZAKOV Vitaliy 7 LYSOVA Mikhalina (WL) NPA B2 99 09:33:30 0.00 500 Guide: IVANOV Alexey Men Middle,Visually Impaired 11 KANAFIN Kairat KAZ B2 99 09:40:30 204.91 Guide: ZHDANOVICH Anton 12 DUBOIS Thomas FRA B1 88 09:41:00 168.61 126 Guide: SAUVAGE Bastien 13 CHOI Bogue KOR B3 100 09:41:30 162.70 65 Guide: KIM Hyunwoo 14 UDALTSOV Vladimir NPA B3 100 09:42:00 150.03 137 Guide: BOGACHEV Ruslan 15 POVAROV Nikita NPA B3 100 09:42:30 149.93 206 Guide: ELISEEV Pavel 16 PONOMAREV Oleg NPA B2 99 09:43:00 137.80 32 Guide: ROMANOV Andrei 17 GARBOWSKI Piotr POL B3 100 09:43:30 135.49 69 Guide: TWARDOWSKI J 18 ARTEMOV Aleksandr NPA B1 88 09:44:00 125.38 209 Guide: CHEREPANOV Ilia 19 MAKHOTKIN Oleksandr UKR B3 100 09:44:30 124.74 16 Guide: NIKULIN Denys 20 HOLUB Yury BLR B3 100 09:45:00 82.45 45 Guide: BUDZILOVICH D 21 POLUKHIN Nikolai NPA B2 99 09:45:30 73.45 345 Guide: BEREZIN Eduard 22 CHALENCON Anthony FRA B1 88 09:46:00 22.36 133 Guide: VALVERDE Simon 23 LUK'YANENKO Vitaliy UKR B3 100 09:46:30 -

On Complexes Equivalent to S3-Bundles Over S4

ON COMPLEXES EQUIVALENT TO S3-BUNDLES OVER S4 NITU KITCHLOO AND KRISHNAN SHANKAR Introduction S3-bundles over S4 have played an important role in topology and geom- etry since Milnor showed that the total spaces of such bundles with Euler class ±1 are manifolds homeomorphic to S7 but not always diffeomorphic to it. In 1974, Gromoll and Meyer exhibited one of these spheres (a gen- erator in the group of homotopy 7-spheres) as a double coset manifold i.e. a quotient of Sp(2) hence showing that it admits a metric of nonnegative curvature (cf. [6]). Until recently, this was the only exotic sphere known to admit a metric of nonnegative sectional curvature. Then in [7], K. Grove and W. Ziller constructed metrics of nonnegative curvature on the total space of S3-bundles over S4. They also asked for a classification of these bundles up to homotopy equivalence, homeomorphism and diffeomorphism. These questions have been addressed in many papers such as [12], [11], [15] and more recently in [3]. In this paper we attempt to fill the gap in the previous papers; we consider the problem of determining when a given CW complex is homotopy equivalent to such a bundle. The problem was motivated by [7]: the Berger space, Sp(2)/ Sp(1), is a 7-manifold that has the cohomology ring of an S3-bundle over S4, but does it admit the structure of such a bundle? The fact that it cannot be a principal S3-bundle over S4 is straightforward and is proved in [7]. Let X be a simply connected CW complex with integral cohomology groups given by Hi(X)= Z if i = 0, 7 (1) = Zn if i = 4 where n is some fixed non-zero integer. -

(VA) Veteran Monthly Assistance Allowance for Disabled Veterans

Revised May 23, 2019 U.S. Department of Veterans Affairs (VA) Veteran Monthly Assistance Allowance for Disabled Veterans Training in Paralympic and Olympic Sports Program (VMAA) In partnership with the United States Olympic Committee and other Olympic and Paralympic entities within the United States, VA supports eligible service and non-service-connected military Veterans in their efforts to represent the USA at the Paralympic Games, Olympic Games and other international sport competitions. The VA Office of National Veterans Sports Programs & Special Events provides a monthly assistance allowance for disabled Veterans training in Paralympic sports, as well as certain disabled Veterans selected for or competing with the national Olympic Team, as authorized by 38 U.S.C. 322(d) and Section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program, VA will pay a monthly allowance to a Veteran with either a service-connected or non-service-connected disability if the Veteran meets the minimum military standards or higher (i.e. Emerging Athlete or National Team) in his or her respective Paralympic sport at a recognized competition. In addition to making the VMAA standard, an athlete must also be nationally or internationally classified by his or her respective Paralympic sport federation as eligible for Paralympic competition. VA will also pay a monthly allowance to a Veteran with a service-connected disability rated 30 percent or greater by VA who is selected for a national Olympic Team for any month in which the Veteran is competing in any event sanctioned by the National Governing Bodies of the Olympic Sport in the United State, in accordance with P.L. -

Official Rules

2018 Willamette Valley Youth Football & Cheer OFFICIAL RULES Page 1 Willamette Valley Youth Football & Cheer Table of Contents Part I – The WVYFC Program ............................................................... 5 Article 1: Members Code of Conduct ............................................. 5 Part II – WVYFC Structure .................................................................... 7 Part III – Regulations ............................................................................ 7 Article 1: Authority of League ......................................................... 7 Article 2: Boundaries ....................................................................... 7 Article 3: Coaches Requirements .................................................... 8 Article 4: Registration ..................................................................... 8 Article 5: Formation of Teams ........................................................ 9 Article 6: Mandatory Cuts ............................................................. 10 Article 7: Voluntary Cuts ............................................................... 10 Article 8: Certification ................................................................... 10 Article 9: Retention of Eligibility ................................................... 10 Article 10: No All Stars .................................................................. 10 Article 11: Awards ......................................................................... 11 Article 12: Practice (Definition & Date -

Cryo-EM Structures of Respiratory Bc1-Cbb3 Type CIII2CIV Super-Complex and Electronic Communication Between the Complexes

Cryo-EM Structures of Respiratory bc1-cbb3 type CIII2CIV Super-complex and Electronic Communication Between the Complexes Stefan Steimle1, Trevor VanEeuwen2, Yavuz Ozturk1, #, Hee Jong Kim2, Merav Braitbard3, Nur Selamoglu1, Benjamin A. Garcia4, Dina Schneidman-Duhovny3, Kenji Murakami4,* and Fevzi Daldal1,* 1Department of Biology, University of Pennsylvania, Philadelphia, PA, 19104; 2Biochemistry and Molecular Biophysics Graduate Group, Perelman School of Medicine, University of Pennsylvania, Philadelphia, PA 19104; #Institute of Biochemistry and Molecular Biology, Faculty of Medicine, Albert Ludwigs University of Freiburg, 79104 Freiburg, Germany; 3School of Computer Science and Engineering, Institute of Life Sciences, The Hebrew University of Jerusalem, Jerusalem, 9190401, Israel and 4Department of Biochemistry and Biophysics, Perelman School of Medicine, University of Pennsylvania, Philadelphia, PA 19104 Running title: Bacterial respiratory cytochrome bc1-cbb3 supercomplex Key words: cytochrome bc1 or Complex III; Cytochrome cbb3 oxidase or Complex IV; respiratory super-complex; electron carrier cytochrome c; membrane-anchored cytochrome cy; soluble cytochrome c2; Rhodobacter capsulatus; respiratory electron transport chain *Corresponding authors: Fevzi Daldal: [email protected] Phone: +1 215 898-4394 Kenji Murakami: [email protected] Phone: +1 215 573-1125 1 Methods Bacterial strains and growth conditions Bacterial strains and plasmids used are listed in Table S1. LB medium supplemented as appropriate with ampicillin, gentamicin, kanamycin or tetracycline at 100, 12, 50 or 12.5 μg/mL, respectively, was used for growing E. coli strains at 37 °C (Darrouzet and Daldal, 2002). R. capsulatus strains were grown chemoheterotrophically under semi-aerobic/dark conditions at 35 °C on enriched (MPYE) medium, supplemented as needed with gentamicin, kanamycin, spectinomycin, or tetracycline at 3, 10, 10 or 2.5 μg/mL, respectively (Davidson et al., 1992). -

The Paralympic Athlete Dedicated to the Memory of Trevor Williams Who Inspired the Editors in 1997 to Write This Book

This page intentionally left blank Handbook of Sports Medicine and Science The Paralympic Athlete Dedicated to the memory of Trevor Williams who inspired the editors in 1997 to write this book. Handbook of Sports Medicine and Science The Paralympic Athlete AN IOC MEDICAL COMMISSION PUBLICATION EDITED BY Yves C. Vanlandewijck PhD, PT Full professor at the Katholieke Universiteit Leuven Faculty of Kinesiology and Rehabilitation Sciences Department of Rehabilitation Sciences Leuven, Belgium Walter R. Thompson PhD Regents Professor Kinesiology and Health (College of Education) Nutrition (College of Health and Human Sciences) Georgia State University Atlanta, GA USA This edition fi rst published 2011 © 2011 International Olympic Committee Blackwell Publishing was acquired by John Wiley & Sons in February 2007. Blackwell’s publishing program has been merged with Wiley’s global Scientifi c, Technical and Medical business to form Wiley-Blackwell. Registered offi ce: John Wiley & Sons, Ltd, The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, UK Editorial offi ces: 9600 Garsington Road, Oxford, OX4 2DQ, UK The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, UK 111 River Street, Hoboken, NJ 07030-5774, USA For details of our global editorial offi ces, for customer services and for information about how to apply for permission to reuse the copyright material in this book please see our website at www.wiley.com/wiley-blackwell The right of the author to be identifi ed as the author of this work has been asserted in accordance with the UK Copyright, Designs and Patents Act 1988. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, except as permitted by the UK Copyright, Designs and Patents Act 1988, without the prior permission of the publisher. -

Lecture 3: MIPS Instruction Set

Lecture 3: MIPS Instruction Set • Today’s topic: More MIPS instructions Procedure call/return • Reminder: Assignment 1 is on the class web-page (due 9/7) 1 Memory Operands • Values must be fetched from memory before (add and sub) instructions can operate on them Load word Register Memory lw $t0, memory-address Store word Register Memory sw $t0, memory-address How is memory-address determined? 2 Memory Address • The compiler organizes data in memory… it knows the location of every variable (saved in a table)… it can fill in the appropriate mem-address for load-store instructions int a, b, c, d[10] … Memory Base address 3 Immediate Operands • An instruction may require a constant as input • An immediate instruction uses a constant number as one of the inputs (instead of a register operand) addi $s0, $zero, 1000 # the program has base address # 1000 and this is saved in $s0 # $zero is a register that always # equals zero addi $s1, $s0, 0 # this is the address of variable a addi $s2, $s0, 4 # this is the address of variable b addi $s3, $s0, 8 # this is the address of variable c addi $s4, $s0, 12 # this is the address of variable d[0] 4 Memory Instruction Format • The format of a load instruction: destination register source address lw $t0, 8($t3) any register a constant that is added to the register in brackets 5 Example Convert to assembly: C code: d[3] = d[2] + a; Assembly: # addi instructions as before lw $t0, 8($s4) # d[2] is brought into $t0 lw $t1, 0($s1) # a is brought into $t1 add $t0, $t0, $t1 # the sum is in $t0 sw $t0, 12($s4)