CMOS Signal Synthesizers for Emerging RF-To-Optical Applications Jahnavi Sharma

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

BTN-0040 the BTN-0040 Is Constructed Using a Custom-Made, Resonance-Free Conical Inductor to Achieve Extremely Broadband Performance

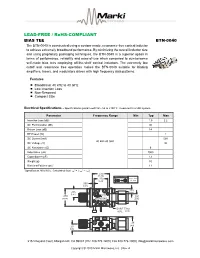

LEAD-FREE / RoHS-COMPLIANT BIAS TEE BTN-0040 The BTN-0040 is constructed using a custom-made, resonance-free conical inductor to achieve extremely broadband performance. By minimizing the overall inductor size and using proprietary packaging techniques, the BTN-0040 is a superior option in terms of performance, reliability and ease-of-use when compared to cumbersome self-made bias tees employing off-the-shelf conical inductors. The extremely low cutoff and resonance free operation makes the BTN-0040 suitable for biasing amplifiers, lasers, and modulators driven with high frequency data patterns. Features Broadband: 40 kHz to 40 GHz Low Insertion Loss Non-Resonant Compact Size Electrical Specifications - Specifications guaranteed from -55 to +100°C, measured in a 50Ω system. Parameter Frequency Range Min Typ Max Insertion Loss (dB) 1.5 2.2 DC Port Isolation (dB) 30 Return Loss (dB) 14 RF Power (W) 1 DC Current (mA) 500 40 kHz-40 GHz DC Voltage (V) 30 DC Resistance (Ω) 6 Inductance (uH) 1000 Capacitance (uF) 1.1 Weight (g) 10 Risetime/Falltime (ps)1 11 1 2 2 2 Specified as 90%/10%. Calculated from bt = (out – in ) .470 [11.94] PROJECTION .370 XXX=±.005 INCH XX=±.02 [9.40] [MM] .050 [1.27] .135 .235 [3.43] [5.97] .470 .200 [11.94] BTN0040 [5.08] Ø.067 Thru 4 PL [1.70] .39 .20 [9.9] [5.0] 215 Vineyard Court, Morgan Hill, CA 95037 | Ph: 408.778.4200 | Fax 408.778.4300 | [email protected] Copyright © 2019 Marki Microwave, Inc. | Rev. A BIAS TEE BTN-0040 Page 2 Schematic RF RF+DC DC Application Examples Fig. -

Wideband Bias Tee Gary W

Wideband Bias Tee Gary W. Johnson, WB9JPS 11-8-08 Bias tees are useful for injecting DC bias to a device under test while isolating an instrument from any DC offset. For instance, you may be applying a bias to the base of a transistor while using a network analyzer to measure S parameters. Or, when testing a modulated laser diode, a DC operating current is required while an ac modulation rides on top of that. Conceptually, the simplest bias tee is just a coupling capacitor and an inductor, and is in effect a diplexer. For real-world components, the big shortcoming is inductor performance, especially self-resonance. If you are only interested in a narrow band of frequencies (say, one decade), the solution is indeed a simple LC network, and is no different than an RF choke and coupling capacitor on the output of an RF amplifier. But wideband applications—covering multiple decades in frequency—are more difficult and this is the performance we seek for test and measurement applications. One solution is to design a series of damped lowpass filter sections where each inductor is only required to operate over a little more than one decade of frequency. Damping is very important and requires experimentation. With no damping, return loss and isolation exhibit large undesired deviations at many frequencies as you’ll see later. A side effect of those large deviations is poor time domain response. If you want to use your bias tee to transmit fast digital pulses, you need to achieve smooth frequency-domain behavior, which typically translates into good pulse fidelity. -

Broadband Chokes for Bias Tee Applicationsdoc 1193

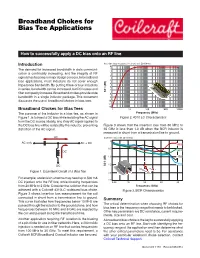

Broadband Chokes for Bias Tee Applications How to successfully apply a DC bias onto an RF line Insertion loss measured in shunt (ref: 50 Ohms) Introduction 0 The demand for increased bandwidth in data communi- 1 cation is continually increasing, and the integrity of RF 2 signals has become a major design concern. In broadband 3 bias applications, most inductors do not cover enough 4 5 impedance bandwidth. By putting three or four inductors 6 in series, bandwidth can be increased, but DC losses and 7 (dB) S21 filter complexity increase. Broadband chokes provide wide 8 bandwidth in a single inductor package. This document 9 discusses the use of broadband chokes in bias tees. 10 11 12 Broadband Chokes for Bias Tees 1 10 100 1000 10000 The purpose of the inductor in a bias tee, as shown in Frequency (MHz) Figure 1, is to inject a DC bias while isolating the AC signal Figure 2. 4310 LC Characteristics from the DC source. Ideally, any stray AC signal applied to the DC bias line will be isolated by the inductor, preventing Figure 3 shows that the insertion loss from 50 MHz to distortion of the AC signal. 35 GHz is less than 1.0 dB when the BCR inductor is measured in shunt from a transmission line to ground. AC Insertion loss (ref: 50 Ohms) 0 AC only AC + DC -652 0.5 DC -531 1.0 -122 1.5 -802 DC S21 (dB) Figure 1. Equivalent Circuit of a Bias Tee 2.0 For example, a television antenna may need up to 500 mA 2.5 DC injected onto the RF line, while blocking frequencies 0.05 10 20 30 40 from 20 MHz to 2 GHz. -

Application Note AN-1E Copyright November, 2000

Application Note AN-1e Copyright November, 2000 Broadband Coaxial Bias Tees James R Andrews, PhD, IEEE Fellow frequency cutoffs down to ultrasonic frequencies of tens of kHz or lower Figure 1 shows the basic schematic diagrams of the two most common bias tee designs Capacitor C is a DC block installed in the center conductor of the 50 Ohm coaxial line It prevents the DC power from flowing out the AC port For low-current applications, such as biasing photodiodes, a resistor R is used to provide the connection between the DC input and the coaxial center conductor To avoid loading Bias Tees are coaxial components that are used whenever the coax line, the resistor value is chosen to be much greater a source of DC power must be connected to a coaxial cable than the coax impedance For higher-current applications When properly designed, the bias tee does not affect the AC in which the potential drop across R or the power dissipated or RF transmission through the coaxial cable The usual in R would be too great, it is necessary to instead use an application is to provide a means of powering an active device inductor such as a transistor, laser diode or photodiode Other uses would be to provide power to operate remotely located coaxial relays or amplifiers, or to transmit low frequency analog or digital signals on the same coax cable along with RF signals Bias tees have been around and used for a long time There are several microwave and RF manufacturers that have built bias tees for many years Most of these tees were designed only for specific -

High-Power T/R Circuits for a Multichannel VHF/UHF/HF Ice Imaging Radar by Syed Faiz Ahmed Submitted to the Graduate Degree

High-Power T/R circuits for a Multichannel VHF/UHF/HF Ice Imaging Radar By Syed Faiz Ahmed Submitted to the graduate degree program in Electrical Engineering and Computer Science and the Graduate Faculty of the University of Kansas in partial fulfillment of the requirements for the degree of Master of Science. ________________________________ Chairperson Dr. Carlton Leuschen ________________________________ Dr. Fernando Rodriguez - Morales ________________________________ Dr. Christopher Allen Date Defended: 01 October 2015 ii The Thesis Committee for Syed Faiz Ahmed certifies that this is the approved version of the following thesis: High-Power T/R circuits for a Multichannel VHF/UHF/HF Ice Imaging Radar ________________________________ Chairperson Dr. Carlton Leuschen Date approved: 01 October 2015 iii Abstract This thesis presents the design and implementation of high-power wide-bandwidth transmit/receive (T/R) switches and modules for use in multi-channel ice-penetrating imaging radars. The switches were designed to address the lack of standard off-the shelf (COTS) devices that meet our technical requirements. The design of these switches was accomplished using electronic design automation (EDA) tools and implemented with quadrature hybrids and actively-biased PIN diodes. Three different circuits were developed for three different frequency bands: 160-230 MHz (VHF band), 150-600 MHz (VHF/UHF), and 10-45 MHz (HF band). The circuits are capable of transmitting at least 1000 W of peak power and exhibit an insertion loss lower than 1.3 dB for 160-230 MHz, 1.6 dB for 150-600 MHz, and 2.39 dB for 10-45 MHz ranges. A fourth, miniaturized prototype for the 160-230 MHz range was implemented for use in future multi-channel systems. -

Gunn Diode - Wikipedia, the Free Encyclopedia Page 1

Gunn diode - Wikipedia, the free encyclopedia Page 1 Gunn diode From Wikipedia, the free encyclopedia A Gunn diode , also known as a transferred electron device (TED), is a form of diode, a two-terminal passive semiconductor electronic component, with negative resistance, used in high-frequency electronics. Its largest use is in electronic oscillators to generate microwaves, in applications such as radar speed guns and microwave relay data link transmitters. Its internal construction is unlike other diodes in that it consists only of N-doped semiconductor material, whereas most diodes consist of both P and N-doped regions. It therefore does not conduct in only one direction and cannot rectify alternating current like other diodes, which is why some sources do not use the term diode and prefer TED. In the Gunn diode, three regions exist: two of them are heavily N-doped on each terminal, with a thin layer of A Russian-made Gunn diode lightly doped material in between. When a voltage is applied to the device, the electrical gradient will be largest across the thin middle layer. If the voltage is increased, the current through the layer will first increase, but eventually, at higher field values, the conductive properties of the middle layer are altered, increasing its resistivity, causing current to fall. This means a Gunn diode has a region of negative differential resistance in its current-voltage characteristic curve, in which an increase of voltage across it causes a decrease in current. This property allows it to amplify, functioning as a radio frequency amplifier, or become unstable and oscillate, when it is biased with a DC voltage. -

Site Master S3xxe User Guide

User Guide Site Master Cable and Antenna Analyzer with Spectrum Analyzer S331E, 2 MHz to 4 GHz S332E, 2 MHz to 4 GHz, Spectrum Analyzer, 9 kHz to 4 GHz S361E, 2 MHz to 6 GHz S362E, 2 MHz to 6 GHz, Spectrum Analyzer, 9 kHz to 6 GHz Appendix A provides a list of supplemental documentation for the Site Master features and options. The documentation set is available as PDF files on the Anritsu website. Anritsu Company Part Number: 10580-00252 490 Jarvis Drive Revision: V Morgan Hill, CA 95037-2809 Published: April 2020 USA Copyright 2020 Anritsu Company, USA. All Rights Reserved. http://www.anritsu.com Table of Contents Chapter 1—General Information 1-1 Introduction. 1-1 Additional Documentation . 1-1 Contacting Anritsu for Sales and Service . 1-2 1-2 Instrument Description . 1-2 Available Models . 1-3 Available Options. 1-3 1-3 Calibration and Verification. 1-4 1-4 Instrument Care and Preventive Maintenance . 1-4 Connector Care . 1-4 ESD Caution . 1-5 RF Input Warning . 1-6 Battery Replacement . 1-6 1-5 Secure Environment Workplace . 1-7 Site Master Memory Types . 1-8 Erase All User Files in Internal Memory . 1-9 Recommended Usage in a Secure Environment . 1-9 Chapter 2—Instrument Overview 2-1 Introduction. 2-1 2-2 Turning On the Site Master. 2-1 2-3 Instrument Front Panel . 2-2 LED Indicators . 2-2 Front Panel Keys . 2-3 2-4 Interface Screen . 2-6 Touch Screen Keys . 2-8 Symbols and Icons on the Title Bar . -

Design of Bias Tees for a Pulsed-Bias, Pulsed-Rf Test System Using Accurate Component Models

DESIGN OF BIAS TEES FOR A PULSED-BIAS, PULSED-RF TEST SYSTEM USING ACCURATE COMPONENT MODELS In this article, a design of custom bias tees to be used in a pulsed-bias, pulsed-RF measurement system is described. The bias tee design is such that the DC path allows bias pulses to pass through to the device unchanged, while still allowing RF measurements at as low a frequency as possible. The use of accurate component models led to a successful simulation-based development of a bias tee with a (three-port) frequency response that allows accurate pulsed S-parameter and pulsed IV measurement results to be achieved in the desired bandwidth. his article describes the design of a bias itor, as shown in Figure 1. The function of the tee for a pulsed-bias, pulsed-RF test bias tee is to simultaneously allow a DC bias T system. The cut-off frequency of the voltage and an RF test signal to be applied to DC path was raised to allow pulsing of the the port of a transistor during measurement. bias signal. The theory of bias tee design for For example, in an S-parameter measurement pulsed measurements is first presented. The system, the DC bias is applied at the port la- simulation results for the design without the beled “DC,” and the RF test signal from the use of component models are presented, fol- vector network analyzer is applied to the port lowed by simulation results obtained using ac- labeled “RF.” At the RF + DC port, both the curate parasitic models for the inductor and RF and DC voltages are applied to the device. -

AN11640 TFF1044 Application Recommendations Rev

AN11640 TFF1044 Application Recommendations Rev. 1 — 4 June 2015 Application note Document information Info Content Keywords TFF1044, Quad LNB, Quattro LNB, DVB-S, Ku band to L-band Down Converter, FIMOD IC, Ku Band, NF, PCB Abstract This application note describes how to use the TFF1044 in a typical environment, (typically in DVB-S outdoor equipment). It also lists some do’s and don’ts and frequently asked questions. NXP Semiconductors AN11640 TFF1044 Application Recommendations Revision history Rev Date Description 1 20150604 First publication Contact information For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: [email protected] AN11640 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2015. All rights reserved. Application note Rev. 1 — 4 June 2015 2 of 28 NXP Semiconductors AN11640 TFF1044 Application Recommendations TFF1044 Application Recommendations 1. Introduction This document describes the functionality and use of TFF1044 DCV IC. It also gives some application hints and a schematic for a Quad LNB design with pHEMT first stage LNA’s and SiGe second stage LNA stages. 2. Product Description The TFF1044HN is a 10.70 GHz to 12.75 GHz Ku band down converter for use in universal quad and Quattro Low Noise Block (LNB) in satellite receiver systems. The device features two RF inputs (two polarizations) and four IF outputs (up to 4 active IF paths). It integrates bias generation and control for the external LNA stages, image rejection filtering, LO generation, down conversion mixers, IF amplifier stages, voltage and tone detection on each IF output (for polarization and band selection) and the 4 (IF channels) x 4 (2 polarizations, 2 bands) IF matrix switch. -

Development of an Experimental Facility for the Study of Microparticle Initiated Radio-Frequency Vacuum Breakdown R

Development of an experimental facility for the study of microparticle initiated radio-frequency vacuum breakdown R. Casagrande,1, 2, 3, a) H. Faugel,2 F. Fischer,2 H. Fünfgelder,2 F. Riedl,2 G. Siegl,2 P. Bettini,3 J.-M. Noterdaeme,1, 2 and K. Crombé1, 4 1)Department of Applied Physics, Ghent University, 9000 Gent, Belgium 2)Max-Planck-Institut für Plasmaphysik, 85748 Garching, Germany 3)Università degli Studi di Padova, 35122 Padova, Italy 4)Laboratory for Plasma Physics, ERM/KMS, 1000 Brussels, Belgium (Dated: 8 December 2020) An ongoing objective in ion cyclotron range of frequencies (ICRF) systems is the improvement of power coupling to the plasma. During the last decade, this goal has been mainly pursued through the study of the coupling resistance, either by optimizing the antenna layout or by tailoring the Scrape-O Layer (SOL) prole with gas pung. Another approach is to increase the voltage handling capability of the ICRF system, limited by breakdown in the launchers or in the transmission lines. This paper describes the design of IBEX, a device to investigate fundamental aspects of radio-frequency arcs in ICRF-relevant conditions. IBEX can achieve a peak voltage of 48 kV at 54 MHz, with 5 kW input power. I. INTRODUCTION kV/mm on all the other locations2. These boundaries are extrapolated from the operational conditions of ex- In next generation fusion devices, in order to meet isting antennas, hence the strategy to ensure reliability the tritium breeding ratio requirements, heating sys- and availability is to provide a reasonably large margin tems with reduced impact on the breeder volume will be on the main macroscopic parameters aecting the break- required1. -

DC Offsets in Direct-Conversion Receivers: Characterization and Implications

DC Offsets in Direct-Conversion Receivers: Characterization and Implications ■ R. Svitek and S. Raman irect-conversion receivers (DCRs), also known as RF Front-End Dzero-IF or homodyne re- ceivers, have received significant Low-Pass Mixer attention over the last decade and Filter have become a popular alternative I to the classical heterodyne architec- ture (which has dominated receiver Band topologies for more than 70 years) Select Low-Noise in the development of RF integrated Filter Amplifier To ADCs and circuits (ICs) for wireless applica- Baseband Processing tions. Rather than downconverting to a finite IF, as in the heterodyne case, DCRs translate the desired RF Low-Pass spectrum directly to dc using a local Filter oscillator (LO) frequency exactly Q equal to the RF. The simplicity of this architecture affords two major advantages over the heterodyne Mixer approach. First, because the inter- mediate frequency (IF) is zero, the image to the desired RF signal is the desired signal itself, which means Figure 1. Block diagram of the DCR. DCRs do not face conventional image problems. Therefore, bulky, off-chip, front-end image- be performed either with a simple analog low-pass filter or reject filters, which are required in heterodyne topologies, are by converting to the digital domain with an analog-to-digital unnecessary in a DCR [1]. Second, with the desired spectrum converter (ADC) and digitally performing channel selection down-converted directly to baseband, channel selection can with digital-signal processing (DSP). The latter approach raises the possibility of having a “universal” RF front-end R. Svitek and S. -

Application Note on Remote Amplifier Powering Abbreviations in This Article: Whitham D

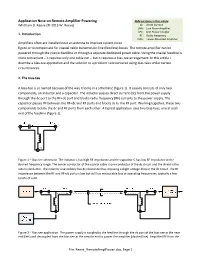

Application Note on Remote Amplifier Powering Abbreviations in this article: Whitham D. Reeve (© 2013 W. Reeve) dc: direct current LNA: Low Noise Amplifier LPC: LNA Power Coupler 1. Introduction RF: Radio frequency TMA: Tower-Mounted Amplifier Amplifiers often are installed near an antenna to improve system noise figure or to compensate for coaxial cable transmission line (feedline) losses. The remote amplifier can be powered through the coaxial feedline or through a separate dedicated power cable. Using the coaxial feedline is more convenient – it requires only one cable run – but it requires a bias-tee arrangement. In this article I describe a bias-tee application and the solution to a problem I encountered using bias-tees under certain circumstances. 2. The bias-tee A bias-tee is so named because of the way it looks in a schematic (figure 1). It usually consists of only two components, an inductor and a capacitor. The inductor passes direct current (dc) from the power supply through the dc port to the RF+dc port and blocks radio frequency (RF) currents to the power supply. The capacitor passes RF between the RF+dc and RF ports and blocks dc to the RF port. Working together, these two components isolate the dc and RF ports from each other. A typical application uses two bias-tees, one at each end of the feedline (figure 2). Figure 1 ~ Bias-tee schematic. The inductor L has high RF impedance and the capacitor C has low RF impedance in the desired frequency range. The center conductor of the coaxial cable is one conductor of the dc circuit and the shield is the return conductor.