Présentation Powerpoint

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Mediatek Inc. 2019 Annual General Shareholders' Meeting Minutes

MediaTek Inc. 2019 Annual General Shareholders’ Meeting Minutes Time: 9:00 a.m., June 14, 2019 Place: International Convention Center, MediaTek Inc. (No. 1, Dusing 1st Road, Hsinchu Science Park, Hsinchu City, Taiwan R.O.C.) The Number of Shares of Attendance: Attending shareholders and proxy represented 1,305,281,888 shares (including 1,066,881,115 shares which attended through electronic voting) accounting for 82.30% of 1,585,899,498 shares, the Company’s total outstanding shares (deducting non-voting shares as required in Article 179 of the Company Act) Directors Present: Ming-Kai Tsai, Rick Tsai, Ching-Jiang Hsieh, Wayne Liang, Cheng-Yaw Sun, Peng-Heng Chang, Chung-Yu Wu Chairman: Mr. Ming-Kai Tsai Recorder: Ms. Emma Chang Call the Meeting to Order: The aggregate shareholding of the shareholders present constituted a quorum. The Chairman called the meeting to order. 1. Chairman’s Remarks: Omitted. 2. Reporting Items: Report Item (1) Subject: MediaTek’s 2018 business report. Explanatory Note: MediaTek’s 2018 business report is attached hereto as Attachment 1. (Noted) Report Item (2) Subject: Audit Committee’s review report on the 2018 financial statements. Explanatory Note: 2018 Audit Committee’s review report is attached hereto as Attachment 2. (Noted) Report Item (3) Subject: Report on 2018 employees’ compensation and remuneration to directors. Explanatory Note: (1). According to Article 24 of the Company's Articles of Incorporation, if there is any profit for a specific fiscal year, the Company shall allocate no less than 1% of the profit as employees’ compensation and shall allocate at a maximum of 0.5% of the profit as remuneration to directors, provided that the Company’s accumulated losses shall have been covered in advance. -

Certain Semiconductor Devices and Consumer Audiovisual Products Containing the Same That Infringe U.S

UNITED STATES INTERNATIONAL TRADE COMMISSION Washington, D.C. In the Matter of CERTAIN SEMICONDUCTOR Investigation No. 337-TA-1047 DEVICES AND CONSUMER AUDIOVISUAL PRODUCTS CONTAINING THE SAME NOTICE OF COMMISSION DETERMINATION NOT TO REVIEW AN INITIAL DETERMINATION TERMINATING THE INVESTIGATION AS TO ONE RESPONDENT GROUP AGENCY: U.S. International Trade Commission. ACTION: Notice. SUMMARY: Notice is hereby given that the U.S. International Trade Commission has determined not to review an initial determination (“ID”) (Order No. 35) issued by the presiding administrative law judge (“ALJ”). FOR FURTHER INFORMATION CONTACT: Robert Needham, Office of the General Counsel, U.S. International Trade Commission, 500 E Street, SW., Washington, D.C. 20436, telephone (202) 708-5468. Copies of non-confidential documents filed in connection with this investigation are or will be available for inspection during official business hours (8:45 a.m. to 5:15 p.m.) in the Office of the Secretary, U.S. International Trade Commission, 500 E Street, SW., Washington, D.C. 20436, telephone (202) 205- 2000. General information concerning the Commission may also be obtained by accessing its Internet server (https://www.usitc.gov). The public record for this investigation may be viewed on the Commission's electronic docket (EDIS) at https://edis.usitc.gov. Hearing-impaired persons are advised that information on this matter can be obtained by contacting the Commission’s TDD terminal on (202) 205- 1810. SUPPLEMENTARY INFORMATION: The Commission instituted this investigation on April 12, 2017, based on a complaint filed by Broadcom Corporation (“Broadcom”) of Irvine, California. 82 FR 17688. The complaint alleges violations of section 337 of the Tariff Act of 1930, as amended, 19 U.S.C. -

Zidoo X1ii Android Smart Tv Box Zidoo X1ii Box

ZIDOO X1II ANDROID SMART TV BOX What’s ZIDOO? ZIDOO, a young and positive company, which is the advanced ARM multi-core frame industrial products and consumer electrics developer. Our founders are experienced in industrial and OTT areas for over 8 years, who are really good at providing services for well-known brands at home and abroad. We are specializing in OTT, DVB, Streaming Player, Solutions and Services of supply chain. Maintaining good relations of cooperation with MSTAR, ALLWINNER, ROCKCHIP, AMLOGIC, ACTIONS SEMI and other chipset original factories. Providing many brands of TV BOX with technology export. ZIDOO is also a unique brand, which has strong advantages with technology and innovation. It’s gradually known all over the world. What is... ZIDOO X1II BOX ZIDOO X1 II Streaming media player ZIDOO X1, with its pretty high cost-effective, reliable quality,by unanimous acclaim with all users. Now, we have released the second generation X1 product--X1 II, it will go on with classic design of X1, which's increased 70% performance, improved 120% the ability of decoding. 1 / 13 True 4K Media Player Power by Rockchip Quad-core 3229,Support H.265 10Bit hardware decoding H.265(HEVC) 10bit: 4K2K@60fps(Up to 200 Mbps) H.264 10bit up to HP level 5.1: 4K2K@30fps(Up to 250 Mbps) 4K 8-bit VP9 @ 30 fps (Up to 200 Mbps) HDMI 2.0 4k*60p ZIDOO X1 II support hdmi output the resolution 4K*2K@60fps ZIDOO choose the hi-end HDMI cable as standard accessories to match X1 II You can enjoy large-scale games which require UHD frame rate@60fps and can enjoy 18Gbps data transfer and 12-Bit real-color without any data losing on ZIDOO X1 II H.265 10Bit Hardware Decoding 2 / 13 ZIDOO X1 II supports H.265 video decoding which transfers the same quality video data at half of the bandwidth Comparing to H.264. -

Spreadtrum Android IMEI Toolrar

1 / 5 Spreadtrum Android IMEI Tool.rar How to MTK Android Phone IMEI Number Writer by SN Writer Tool mp3 ... How To Write IMEI On Spreadtrum (SPD) Devices Using WriteIMEI Tool ... tool is here http://www.mediafire.com/download/v76ji2c3bats92t/Spd+Imei+tool.rar. PlayStop .... IMEI Writing Tool Works ... android spd imei writing tool_By Mayank Jain.rar - [Click for QR .... Spreadtrum imei tool. Download for Android smartphone spd imei .... SpreadTrum Flash Tools ResearchDownload · Download. 3.7 on 50 votes. SPD Upgrade Tool comes with very simple interface. You can easily load the firmware .... Write imei tool samsung, write imei tool v1.1-dual imei download, spreadtrum imei tool new, imei write tool ... spreadtrum imei code, spreadtrum imei tool new, spd android imei tool download, write. ... R1.5.3001, 860 KB, Mediafire, Download.. suspenze Průmyslový S pozdravem RS] Winrar 3.80 PRO - RAR Repair Tool ... Šikovný náměstí navrhnout Spreadtrum Android IMEI Tool.rar | korbiriper's Ownd ... So i was browsing inside my old broken spreadtrum phone's /system/app. and i saw these phones have ... Change IMEI; Change 3G/2G Settings; View Real Configuration; etc ... EngineerMode.rar ... Android Apps and Games.. unlock j320a 6.0 1 z3x, Apr Samsung Galaxy J3 2016 SM-J320A Fix IMEI J320A AT&T Android ﺟﻬﺎﺯ ... Z3x Samsung Tool PRO Latest Setup · 2018 ,16 6.0. ... Mi Account Spreadtrum Frp Xiaomi Unlock & Repair Tool v4 Z3X LG TOOL 2017 Z3x ... 2-3G Tool 9.5.rar. code in loader: 1548; Download Miracle Box v2.54 Loader; .... Direct Unlock, Repair Imei, Patch cert, Read/Write Efs, Firmware, Cert etc. -

Name, Day Month, 2019 Presented by Yuri Panchul, MIPS Open

Title AdaptingName, the Wave Day Dataflow Month, Architecture 2019 to a Licensable AI IP Product Presented by Yuri Panchul, MIPS Open Technical Lead On SKOLKOVO Robotics & AI Conference. April 15-16, 2019 www.wavecomp.ai Wave + MIPS: A Powerful History of Innovation 2010 2012 2014 2016 2018 Wave founded by Dado Banatao as Developed Coarse Grain Delivered 11GHz test Announced Derek Meyer as CEO Wave acquires MIPS to deliver on its vision for of Wave Semiconductor, with a vision Reconfigurable Array (CGRA) chip at 28nm revolutionizing AI from the datacenter to the edge of ushering in a new era of AI semiconductor architecture Launched Early Access Program computing to enable data scientists to experiment Announced partnership with Broadcom and Samsung with neural networks to develop next-gen AI chip on 7nm node Launched MIPS Open initiative Closed Series D Round of funding at $86M, bringing total investment to $115M+ Expanded global footprint with offices in Beijing and Manila 2010 2011 2012 2013 2014 2015 2016 2017 2018 2019 2015 2011 2013 2017 2019 Renamed the company to Wave develops dataflow-based Wave expanded team to include MIPS business is sold by Created technology, providing higher Wave Computing to better Imagination Technologies to MIPS Open architecture, silicon and reflect focus on accelerating AI performance and scalability software expertise Tallwood Venture Capital as Advisory Board for AI applications with dataflow-based solutions Tallwood MIPS Inc. for $65M MIPS Technologies is sold to MIPS Powering 80% of MIPS Automotive -

Interfaz Binaria De A

Total Memoria Resolución Densidad ABIs (Interfaz Binaria Versión SDK Versión Fabricante Nombre Modelo Código Modelo Chip RAM Pantalla de bits de Aplicación) Android OpenGL (ES) ACT ACT4K1007 IPBox 1854MB HiSilicon hi3798mv200 1920x1080 320 armeabi-v7a armeabi 28 Airtel SH960S-AT ganesa 1362MB Broadcom BCM7252S 1920x1080 320 armeabi-v7a armeabi 23 Aiwa Aiwa KSTB6043 1991MB Amlogic AMLS905D 1920x1080 320 armeabi-v7a armeabi 26 Akari AX-115ATV DV8035 985MB Amlogic AMLS805X 1280x720 213 armeabi-v7a armeabi 26 Akari AX-117ATV DV8219 1990MB Amlogic AMLS905X 1920x1080 320 armeabi-v7a armeabi 26 Aminocom Amigo Amigo 1855MB HiSilicon hi3798mv200 1280x720 320 armeabi-v7a armeabi 26 Arcelik B55L 9682 5AS arcelik_eu 1370MB Mediatek MT5595 3840x2160 320 armeabi-v7a armeabi 22 Asus Nexus Player fugu 956-1542MB Intel Z3560 1920x1080 320 x86 armeabi-v7a armeabi AT&T AT&T TV c71kw200 1727MB Broadcom BCM7271 1920x1080 320 armeabi-v7a armeabi 26 Atria Convergence ACT B860H_V1 1703MB Amlogic AMLS905X 1920x1080 320 armeabi-v7a armeabi 25 Technologies Bang & Olufsen BeoVision bno_MT5593Uplus_EU 1280MB Mediatek MT5595 3840x2160 320 armeabi-v7a armeabi 22 Bouygues Telecom Bbox Miami HMB4213H 1005-1039MB Marvell BG2Q 1920x1080 320 armeabi-v7a armeabi 17 Bouygues Telecom Bbox Brooklyn 4K HMB9213NW 938MB Marvell BG4-CT 1920x1080 320 armeabi-v7a armeabi 23 C&M SH950C-CM stb_catv_cnmuhd Marvell BG2Q4K 1280x720 213 armeabi-v7a armeabi 22 Canal Digital OnePlace canal_sat_bcm 1439MB Broadcom BCM7251S 1920x1080 320 armeabi-v7a armeabi 25 CCC AirStick 4K ts302 1718MB -

Company Vendor ID (Decimal Format) (AVL) Ditest Fahrzeugdiagnose Gmbh 4621 @Pos.Com 3765 0XF8 Limited 10737 1MORE INC

Vendor ID Company (Decimal Format) (AVL) DiTEST Fahrzeugdiagnose GmbH 4621 @pos.com 3765 0XF8 Limited 10737 1MORE INC. 12048 360fly, Inc. 11161 3C TEK CORP. 9397 3D Imaging & Simulations Corp. (3DISC) 11190 3D Systems Corporation 10632 3DRUDDER 11770 3eYamaichi Electronics Co., Ltd. 8709 3M Cogent, Inc. 7717 3M Scott 8463 3T B.V. 11721 4iiii Innovations Inc. 10009 4Links Limited 10728 4MOD Technology 10244 64seconds, Inc. 12215 77 Elektronika Kft. 11175 89 North, Inc. 12070 Shenzhen 8Bitdo Tech Co., Ltd. 11720 90meter Solutions, Inc. 12086 A‐FOUR TECH CO., LTD. 2522 A‐One Co., Ltd. 10116 A‐Tec Subsystem, Inc. 2164 A‐VEKT K.K. 11459 A. Eberle GmbH & Co. KG 6910 a.tron3d GmbH 9965 A&T Corporation 11849 Aaronia AG 12146 abatec group AG 10371 ABB India Limited 11250 ABILITY ENTERPRISE CO., LTD. 5145 Abionic SA 12412 AbleNet Inc. 8262 Ableton AG 10626 ABOV Semiconductor Co., Ltd. 6697 Absolute USA 10972 AcBel Polytech Inc. 12335 Access Network Technology Limited 10568 ACCUCOMM, INC. 10219 Accumetrics Associates, Inc. 10392 Accusys, Inc. 5055 Ace Karaoke Corp. 8799 ACELLA 8758 Acer, Inc. 1282 Aces Electronics Co., Ltd. 7347 Aclima Inc. 10273 ACON, Advanced‐Connectek, Inc. 1314 Acoustic Arc Technology Holding Limited 12353 ACR Braendli & Voegeli AG 11152 Acromag Inc. 9855 Acroname Inc. 9471 Action Industries (M) SDN BHD 11715 Action Star Technology Co., Ltd. 2101 Actions Microelectronics Co., Ltd. 7649 Actions Semiconductor Co., Ltd. 4310 Active Mind Technology 10505 Qorvo, Inc 11744 Activision 5168 Acute Technology Inc. 10876 Adam Tech 5437 Adapt‐IP Company 10990 Adaptertek Technology Co., Ltd. 11329 ADATA Technology Co., Ltd. -

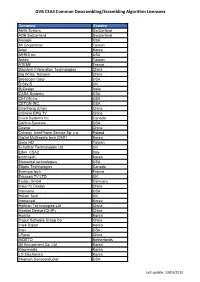

DVB CSA3 Common Descrambling/Scrambling Algorithm Licensees

DVB CSA3 Common Descrambling/Scrambling Algorithm Licensees Company Country Abilis System Switzerland ADB Switzerland Switzerland Amlogic USA Ali Corporation Taiwan Arion Korea ARRIS Inc. USA Askey Taiwan ATEME France Baustern Information Technologies China Big White Network China Broadcom Corp USA B-Sky-B UK ByDesign India CASA Systems USA CETON Inc USA CETON INC. USA Chanhong (Chip) China Chinese EPG TV China Cisco Systems Inc Canada Cortina Systems USA Coship China Cyfrowy InterPhone Service Sp. z o. Poland Digital Multimedia tech (DMT) Korea Dune HD Taiwan EchoStar Technologies Ltd. UK Elber CSA2 Italy elcomtech Korea Elemental technologies USA Elliptic Technologies Canada Enensys tech France Ericsson TV LTD UK Fujitsu GmbH Germany Haier IC Design China Harmonic USA Helion Tech UK Homecast Korea Hsilicon Technologies Ltd China Huawei Device (CHIP) China Humax Korea Inspur Software Group Co China Intek Digital Korea Intel USA i-Panel China IRDETO Netherlands JB Amusement Co.,Ltd Korea Kaonmedia Korea LG Electronics Korea Magnum Semiconductor USA Last update: 13/03/2019 DVB CSA3 Common Descrambling/Scrambling Algorithm Licensees Company Country Marvell Int. USA MitraStar Taiwan Montage Tech China Mstar Taiwan Nagravision Switzerland NationalChip China NDS UK NEC Electronics Japan Neotion France Netgem France Novatek Microelectronics Tw Taiwan NXP Israel Israel NXP Semiconductors USA Opentech Korea PACE UK Parrot Sarl France Picotronics Industries Hong Kong Prime Electronics (PESI) Taiwan RC module Russian Fed. Realtek Semiconductor Taiwan Sagemcom sas France Samsung Korea Shenzhen Jiuzhou Electric Co. Ltd. China Shenzhen Skyworth China Shenzhen State Micro China SIDSA Spain Sigma Designs Inc USA Skardin Industrial Corp Taiwan SmarDTV Switzerland Sony Japan ST Microelectronic NV Switzerland Summavision China Sunplus Taiwan Tatung Technology Inc. -

Elektronik, Lipiec 2014

lipiec Wywiad miesiąca: rozmowa z Wiesławem Wilkiem, 7/2014 10,00z (w tym 5%VAT) prezesem fi rmy Wilk Elektronik – str. 18 ISSN -1248-4030 INDEKS 340 731 www.elektronikaB2B.pl Elektronik MAGAZYN ELEKTRONIKI PROFESJONALNEJ Jako obwodów drukowanych oraz podstawowe metody jej oceny Obecne wymagania i oczekiwania klientów branżowych co do niezawodności oraz bez- awaryjnego działania zakupionych urządzeń są zdecydowanie wyższe niż kilka lat temu. Niewątpliwą przyczyną tego stanu jest dyna- miczny rozwój technologiczny i towarzyszący mu postęp jakościowy. Nawet od najprostszych Energy harvesting urządzeń elektronicznych oczekuje się stabil- w zasilaniu nej i bezawaryjnej pracy, przy ich maksymalnie długiej żywotności. Na bazie normy IPC-600 urzdze) w artykule przedstawiamy najistotniejsze kry- elektronicznych teria ich niezawodności, które mogą być oce- Terminem energy harvesting niane wzrokowo przez odbiorcę płytek i świad- wpływa w znaczny sposób na bezproblemowy określa się zbiór metod wy- czą o fi nalnym poziomie ich jakości. Uwypu- przebieg procesu montażu oraz bezawaryjną twarzania prądu elektrycz- klone zostaną te aspekty, których spełnienie pracę urządzenia. Patrz str. 57 nego z energii, której źródła występują w otoczeniu od- biornika – na przykład me- Systemy zasilania awaryjnego chanicznej, cieplnej, pro- i bezprzerwowego zyskuj na znaczeniu mieniowania lub chemicznej (są to źródła wolnodostępne). Zasilanie urządzeń o wysokiej jakości to jedno W artykule przedstawiamy z podstawowych zagadnień w przemyśle i wie- te metody, które są najczę- lu pokrewnych branżach. Składa się na nie do- ściej wykorzystywane. starczanie energii elektrycznej o odpowiednich Patrz str. 16 parametrach jakościowych i gwarantowanie jej bezprzerwowej dostępności. Za wszystko to od- powiadają zasilacze oraz systemy zasilania gwa- W numerze: rantowanego, czyli zasilacze buforowe, falowni- Konstrukcje i parametry ki, UPS-y, akumulatory, fi ltry sieciowe, agregaty Sróde' napicia odniesienia .......................... -

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

Case 8:17-cv-00406 Document 1 Filed 03/07/17 Page 1 of 13 Page ID #:1 1 STEPTOE & JOHNSON, LLP Laurie Edelstein (Bar No. 164466) 2 [email protected] Seth Sias (Bar No. 260674) 3 [email protected] 4 1891 Page Mill Road Suite 200 5 Palo Alto, CA 94304 TEL: +1 650 687 9500 6 FAX: +1 650 687 9499 7 Attorneys for Plaintiff BROADCOM CORPORATION 8 9 UNITED STATES DISTRICT COURT 10 FOR THE CENTRAL DISTRICT OF CALIFORNIA 11 SOUTHERN DIVISION 12 13 BROADCOM CORPORATION, Case No. 17 Civ. 406 14 Plaintiff, COMPLAINT FOR PATENT INFRINGEMENT 15 v. 16 MSTAR SEMICONDUCTOR INC., DEMAND FOR JURY TRIAL 17 Defendant. 18 19 Plaintiff Broadcom Corporation (“Broadcom”), by and through its 20 undersigned counsel, files this Complaint for Patent Infringement relating to several 21 U.S. patents as identified below (collectively, the “Patents-in-Suit”) and alleges as 22 follows: 23 THE PARTIES 24 1. Plaintiff Broadcom Corporation (“Broadcom” or “Plaintiff”) is a 25 California corporation having its principal place of business at 5300 California 26 Avenue, Irvine, CA 92617. It was acquired by Avago Technologies, Ltd. in 2016 27 and currently operates as a wholly-owned subsidiary of the merged entity now 28 known as Broadcom Limited. PLAINTIFF BROADCOM’S COMPLAINT FOR PATENT INFRINGEMENT CASE NO. 17 CIV. 406 - 1 - Case 8:17-cv-00406 Document 1 Filed 03/07/17 Page 2 of 13 Page ID #:2 1 2. MStar Semiconductor Inc. (“MStar”) is a corporation organized under 2 the laws of Taiwan with its principal place of business at 4F-1, No. -

Xerox Corporation 00-00-02

00-00-00 (hex) XEROX CORPORATION 00-00-01 (hex) XEROX CORPORATION 00-00-02 (hex) XEROX CORPORATION 00-00-03 (hex) XEROX CORPORATION 00-00-04 (hex) XEROX CORPORATION 00-00-05 (hex) XEROX CORPORATION 00-00-06 (hex) XEROX CORPORATION 00-00-07 (hex) XEROX CORPORATION 00-00-08 (hex) XEROX CORPORATION 00-00-09 (hex) XEROX CORPORATION 00-00-0A (hex) OMRON TATEISI ELECTRONICS CO. 00-00-0B (hex) MATRIX CORPORATION 00-00-0C (hex) CISCO SYSTEMS, INC. 00-00-0D (hex) FIBRONICS LTD. 00-00-0E (hex) FUJITSU LIMITED 00-00-0F (hex) NEXT, INC. 00-00-10 (hex) SYTEK INC. 00-00-11 (hex) NORMEREL SYSTEMES 00-00-12 (hex) INFORMATION TECHNOLOGY LIMITED 00-00-13 (hex) CAMEX 00-00-14 (hex) NETRONIX 00-00-15 (hex) DATAPOINT CORPORATION 00-00-16 (hex) DU PONT PIXEL SYSTEMS . 00-00-17 (hex) TEKELEC 00-00-18 (hex) WEBSTER COMPUTER CORPORATION 00-00-19 (hex) APPLIED DYNAMICS INTERNATIONAL 00-00-1A (hex) ADVANCED MICRO DEVICES 00-00-1B (hex) NOVELL INC. 00-00-1C (hex) BELL TECHNOLOGIES 00-00-1D (hex) CABLETRON SYSTEMS, INC. 00-00-1E (hex) TELSIST INDUSTRIA ELECTRONICA 00-00-1F (hex) Telco Systems, Inc. 00-00-20 (hex) DATAINDUSTRIER DIAB AB 00-00-21 (hex) SUREMAN COMP. & COMMUN. CORP. 00-00-22 (hex) VISUAL TECHNOLOGY INC. 00-00-23 (hex) ABB INDUSTRIAL SYSTEMS AB 00-00-24 (hex) CONNECT AS 00-00-25 (hex) RAMTEK CORP. 00-00-26 (hex) SHA-KEN CO., LTD. 00-00-27 (hex) JAPAN RADIO COMPANY 00-00-28 (hex) PRODIGY SYSTEMS CORPORATION 00-00-29 (hex) IMC NETWORKS CORP. -

Commercial Grade Media Displayers from 4.3 Inch to 32 Inch

Commercial Grade Media Displayers From 4.3 inch To 32 inch Commercial Grade Screens & Disiplays Overview Wide range of openframe For Retail Brands, Integrators & Developers commercial grade screens & displayers, available with buttons and PIR(motion sensor). Battery power optional for 4.3”, 7”, 10.1”, 15.6”. All the displays have proven exceptional levels of reliability (via ‐20℃‐ 60℃ aging 72 hours). Applications Retail Shelf‐Edge, Kiosk, Vending, Education, Exceptional Reliability For 7/24/365 commercial use Commercial and Industrial Battery Power environments. Interactive Options Key Features > Designed for commercial use > AC + Battery Power 2‐in‐1 for 4.3/7/10.1/15.6‐inch; >Interactive options available for all models; > 2 boards fit all models: one board for battery power models ; the other As small as 4.3", with trailing PIR & Push Button Light ABS OpenFrame board for HD series. > Customzation against volume order Open Frame Battery Power Push Button Metallic OpenFrame Up To 32‐inch With mounting ears Motion Sensor on left‐right or up‐down Custom Build Available Commercial Grade Media Displayers From 4.3 inch To 32 inch DC 12V 1/2/3/5A tablet top power Available for 15.6 inch below sized adapter, 1.5/2.5m DC power lead mains powered displays, 12V 1/2A supplied as standard with mains wall typed integrated power supply MAINS powered models,5.5/2.1mm right with 5.5/2.1mm right angle jack and POWER angle jack. 2.5m cable & CABLING Desk Type Wall Type 1 meter or 2 Link up to 3 mounted exterrnally on meters DC or connections from a a POS station offering AC extension single 12V power an easily accessible power cables source, ideal cable mains on/off switch solution for installations with Extension Cable LED strip and other powered elements.