ME11-L Core Memory System Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

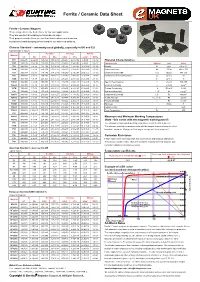

Ferrite / Ceramic Data Sheet

Ferrite / Ceramic Data Sheet Ferrite / Ceramic Magnets These magnets are the best choice for low cost applications. They are excellent at resisting corrosion due to water. Their properties make them an excellent choice when used in motors, loudspeakers and clamping devices and for use with reed switches. Chinese Standard - commonly used globally, especially in UK and EU Typical Range of Values Br Hc (Hcb) Hci (Hcj) BHmax Material mT kG kA/m kOe kA/m kOe kJ/m3 MGOe Y8T 200-235 2.0-2.35 125-160 1.57-2.01 210-280 2.64-3.52 6.5-9.5 0.8-1.2 Physical Characteristics Y10T 200-235 2.0-2.35 128-160 1.61-2.01 210-280 2.64-3.52 6.4-9.6 0.8-1.2 Characteristic Symbol Unit Value Y20 320-380 3.2-3.8 135-190 1.70-2.39 140-195 1.76-2.45 18.0-22.0 2.3-2.8 Density D g/cc 4.9 to 5.1 Y22H 310-360 3.1-3.6 220-250 2.76-3.14 280-320 3.52-4.02 20.0-24.0 2.5-3.0 Vickers Hardness Hv D.P.N 400 to 700 Y23 320-370 3.2-3.7 170-190 2.14-2.39 190-230 2.39-2.89 20.0-25.5 2.5-3.2 Compression Strength C.S N/mm2 680-720 Y25 360-400 3.6-4.0 135-170 1.70-2.14 140-200 1.76-2.51 22.5-28.0 2.8-3.5 Coefficient of Thermal Expansion C// 10-6/C 15 Y26H 360-390 3.6-3.9 220-250 2.76-3.14 225-255 2.83-3.20 23.0-28.0 2.9-3.5 C^ 10-6/C 10 Y26H-1 360-390 3.6-3.9 200-250 2.51-3.14 225-255 2.83-3.20 23.0-28.0 2.9-3.5 Specific Heat Capacity c J/kg°C 795-855 Y26H-2 360-380 3.6-3.8 263-288 3.30-3.62 318-350 4.00-4.40 24.0-28.0 3.0-3.5 Electrical Resistivity r m Ω.cm 1x1010 Y27H 370-400 3.7-4.0 205-250 2.58-3.14 210-255 2.64-3.20 25.0-29.0 3.1-3.6 Thermal Conductivity k W/cm°C 0.029 Y28 370-400 3.7-4.0 175-210 2.20-2.64 180-220 2.26-2.76 26.0-30.0 3.3-3.8 Modulus of Elasticity l / E Pa 1.8x1011 Y28H-1 380-400 3.8-4.0 240-260 3.02-3.27 250-280 3.14-3.52 27.0-30.0 3.4-3.8 Compression Strength C.S. -

Chapter 6 BUILDING a HOMEBREW

1. Chapter 6, Harris CRYSTAL SETS TO SIDEBAND © Frank W. Harris 2002 Chapter 6 BUILDING A HOMEBREW QRP Among the guys I work, QRPs seem to be the most common homebrew project, second only to building antennas. Therefore this chapter describes a simple QRP design I have settled on. I use my QRPs as stand-alone transmitters or I use them to drive a final amplifier to produce higher power, 25 to 100 watts. It’s true that before you build a transmitter you’ll need a receiver. Unfortunately, a good selective, all-band ham receiver is complicated to build and most guys don’t have the time and enthusiasm to do it. (See chapter 13.) The next chapter describes building a simple, 5 transistor 40 meter receiver which I have used with the QRP below to talk to other hams. This simple receiver will work best during off hours when 40 meters isn’t crowded. It can also be used to receive Morse code for code practice. A 40 meter QRP module. The QRP transmitter above is designed exclusively for 40 meters, (7.000 to 7.300 MHz.) The twelve-volt power supply comes in through the pig-tail wire up on the right. The telegraph key plugs into the blue-marked phono plug socket on the right of the aluminum heat sink. The antenna output is the red-colored socket on the left end of the heat sink. The transmitting frequency of the QRP module is controlled by a quartz crystal. That’s the silver rectangular can plugged into the box on the right front. -

A TWO DIMENSIONAL FERRITE-CORE MEMORY Bv M

A TWO DIMENSIONAL FERRITE-CORE MEMORY Bv M. M. FAROOQUI, S. P. SKiVASTAVA AND R. N. NEOGI (Tata Institute of Fundamental Research, Bomba),) Received January t0, 1957 (Communicated by Prof. Bernard P ABS'IXACT This paper describes a two dimensional matrix memory using ferrite- cores. A urtit consisting of 100 words of I 1 binary digits each has been cortstructed for parallel operation. The word drive is from a biasr switch-core matrix, while the digit drive makes use of pulse--trans- formers. Logic and circuit techniques enable high discrimination bet- ween wanted and unwanted signals. A semi-automatic method for testing the memory cores is also described. INTRODUCTION THE potentiality of magnetie fer¡ with a rectangular hysteresis loop as binary storage elements for digital computer was realised earlier by Forrester. x Later, Papian% s and almost simultaneously Rajchman4, ~ showed the practicability of such a system by successfully operating memories of fairly large capacity. This paper describes a modest attempt in this direction. A memory of I00 words, 11 bits each, has beca constructed to operate with a smaU digital computer at the Tata institute of Fundamental Research, Bombay. THE PRINClPLE OF OPERATION OF THE MEMORY The two stable states required for sto¡ binary information in magnetic cores ate the states of positive and negative magnetisation. These are the states corresponding to the position A0 and Ax on the hysteresis loop and can be termed as the 0- and the 1-states respectively (Fig. 2). Con- sider a number of sucia cores with ah ideaUy rectangular hysteresis character- istic, arranged in rows and columns in the form of a matrix. -

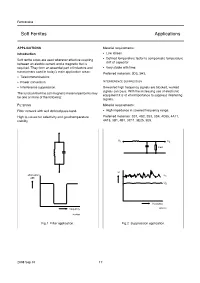

Soft Ferrites Applications

Ferroxcube Soft Ferrites Applications APPLICATIONS Material requirements: Introduction • Low losses • Defined temperature factor to compensate temperature Soft ferrite cores are used wherever effective coupling drift of capacitor between an electric current and a magnetic flux is required. They form an essential part of inductors and • Very stable with time. transformers used in today’s main application areas: Preferred materials: 3D3, 3H3. • Telecommunications • Power conversion INTERFERENCE SUPPRESSION • Interference suppression. Unwanted high frequency signals are blocked, wanted signals can pass. With the increasing use of electronic The function that the soft magnetic material performs may equipment it is of vital importance to suppress interfering be one or more of the following: signals. FILTERING Material requirements: Filter network with well defined pass-band. • High impedance in covered frequency range. High Q-values for selectivity and good temperature Preferred materials: 3S1, 4S2, 3S3, 3S4, 4C65, 4A11, stability. 4A15, 3B1, 4B1, 3C11, 3E25, 3E5. andbook, halfpage handbook, halfpage U1 U2 load U attenuation U1 (dB) U2 frequency frequency MBW404 MBW403 Fig.1 Filter application. Fig.2 Suppression application. 2008 Sep 01 17 Ferroxcube Soft Ferrites Applications DELAYING PULSES STORAGE OF ENERGY The inductor will block current until saturated. Leading An inductor stores energy and delivers it to the load during edge is delayed depending on design of magnetic circuit. the off-time of a Switched Mode Power Supply (SMPS). Material requirements: Material requirements: • High permeability (µi). • High saturation level (Bs). Preferred materials: 3E25, 3E5, 3E6, 3E7, 3E8, 3E9. Preferred materials: 3C30, 3C34, 3C90, 3C92, 3C96 2P-iron powder. U U handbook, halfpage 1 handbook, halfpage1 U2 U2 SMPS load delay U U U1 U2 U1 U2 time time MBW405 MBW406 Fig.3 Pulse delay application. -

Magnetics in Switched-Mode Power Supplies Agenda

Magnetics in Switched-Mode Power Supplies Agenda • Block Diagram of a Typical AC-DC Power Supply • Key Magnetic Elements in a Power Supply • Review of Magnetic Concepts • Magnetic Materials • Inductors and Transformers 2 Block Diagram of an AC-DC Power Supply Input AC Rectifier PFC Input Filter Power Trans- Output DC Outputs Stage former Circuits (to loads) 3 Functional Block Diagram Input Filter Rectifier PFC L + Bus G PFC Control + Bus N Return Power StageXfmr Output Circuits + 12 V, 3 A - + Bus + 5 V, 10 A - PWM Control + 3.3 V, 5 A + Bus Return - Mag Amp Reset 4 Transformer Xfmr CR2 L3a + C5 12 V, 3 A CR3 - CR4 L3b + Bus + C6 5 V, 10 A CR5 Q2 - + Bus Return • In forward converters, as in most topologies, the transformer simply transmits energy from primary to secondary, with no intent of energy storage. • Core area must support the flux, and window area must accommodate the current. => Area product. 4 3 ⎛ PO ⎞ 4 AP = Aw Ae = ⎜ ⎟ cm ⎝ K ⋅ΔB ⋅ f ⎠ 5 Output Circuits • Popular configuration for these CR2 L3a voltages---two secondaries, with + From 12 V 12 V, 3 A a lower voltage output derived secondary CR3 C5 - from the 5 V output using a mag CR4 L3b + amp postregulator. From 5 V 5 V, 10 A secondary CR5 C6 - CR6 L4 SR1 + 3.3 V, 5 A CR8 CR7 C7 - Mag Amp Reset • Feedback to primary PWM is usually from the 5 V output, leaving the +12 V output quasi-regulated. 6 Transformer (cont’d) • Note the polarity dots. Xfmr CR2 L3a – Outputs conduct while Q2 is on. -

Designing Magnetic Components for Optimum Performance Article

Power Supply Design Seminar Designing Magnetic Components for Optimum Performance in Low-Cost AC/DC Converter Applications Topic Category: Magnetic Component Design Reproduced from 2010 Texas Instruments Power Supply Design Seminar SEM1900, Topic 5 TI Literature Number: SLUP265 © 2010, 2011 Texas Instruments Incorporated Power Seminar topics and online power- training modules are available at: power.ti.com/seminars Designing Magnetic Components for Optimum Performance in Low-Cost AC/DC Converter Applications Seamus O’Driscoll, Peter Meaney, John Flannery, and George Young AbstrAct Assuming that the reader is familiar with basic magnetic design theory, this topic provides design guidance to achieve high efficiency, low electromagnetic interference (EMI), and manufacturing ease for the magnetic components in typical offline power converters. Magnetic-component designs for a 90-W notebook adapter and a 300-W ATX power supply are used as examples. Magnetic applications to be considered include the input EMI filter, power inductor design, high-voltage (HV) level-shifting gate drives, and single- and multiple-output forward-mode transformers in both wound and planar formats. The techniques are also applied to flyback “transformers” (coupled inductors) and will enable lower- profile designs with lower intrinsic common-mode noise generation. I. IntroductIon Gate Drive Note: The SI (extended MKS) units system AC Filter PFC Isolated Main Drive (for some Converter Output(s) is used throughout this topic. CM Inductor, topologies), Balanced Bridge, Differential This material is intended as a high- PFC Inductor, Multi-Output Filter level overview of the primary consider- Bias Flyback ations when designing magnetic components for high-volume and cost- Isolated Feedback optimized applications such as computer Fig. -

APPLICATION NOTE How to Select the Right Reinforced Transformer for High Voltage Energy Storage Applications

APPLICATION NOTE How to Select the Right Reinforced Transformer for High Voltage Energy Storage Applications Introduction Providing isolated low voltage bias power to ICs such as microcontrollers, analog-to-digital HCT Series converters, isolated gate drivers or voltage monitoring ICs in high voltage systems is usually accomplished with an isolated DC-DC converter. If the high voltage system is spread out over several modules, the architecture may call for a parallel DC bus on the low voltage side with multiple isolated low power DC-DC converters for each module. Because it is used multiple times in this scenario, an efficient and cost-effective topology is the best approach. This application note highlights the design benefits of using push-pull transformers that are proven solutions for these situations. Used as an example is the Bourns® Model HCTSM8 series transformer, which is AEC-Q200 compliant and available with a wide range of turns ratios as standard. Multiple turns ratios are an important feature enabling the same basic circuit topology to be replicated across a system with the same components and PCB layout. With a transformer series like the Model HCTSM8, designers are able to select the right reinforced transformer part number based on the specified output voltage for powering a microcontroller or an isolated IGBT gate driver. www.bourns.com 07/20 • e/IC2075 APPLICATION NOTE How to Select the Right Reinforced Transformer for High Voltage Energy Storage Applications Why Push-Pull Transformers are an Optimal Choice Electrical Advantages HCT Series Push-pull transformers are known to operate well with low voltages and low variations in input and output. -

Very High Frequency Integrated POL for Cpus

Very High Frequency Integrated POL for CPUs Dongbin Hou Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY in Electrical Engineering Fred C. Lee, Chair Qiang Li Rolando Burgos Daniel J. Stilwell Dwight D. Viehland March 23rd, 2017 Blacksburg, Virginia Keywords: Point-of-load converter, integrated voltage regulator, very high frequency, 3D integration, ultra-low profile inductor, magnetic characterizations, core loss measurement © 2017, Dongbin Hou Dongbin Hou Very High Frequency Integrated POL for CPUs Dongbin Hou Abstract Point-of-load (POL) converters are used extensively in IT products. Every piece of the integrated circuit (IC) is powered by a point-of-load (POL) converter, where the proximity of the power supply to the load is very critical in terms of transient performance and efficiency. A compact POL converter with high power density is desired because of current trends toward reducing the size and increasing functionalities of all forms of IT products and portable electronics. To improve the power density, a 3D integrated POL module has been successfully demonstrated at the Center for Power Electronic Systems (CPES) at Virginia Tech. While some challenges still need to be addressed, this research begins by improving the 3D integrated POL module with a reduced DCR for higher efficiency, the vertical module design for a smaller footprint occupation, and the hybrid core structure for non-linear inductance control. Moreover, as an important category of the POL converter, the voltage regulator (VR) serves an important role in powering processors in today’s electronics. -

Ferrite and Metal Composite Inductors

Ferrite and Metal Composite Inductors Design and Characteristics © 2019 KEMET Corporation What is an Inductor? Coil Magnetic Magnetic flux φ (Wire) Field dφ Core e = - dt Material i The coil converts electric energy into magnetic energy and stores it. e Core Material Current through the coil of wire creates a magnetic field Air Ferrite Metal and stores it. (None) (Iron) Composite Different core materials change magnetic field strength. © 2019 KEMET Corporation Ferrite Inductor or Metal Composite Inductor? Ferrite InductorFerrite Metal InductorMetal Composite MaterialMaterial Type type Ni-ZnNi-Zn Mn-Zn Mn-Zn Fe based Fe Based Very Good!! No Good.. InductanceInductace GoodGood! Very Good No Good Very Good!! Magnetic Saturation Good! No Good.. Good! No Good.. Very Good!! MagneticThermal Saturation Property Good No Good Very Good Good! Very Good!! Good! Efficiency Very Good!! No Good.. Good! ThermalResistance Property of core Good No Good Very Good Efficiency SBC/SBCPGood TPI Very GoodMPC, MPCV Good Products MPLC, MPLCV Resistance of Core Very Good No Good Good © 2019 KEMET Corporation Ferrite and Metal Composite Comparison Advantage of Ferrite 1. Higher inductance with high permeability 2. Stable inductance in the right range High L and Low DCR capability Advantage of Metal Composite 1. Very slow saturation 2. Very stable saturation for the thermal Core Loss Comparison Good for Auto app especially Advantage of Ferrite Very low core loss in dynamic frequency range Mn-Zn Ferrite Metal Core Low power consumption capability © 2019 KEMET Corporation -

Switch Mode Power Supplies and Their Magnetics Tutorial

Datatronic Switch Mode Power Supplies and their Magnetics Many factors must be considered by designers when choosing the magnetic components required in today’s electronic power supplies DATATRONIC DISTRIBUTION, INC. Datatronic In today’s day and age the most often used topology for electronic power supplies is that of the Switch Mode Power Supply (SMPS), which is a major user of magnetics. In some applications the “older type” linear supplies are still used, but in the early 70’s SMPS came into being spurred by the development of faster switching transistors. This facilitated the use of much smaller magnetic components and greater efficiencies. DATATRONIC DISTRIBUTION, INC. Datatronic SMPS and their General Magnetic Usage In general, there are four different types of magnetic components that are needed for the typical SMPS. They include the Output Transformer, usually the most noticeable because of its size compared to the others, the Output Inductors, the Input Inductors and the Current Sense Transformer, each with its own important function. DATATRONIC DISTRIBUTION, INC. Datatronic SMPS and their General Magnetic Usage 1.The Output Transformer or “Main” Transformer takes the input voltage that is supplied to its primary winding and then transforms the input voltage to one or more voltages that are the output of the secondary winding or windings. 2. The Output Inductors are used to filter the output voltage so that the load “sees” a filtered DC voltage. DATATRONIC DISTRIBUTION, INC. Datatronic SMPS and their General Magnetic Usage 3. The Input Inductors filter out the noise generated by the switching transistors so that this noise isn’t emitted back to the source. -

LM2596 SIMPLE SWITCHER Power Converter 150 Khz3a Step-Down

Distributed by: www.Jameco.com ✦ 1-800-831-4242 The content and copyrights of the attached material are the property of its owner. LM2596 SIMPLE SWITCHER Power Converter 150 kHz 3A Step-Down Voltage Regulator May 2002 LM2596 SIMPLE SWITCHER® Power Converter 150 kHz 3A Step-Down Voltage Regulator General Description Features The LM2596 series of regulators are monolithic integrated n 3.3V, 5V, 12V, and adjustable output versions circuits that provide all the active functions for a step-down n Adjustable version output voltage range, 1.2V to 37V (buck) switching regulator, capable of driving a 3A load with ±4% max over line and load conditions excellent line and load regulation. These devices are avail- n Available in TO-220 and TO-263 packages able in fixed output voltages of 3.3V, 5V, 12V, and an adjust- n Guaranteed 3A output load current able output version. n Input voltage range up to 40V Requiring a minimum number of external components, these n Requires only 4 external components regulators are simple to use and include internal frequency n Excellent line and load regulation specifications compensation†, and a fixed-frequency oscillator. n 150 kHz fixed frequency internal oscillator The LM2596 series operates at a switching frequency of n TTL shutdown capability 150 kHz thus allowing smaller sized filter components than n Low power standby mode, I typically 80 µA what would be needed with lower frequency switching regu- Q n lators. Available in a standard 5-lead TO-220 package with High efficiency several different lead bend options, and a 5-lead TO-263 n Uses readily available standard inductors surface mount package. -

INTRODUCTION:- Ferrites Are Ferromagnetic Material Containing Predominantly Oxides Iron Along with Other Oxides of Barium, Stron

INTRODUCTION:- Ferrites are ferromagnetic material containing predominantly oxides iron along with other oxides of barium, strontium, manganese, nickel, zinc, lithium and cadmium .Ferrites are ideally suited for making device like inductor core, circulators, memory devices and also for various microwave application. Although the saturation magnetisation of ferrites less than that of ferromagnetic alloys, they have advantages such as applicability at higher frequency, lower price and greater electrical resistance. Since 1950, soft ferrites have been widely studied and have become a field of interest of many researches because of their application potential in the modern electronics industry. The electrical and magnetic properties of these materials are structure sensitive and can be altered by doping or substitution. The substitution of aluminium in the inverse ferrites like Nickel, copper and cobalt ferrites have proved to be useful by increasing their saturation, magnetization, resistivity, however, at the cost of decrease of Curie temperature. Cadmium ferrite is a normal spinel ; its magnetic moment per unit cell is zero. Low magnetic high resistive ferrite are so applicable in the high frequency transformer cores. The addition of aluminium which has strong preference for the octahedral sites should exhibit the decrease of the magnetisation because aluminium is nonmagnetic. As aluminium content increases, the magnetic moment of unit cell decreases that means show triangular spin moment, their occurs a reduction in the sub lattice interaction. The removal of iron ions from magnetic sublattice and substitution of the nonmagnetic aluminium ion in its place weakens the magnetism. Due to this substitution improves catalytic, dielectric and magnetic properties, as they possess high resistivity and negligible eddy current losses.