SDC420T Memory Card

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Toshiba's Standard SD Cards Are the Perfect Way to Capture and Store Your Memories. the Series Is Compatible with Cameras

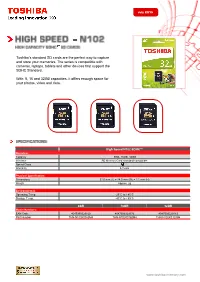

July 2015 Toshiba’s standard SD cards are the perfect way to capture and store your memories. The series is compatible with cameras, laptops, tablets and other devices that support the SDHC Standard. With 8, 16 and 32GB capacities, it offers enough space for your photos, video and data. High Speed N102 SDHC™ Overview: Capacity 8GB, 16GB, 32GB Interface SD Memory Card standard compatible Speed Class * Warranty 5 Years Physical Specification: Dimensions 32.0 mm (L) × 24.0 mm (W) × 2.1 mm (H) Weight Approx. 2g Environmental: Operating Temp. -25°C to +85°C Storage Temp. -40°C to +85°C 8GB 16GB 32GB Model Numbers: EAN Code 4047999329169 4047999329176 4047999329183 Part Number THN-N102K0080M4 THN-N102K0160M4 THN-N102K0320M4 www.toshiba-memory.com In 1984, Toshiba developed a new type of semiconductor memory called flash memory, leading the industry into the next generation ahead of its competitors. Some time later in 1987, NAND flash memory was developed, and this has since been used in a variety of memory cards and electronic equipments. The NAND flash market has grown rapidly, with flash memory becoming an internationally standardized memory device. Toshiba, the inventor of flash memory, has carved out a path to a new era in which we are all able to carry videos, music and data with us wherever we go. History of Flash Memory 1984 Developed NOR-type Flash Memory 1987 Developed NAND-type Flash Memory Jul. 2000 Released SD™ Memory Card Jun. 2003 Released miniSD™ Memory Card Dec. 2003 Released USB Flash Memory Jul. 2006 Released microSD™ Memory Card Oct. -

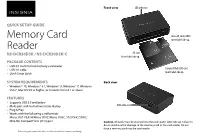

Memory Card Reader • USB 3.0 Cable Compactflash (CF) Card • Quick Setup Guide Insert Label Side Up

Front view LED indicator QUICK SETUP GUIDE Memory Card microSD, microSDXC Reader Insert label side up. NS-DCR30D3K / NS-DCR30D3K-C SD card Insert label side up. PACKAGE CONTENTS • USB 3.0 multi-format memory card reader • USB 3.0 cable CompactFlash (CF) card • Quick Setup Guide Insert label side up. SYSTEM REQUIREMENTS Back view • Windows® 10, Windows® 8.1, Windows® 8, Windows® 7, Windows Vista®, Mac OS 9.0 or higher, or Linux Kernal 2.4.1 or above FEATURES • Supports USB 3.0 and below • Multi-port and multi-driver letter display USB cable port • Plug & Play • Works with the following card formats: Micro SD/T-FLASH/Micro SDXC/Micro SDHC, SD/SDHC/SDXC/ Mini-SD, CompactFlash (CF) type I Caution: All cards must be inserted into the card reader label side up. Failure to do so could result in damage to the memory card or the card reader. Do not force a memory card into the card reader. Before using your new product, please read these instructions to prevent any damage. CONNECTING THE CARD READER 5 Do not remove your card from the card reader until the data LED Plug one end of a USB cable into the USB port of the card reader and stops blinking and the name of your card disappears from the Finder the other end into an available USB port on your computer. Your window. computer loads the drivers automatically. SPECIFICATIONS USING THE CARD READER • Dimensions: 2.87 × 1.98 × .68 in. (7.3 × 5.05 × 1.75 cm) Cautions: • Transmission port: USB 3.0 • Insert a card, label side up, into the appropriate slot. -

Capturemovemanipulates

CAPTUREMOVEMANIPULATESTORE Flash Memory Cards from Simpletech CompactFlash Secure Digital MultiMediaCard RS-MMC miniSD Flash Memory Cards from SimpleTech Capture your digital photos, music, and files with SimpleTech high-speed flash FLASHMEMORYCARDS memory cards. CompactFlash CompactFlash (CF) flash memory cards are the most popular form factor of flash storage used in consumer devices today. CF cards are ideal storage solutions for digital cameras, MP3 players, PDAs, palmtops, and handheld PCs. Features • Low power consumption • Compatible with all CF devices • Hot Swappable • CFA and PCMCIA Compliant • Highest Capacity Available using IC TowerTM Chip Stacking Capacities 32MB-4GB Dimension 1.69" (w) x 1.43" (l) x 0.13" (t) Weight 11.4g Interface ATA True IDE Operating Temperature 0o - 70o C Power 3.3V or 5V Operation Warranty Lifetime Secure Digital Secure Digital (SD) flash memory cards are next generation memory devices that offer a combination of high storage capacity, fast data transfer rates, great flexibility and excellent security. Features • Copyrights protection function • SD and SPI interface supported • Nonvolatile solid-state storage • Mechanical write protect switch Capacities 32MB - 1GB Dimension 0.94" (w) x 1.26" (l) x 0.08" (t) Weight 1g Interface Secure Digital Mode SPI Mode miniSD card adapter can be use in SD card socket Operating Temperature 0o - 70o C Power 2.7V - 3.6V Warranty Lifetime MultiMediaCard MultiMediaCards (MMC) flash memory cards are highly integrated flash products which let you carry more music, images, data, and voice recordings. MMC cards are small but rugged. They are great for MP3 players, digital cameras, voice recorders, smart phones and digital camcorders. -

In-Desk Hub 3 Port USB 3.0 + 2 Slot SD Card Reader

In-Desk Hub 3 Port USB 3.0 + 2 Slot SD Card Reader Description This hub by Delock can be installed into an existing cut-out of the desk with a diameter of 60 mm or 80 mm to lead through the cables for the monitor, keyboard and mouse. At the same time, the hub offers three USB Type-A female ports and one SD Card Reader with two slots. The data transfer and power supply is guaranteed through one USB 3.0 Type-A male and one USB 2.0 Type-A male. The distance between the free connectors can be maximum 20 cm, because the two cables are connected with each other. Specification Item no. 62869 • Connectors: EAN: 4043619628698 top side: 3 x USB 3.0 Type-A female Country of origin: China 1 x SD slot 1 x Micro SD slot Package: Retail Box bottom side: 1 x USB 3.0 Type-A male 1 x USB 2.0 Type-A male (power supply) • Chipset: VL813, GL3233 • Data transfer rate up to: SuperSpeed USB 5 Gbps, Hi-Speed 480 Mbps, Full-Speed 12 Mbps, Low-Speed 1.5 Mbps • The Card Reader supports following memory cards: 1. Slot Secure Digital SD, SD Pro, SD High Capacity (SDHC), SD Ultra, SDHC Ultra, SDXC, SDXC Ultra, MMC-I, MMC-II, MMC 4.0, Mini SD, Mini SDHC, MMCmobile, RS-MMC, RS-MMC 4.0 2. Slot Micro Secure Digital Micro SD, Micro SDHC, Micro SDHC Ultra, T-Flash, MMCmicro • Mounting diameter: 60 mm / 80 mm • Mounting depth: 35 mm • Cable length: ca. -

SD Express Memory Cards with Pcie® and Nvmetm Interfaces

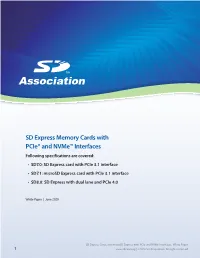

SD Express Memory Cards with PCIe® and NVMeTM Interfaces Following specifications are covered: • SD7.0: SD Express card with PCIe 3.1 interface • SD7.1: microSD Express card with PCIe 3.1 interface • SD8.0: SD Express with dual lane and PCIe 4.0 White Paper | June 2020 SD Express Cards and microSD Express with PCIe and NVMe Interfaces White Paper 1 www.sdcard.org | ©2020 SD Association. All rights reserved Conditions for publication Publisher and Copyright Holder: Disclaimers: SD Card Association The information contained in this whitepaper is provided as 5000 Executive Parkway, Suite 302 is without any representations or warranties of any kind. San Ramon, CA 94583 USA No responsibility is assumed by the SD Association for any Telephone: +1 (925) 275-6615 damages, or any infringements of patents or other rights of Fax: +1 (925) 886-4870 the SD Association or any third-parties, which may result E-mail: [email protected] from the use of any portion thereof. No license is granted by implication, estoppel or otherwise under any patent or other rights of the SD Association or any third-party. Nothing herein shall be construed as an obligation by the SD Association to disclose or distribute any technical information, know-how or other confidential information to any third party. Specifications are subject to change without notice. Nonmetric weights and measurements are approximate. All data were deemed correct a time of creation. SD Association is not liable for errors or omissions. All brand, product, service names and logos are trademarks and/or registered trademarks of their respective owners and are hereby recognized and acknowledged. -

EXCERIA PRO™ Storage Solutions Are Ideal

March 2017 EXCERIA PRO™ storage solutions are ideal for use in action-cameras and other wearables. M402 is perfect for 4K video recording in the fastest and toughest situations as well as for capacity expansion for your smartphone. The new Application Performance Class A1*1 gives you high confidence level and reliability when storing and running Android applications on microSD cards*2 at optimal levels. The series is made for hard conditions: waterproof, shockproof, X-Ray proof and temperature proof, plus the card inlcudes a data recovery software. The SD adaptor included with the M402 Package gives you a wide variety of use options. EXCERIA PRO™ M402 microSDHC™ & microSDXC™ Cards Overview: Capacity 16GB, 32GB, 64GB,128GB *3 Interface UHS-I Speed Class UHS Speed Class 3 *4 Write Speed Up to 95 MB/s *5 Read Speed Up to 95 MB/s Application Performance Class Class 1 *1 Random Read IOPS *1 1500 Write IOPS *1 500 Sustained Sequential performance 10MB/s Warranty 5 Years Physical Specification: Dimensions 15 mm (L) x 11 mm (W) x 1.0 mm (H) Weight Approx. 0.4g Environmental: Operating Temp. -25°C to +85°C Storage Temp. -40°C to +85°C 16GB 32GB 64GB 128GB Model Numbers: EAN Code 4047999410461 4047999410478 4047999410485 4047999410492 Part Number THN-M402S0160E2 THN-M402S0320E2 THN-M402S0640E2 THN-M402S1280E2 Blister Dimensions 152 mm (L) x 101mm (W) x 5mm (H) MOQ 10 pcs www.toshiba-memory.com In 1984, Toshiba developed a new type of semiconductor memory called flash memory, leading the industry into the next generation ahead of its competitors. -

Flash Memory and Micro SD Card

Flash Memory and Micro SD Card Presented by: Krishna Goyal (200601195) Anirudh Tripathi (200601141) OUTLINE • Memory • Volatile and Nonvolatile memory • EPROM and EEPROM memory • Flash memory • NAND and NOR Flash memory • Flash Memory operations • Advantage and Disadvantage of Embedded Over Stand Alone Flash Memory • Micro SD card • Summary • References Memory • The terms “storage” or “memory” refer to the parts of a digital computer that retain physical state (data) for some interval of time, possibly even after electrical power to the computer is turned off. • A computer system's memory is crucial to its operation; without memory, a computer could not read programs or retain data. Memory stores data electronically in memory cells contained in chips. It is usually measured in kilobytes, megabytes, or gigabytes. • Memory is classified into volatile and non-volatile memory. Memory Classification VOLATILE NON-VOLATILE SRAM ROM PROM DRAM EPROM EEPROM NVRAM Flash Memory Floppy Disk MRAM Hard Disk Magnetic Devices Volatile Memory • The most widely used form of primary storage today is a volatile form of random access memory, meaning that when the computer is shut down, anything contained in random access memory (RAM) is lost. • DRAM used for main memory • SRAM used for cache Non-Volatile memory • EEPROM, EPROM, FeRAM, FLASH, NVSRAM and ROM are different types of non-volatile memory. • The main differences are in the memories relative cost per bit and the flexibility to accommodate code changes. • nonvolatile memory, NVM or non-volatile storage, is computer memory that can retain the stored information even when not powered. EPROM • Erasable Programmable Read Only Memory also known as UV-EPROM is a form of non-volatile memory. -

HP Laptop 15-Db1153nm

Datasheet HP Laptop 15-db1153nm Quality performance and a long-lasting battery to tackle every day tasks Designed for long-lasting performance, this stylishly designed HP 39.6 cm (15.6") laptop has a long-lasting battery that keeps you connected, entertained, and productive all day. Speed through tasks, or sit back and socialize – with a powerful AMD processor3 and a rich HD1 or FHD2 display. Do it all, all day. *Product image may differ from actual product Responsive and reliable performance Sleek. Stylish. Powerful. Stay connected and entertained A laptop with the power to surf, stream,4 and do so A sleek and stylish design makes this eye-catching Stay connected and entertained with a long-lasting much more with an AMD processor3 and graphics laptop easy to take anywhere. With its beautiful HP Fast charge battery and visually rich display. Plus, options. Plus extensive quality testing ensures that brushed keyboard and color-matched hinge, the easily store and enjoy your favorite music, movies, you can keep going...and going. smartly designed HP 39.6 cm (15.6") laptop looks as and photos with ample storage. good as it performs. Datasheet HP Laptop 15-db1153nm Featuring 2nd Generation AMD Ryzen™ Mobile Processors DDR4 RAM Uplift your performance with 2nd Generation AMD Ryzen™ Mobile Designed to run more efficiently and more reliably at faster speeds, DDR4 is Processors. Multitask seamlessly with accelerated power and efficiency, while the future of RAM. With its higher bandwidth, everything from multi-tasking enjoying stunning visuals.5 to playing games gets a performance boost. AMD Radeon™ Vega graphics SuperSpeed USB Type-A 5Gbps signaling data rate Thrill your visual senses with the latest AMD graphics compute engines for Plug in your external storage with this SuperSpeed USB Type-A port, fast, powerful, and fluid graphics. -

HP Stream Laptop 11-Ak0502sa

Datasheet HP Stream Laptop 11-ak0502sa Study. Stream. Share. On a single charge. Between home, school, and work—your mobile life demands a PC that just doesn’t quit. With up to 13 hours and 15 minutes of battery life1, the HP Stream does everything your smartphone can’t. Post, play, and stay productive all day with the familiarity of a Windows PC that’s affordable, portable, and incredibly stylish. Extremely portable. Expressive design. More features. More value. Windows you love. Office you need. Live your best life on-the-go and in style with a slim, With Intel® processors and up to 13 hours and 15 Experience peace of mind that comes with the most expressive design. With its smooth finish and vertical minutes of battery life1, work all day or binge-watch secure Windows ever built. Designed to run powerful brushed pattern, the HP Stream that perfectly fits your favorite shows—all while staying under budget. Windows store apps exclusively—you can do it all your personality. Plus, stay connected with fast Wi-Fi, plenty of storage with Microsoft Edge, Bing Search, Windows Defender, options, and all the ports you need. and so much more. 1 Battery life estimates are based on battery wattage and capacity and will vary depending on various factors including product model, configuration, loaded applications, features, use, wireless functionality, and power management settings. The maximum capacity of the battery will naturally decrease with time and usage. Datasheet HP Stream Laptop 11-ak0502sa Featuring Windows 10 in S Mode 32 GB eMMC storage Experience the most secure Windows ever built. -

Memory Card Guide for Photos and Videos You + Right Shot = Unforgettable Moment

Memory Card Guide for photos and videos you + right shot = unforgettable moment Whether you want to capture, share or preserve, we have the perfect solution for you. We've pioneered and innovated the technology of flash memory for over 20 years. And we will continue with what we do best so you can continue with what you do best. Store your world in ours® Standard Standard Dependability and solid performance you can count on to capture and store your favorite pictures and videos on your point and shoot camera. Enhanced Standard You'll benefit from ultra-fast transfer speed and enhanced performance for Full HD1 video (1080p) with quality you can trust. Advanced For increased speed and performance to capture fast-action photos in quick succession and Full HD1 and 3D videos. Ultimate Delivers the ultimate in speed to experience Performance RAW+JPEG continuous burst mode shooting and captures fast-action Full HD1 (1080p), 3D and cinema quality 4K video recording like never before. Count on this professional grade memory card to get the shot. SanDisk® SDHC™/SDXC™ Memory Cards Setting the standard Dependability and solid performance you can count on to capture and store your favorite pictures and videos on your point and shoot camera. Writeable label for easy identification and organization; start building your digital library CAPACITIES 4 | 8 | 16 | 32 | 64 GB** IDEAL FOR POINT-AND-SHOOT VIDEO CAMERAS CAMERAS DURABILITY SanDisk Ultra® SDHC™/SDXC™ UHS-I Cards Capture amazing pictures and stunning Full HD1 video Twice as fast as ordinary SDHC cards2. Experience faster downloads, increased capacity and high performance. -

Part 2 FILE SYSTEM SPECIFICATION

SD Memory Card Specifications Part 2 FILE SYSTEM SPECIFICATION Version 1.0 February 2000 Standard SD Group Matsushita Electric Industrial Co., Ltd. (MEI) SanDisk Corporation ToshibaMicrosystems Corporation CONFIDENTIAL Standard Microsystems SD Memory Card Specifications / Part 2. File System Specification Version 1.0 Conditions for publication Publisher and Copyright Holder SD Group(MEI, SanDisk, Toshiba) Confidentiality This document shall be treated as confidential under the Non Disclosure Agreement which has been signed by the obtainer. Reproduction in whole or in part is prohibited without prior written permission of SD Group. Exemption None will be liable for any damages from use of this document. Standard Microsystems DO NOT COPY ã2000 SD Group (MEI, SanDisk, Toshiba). FS-0 CONFIDENTIAL SD Memory Card Specifications / Part 2. File System Specification Version 1.0 This page is intentionally left blank. Standard Microsystems DO NOT COPY ã2000 SD Group (MEI, SanDisk, Toshiba). CONFIDENTIAL SD Memory Card Specifications / Part 2. File System Specification Version 1.0 Part2 FILE SYSTEM SPECIFICATION 1. General.............................................................................................................................................................. FS-1 1.1 Scope ..................................................................................................................................................................... 1 1.2 Normative References ....................................................................................................................................... -

Flash Memory

Semiconductor Catalog Mar. 2016 Flash Memory STORAGE PRODUCTS & SEMICONDUCTOR SEMICONDUCTOR & STORAGE PRODUCTS http://toshiba.semicon-storage.com/ FlashF l ash M emor Memoryy Toshiba, the inventor of Flash Memory, blazed the trail to a world we can all carry data, music and videos with us, wherever we go. Now, Flash Memory is playing a major role in driving the evolution of automobiles and industrial equipment that is essential for realizing an environmentally friendly society. Behind the scenes, Flash Memory supports the world’s continuing transformation to a better tomorrow. Back in 1984, Toshiba developed a new semiconductor memory, Flash Memory, and by doing led the industry, and its competitors, into the next generation. Today the international de facto standard, Flash Memories have realized an immense range of applications that include Memory Cards, Solid-State Drives (SSDs), and even industrial equipment. As the total volume of information continues its exponential growth, demand for storage units using Flash Memories will grow with it. In order to meets these market needs, Toshiba has made major investments in plant and equipment at its Yokkaichi memory fab, and is resolutely committed to develop new products. This brochure highlights Toshiba's Flash Memory and other Memory Solutions. Toshiba's Leading Technology Areas Features of Toshiba's Flash Memory W Process W Fast storage of large files W Multi-Level Cell (MLC) W Fast write and erase rates W Controller W Low per-bit cost W Die stacking W Easily extendable using the NAND Flash Memory interface W Packaging W Extensive product portfolio to meet diverse needs OProducts with the standard HS-MMC interface OOffers products with the high-speed UHS-I and UHS-II SD bus interfaces OAvailable as SD Memory Cards with unique features – 2 – Toshiba's Flash Memory and controller technologies have found a wide range of applications.