Architecture of the Super NES Jacob Klassen & Thomas Papish Overview - Super Nintendo Entertainment System

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

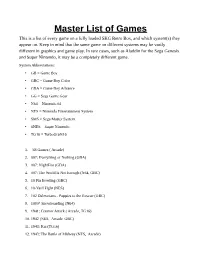

Master List of Games This Is a List of Every Game on a Fully Loaded SKG Retro Box, and Which System(S) They Appear On

Master List of Games This is a list of every game on a fully loaded SKG Retro Box, and which system(s) they appear on. Keep in mind that the same game on different systems may be vastly different in graphics and game play. In rare cases, such as Aladdin for the Sega Genesis and Super Nintendo, it may be a completely different game. System Abbreviations: • GB = Game Boy • GBC = Game Boy Color • GBA = Game Boy Advance • GG = Sega Game Gear • N64 = Nintendo 64 • NES = Nintendo Entertainment System • SMS = Sega Master System • SNES = Super Nintendo • TG16 = TurboGrafx16 1. '88 Games ( Arcade) 2. 007: Everything or Nothing (GBA) 3. 007: NightFire (GBA) 4. 007: The World Is Not Enough (N64, GBC) 5. 10 Pin Bowling (GBC) 6. 10-Yard Fight (NES) 7. 102 Dalmatians - Puppies to the Rescue (GBC) 8. 1080° Snowboarding (N64) 9. 1941: Counter Attack ( Arcade, TG16) 10. 1942 (NES, Arcade, GBC) 11. 1943: Kai (TG16) 12. 1943: The Battle of Midway (NES, Arcade) 13. 1944: The Loop Master ( Arcade) 14. 1999: Hore, Mitakotoka! Seikimatsu (NES) 15. 19XX: The War Against Destiny ( Arcade) 16. 2 on 2 Open Ice Challenge ( Arcade) 17. 2010: The Graphic Action Game (Colecovision) 18. 2020 Super Baseball ( Arcade, SNES) 19. 21-Emon (TG16) 20. 3 Choume no Tama: Tama and Friends: 3 Choume Obake Panic!! (GB) 21. 3 Count Bout ( Arcade) 22. 3 Ninjas Kick Back (SNES, Genesis, Sega CD) 23. 3-D Tic-Tac-Toe (Atari 2600) 24. 3-D Ultra Pinball: Thrillride (GBC) 25. 3-D WorldRunner (NES) 26. 3D Asteroids (Atari 7800) 27. -

Using the ZMET Method to Understand Individual Meanings Created by Video Game Players Through the Player-Super Mario Avatar Relationship

Brigham Young University BYU ScholarsArchive Theses and Dissertations 2008-03-28 Using the ZMET Method to Understand Individual Meanings Created by Video Game Players Through the Player-Super Mario Avatar Relationship Bradley R. Clark Brigham Young University - Provo Follow this and additional works at: https://scholarsarchive.byu.edu/etd Part of the Communication Commons BYU ScholarsArchive Citation Clark, Bradley R., "Using the ZMET Method to Understand Individual Meanings Created by Video Game Players Through the Player-Super Mario Avatar Relationship" (2008). Theses and Dissertations. 1350. https://scholarsarchive.byu.edu/etd/1350 This Thesis is brought to you for free and open access by BYU ScholarsArchive. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of BYU ScholarsArchive. For more information, please contact [email protected], [email protected]. Using the ZMET Method 1 Running head: USING THE ZMET METHOD TO UNDERSTAND MEANINGS Using the ZMET Method to Understand Individual Meanings Created by Video Game Players Through the Player-Super Mario Avatar Relationship Bradley R Clark A project submitted to the faculty of Brigham Young University in partial fulfillment of the requirements for the degree of Master of Arts Department of Communications Brigham Young University April 2008 Using the ZMET Method 2 Copyright © 2008 Bradley R Clark All Rights Reserved Using the ZMET Method 3 Using the ZMET Method 4 BRIGHAM YOUNG UNIVERSITY GRADUATE COMMITTEE APPROVAL of a project submitted by Bradley R Clark This project has been read by each member of the following graduate committee and by majority vote has been found to be satisfactory. -

Video Game Trader Magazine & Price Guide

Winter 2009/2010 Issue #14 4 Trading Thoughts 20 Hidden Gems Blue‘s Journey (Neo Geo) Video Game Flashback Dragon‘s Lair (NES) Hidden Gems 8 NES Archives p. 20 19 Page Turners Wrecking Crew Vintage Games 9 Retro Reviews 40 Made in Japan Coin-Op.TV Volume 2 (DVD) Twinkle Star Sprites Alf (Sega Master System) VectrexMad! AutoFire Dongle (Vectrex) 41 Video Game Programming ROM Hacking Part 2 11Homebrew Reviews Ultimate Frogger Championship (NES) 42 Six Feet Under Phantasm (Atari 2600) Accessories Mad Bodies (Atari Jaguar) 44 Just 4 Qix Qix 46 Press Start Comic Michael Thomasson’s Just 4 Qix 5 Bubsy: What Could Possibly Go Wrong? p. 44 6 Spike: Alive and Well in the land of Vectors 14 Special Book Preview: Classic Home Video Games (1985-1988) 43 Token Appreciation Altered Beast 22 Prices for popular consoles from the Atari 2600 Six Feet Under to Sony PlayStation. Now includes 3DO & Complete p. 42 Game Lists! Advertise with Video Game Trader! Multiple run discounts of up to 25% apply THIS ISSUES CONTRIBUTORS: when you run your ad for consecutive Dustin Gulley Brett Weiss Ad Deadlines are 12 Noon Eastern months. Email for full details or visit our ad- Jim Combs Pat “Coldguy” December 1, 2009 (for Issue #15 Spring vertising page on videogametrader.com. Kevin H Gerard Buchko 2010) Agents J & K Dick Ward February 1, 2009(for Issue #16 Summer Video Game Trader can help create your ad- Michael Thomasson John Hancock 2010) vertisement. Email us with your requirements for a price quote. P. Ian Nicholson Peter G NEW!! Low, Full Color, Advertising Rates! -

The Making of Star Fox Welcome to My First Newshounds Article of 2019

The Making Of Star Fox Welcome to my first Newshounds article of 2019-2020! It’s that time once again of a new school year, which means a whole new batch of articles to publish! There’s a bunch of great articles that I’ve planned for this year, so before we dive into this article, let’s recap which articles I published last year! We started off the previous year with a Q&A about myself, where students could give me questions to answer! Let’s say there were some interesting ones in there! Christmas was approaching at a rapid pace and before the big day arrived, we delved into the history of Apple’s iPhone and we realised how far technology has come since the late 2000’s. After that, we entered the construction site to delve into the deepest blueprints of Blackpool Pleasure Beach’s latest rollercoaster ICON! Finally, we all came as one to choose which article to be published next. We ended up taking look at the history of Sonic The Hedgehog at Alton Towers, which covered over a quarter of a century to produce! Anyways enough rambling on, let’s get the ball rolling! Nowadays, gaming has come an extremely long way since its inception, but back in the ‘90’s we were restricted in technology compared to what we have today. However, today we are going to look at singlehandedly THE game that brought the world of 3D to home consoles. Welcome to the making of… WARNING: There may some terms that may be hard to understand. -

Concert Program

Gamer Symphony Orchestra Spring 2014 Concert Saturday, May 3, 2014, 2 p.m. Dekelboum Concert Hall Clarice Smith Performing Arts Center Jacob Coppage-Gross, Conductor Kevin Mok, Conductor Kyle G. Jamolin, Choral Director Bryan Doyle, Assistant Conductor About the GSO In the fall of 2005, student violist Michelle Eng sought to create an orchestral group that played video game music. With a half-dozen others from the University of Maryland Repertoire Orchestra, she founded GSO to achieve that dream. By the time of the ensemble’s first public performance in spring 2006, its size had quadrupled. Today GSO provides a musical and social outlet to 120 members. It is the world’s first collegiate ensemble to draw its repertoire exclusively from the soundtracks of video games. The ensemble is entirely student run, which includes conducting and musical arranging. In February of 2012 the GSO collaborated with Video Games Live!, for the performances at the Strathmore in Bethesda, Md. The National Philharmonic per- formed the GSO’s arrangement of “Korobeiniki” from Tetris to two sold-out houses. In May of 2012 the GSO was invited to perform as part of the Smithsonian’s The Art of Video Games exhibit. Aside from its concerts, GSO also holds the “Deathmatch for Charity” (renamed the “Gamer Olympics” this year) video game tournament every spring. All proceeds benefit Children’s National Medical Center in Washington, D.C. Find GSO online at UMD.gamersymphony.org Beyond the GSO The GSO has also fostered the creation of a multitude of other collegiate GSOs at California State University—Northridge, Ithaca College, Montclair State University, the University of California—Los Angeles, the University of Delaware, and West Char- ter University. -

Vintage Game Consoles: an INSIDE LOOK at APPLE, ATARI

Vintage Game Consoles Bound to Create You are a creator. Whatever your form of expression — photography, filmmaking, animation, games, audio, media communication, web design, or theatre — you simply want to create without limitation. Bound by nothing except your own creativity and determination. Focal Press can help. For over 75 years Focal has published books that support your creative goals. Our founder, Andor Kraszna-Krausz, established Focal in 1938 so you could have access to leading-edge expert knowledge, techniques, and tools that allow you to create without constraint. We strive to create exceptional, engaging, and practical content that helps you master your passion. Focal Press and you. Bound to create. We’d love to hear how we’ve helped you create. Share your experience: www.focalpress.com/boundtocreate Vintage Game Consoles AN INSIDE LOOK AT APPLE, ATARI, COMMODORE, NINTENDO, AND THE GREATEST GAMING PLATFORMS OF ALL TIME Bill Loguidice and Matt Barton First published 2014 by Focal Press 70 Blanchard Road, Suite 402, Burlington, MA 01803 and by Focal Press 2 Park Square, Milton Park, Abingdon, Oxon OX14 4RN Focal Press is an imprint of the Taylor & Francis Group, an informa business © 2014 Taylor & Francis The right of Bill Loguidice and Matt Barton to be identified as the authors of this work has been asserted by them in accordance with sections 77 and 78 of the Copyright, Designs and Patents Act 1988. All rights reserved. No part of this book may be reprinted or reproduced or utilised in any form or by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying and recording, or in any information storage or retrieval system, without permission in writing from the publishers. -

Nintendo: the Illusive Competitive Advantage Luke Nguyen Raymond

Nintendo: The Illusive Competitive Advantage Luke Nguyen Raymond Estrella Toan Bui James Crosby Don Hatley Jeremy Westerman The University of Texas at Dallas Nintendo: The Illusive Competitive Advantage 1 History The video game industry owes much of its popularity generated today to one company: Nintendo. From its beginnings in the late nineteenth century, Nintendo has proven the ability to survive throughout dire circumstances, but the challenging dynamics of the video game industry proved companies could not survive without adapting a variety of business strategies. In 1889, Nintendo was established by Fusajiro Yamauchi and began as a card company (Jones, 2013), producing playing cards similar to those found in casinos and game parlors. The company maintained this simple product line for over 50 years until the grandson of Fusajiro, Hiroshi Yamauchi, took over the company and began to explore ways to expand the business. Solidifying the first game card licensing deal in 1959, Yamauchi agreed to produce playing cards for Disney’s iconic characters, bringing in significant revenue and a change of pace from the arena of gambling. Success driven, Yamauchi expanded the company into “non-game related markets which included taxi services, hotels, and even the food industry, all which failed” (Cohen, 2014). Taking to a host of different ventures while continuing to produce the majority of products for the playing card market, the company fell into debt and was at risk of facing bankruptcy. Nintendo needed to reinvent itself and did so by deciding to manufacture toys for children and hired engineers to develop and run the production lines. -

Keeping the Game Alive: Evaluating Strategies for the Preservation of Console Video Games

64 Keeping the Game Alive The International Journal of Digital Curation Issue 1, Volume 5 | 2010 Keeping the Game Alive: Evaluating Strategies for the Preservation of Console Video Games Mark Guttenbrunner, Christoph Becker, Andreas Rauber, Vienna University of Technology Abstract Interactive fiction and video games are part of our cultural heritage. As original systems cease to work because of hardware and media failures, methods to preserve obsolete video games for future generations have to be developed. The public interest in early video games is high, as exhibitions, regular magazines on the topic and newspaper articles demonstrate. Moreover, games considered to be classic are rereleased for new generations of gaming hardware. However, with the rapid development of new computer systems, the way games look and are played changes constantly. When trying to preserve console video games one faces problems of classified development documentation, legal aspects and extracting the contents from original media like cartridges with special hardware. Furthermore, special controllers and non-digital items are used to extend the gaming experience making it difficult to preserve the look and feel of console video games. This paper discusses strategies for the digital preservation of console video games. After a short overview of console video game systems, there follows an introduction to digital preservation and related work in common strategies for digital preservation and preserving interactive art. Then different preservation strategies are described with a specific focus on emulation. Finally a case study on console video game preservation is shown which uses the Planets preservation planning approach for evaluating preservation strategies in a documented decision-making process. -

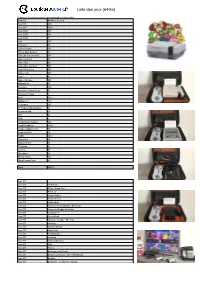

Website Listing Ajax

Liste des jeux (64Go) Cliquez sur le nom des consoles pour descendre au bon endroit Console Nombre de jeux Atari ST 274 Atari 800 5627 Atari 2600 457 Atari 5200 101 Atari 7800 51 C64 150 Channel F 34 Coleco Vision 151 Family Disk System 43 FBA Libretro (arcade) 647 Game & watch 58 Game Boy 621 Game Boy Advance 951 Game Boy Color 501 Game gear 277 Lynx 84 Mame (arcade) 808 Nintento 64 78 Neo-Geo 152 Neo-Geo Pocket Color 81 Neo-Geo Pocket 9 NES 1812 Odyssey 2 125 Pc Engine 291 Pc Engine Supergraphx 97 Pokémon Mini 26 PS1 54 PSP 2 Sega Master System 288 Sega Megadrive 1030 Sega megadrive 32x 30 Sega sg-1000 59 SNES 1461 Stellaview 66 Sufami Turbo 15 Thomson 82 Vectrex 75 Virtualboy 24 Wonderswan 102 WonderswanColor 83 Total 16877 Atari ST Atari ST 10th Frame Atari ST 500cc Grand Prix Atari ST 5th Gear Atari ST Action Fighter Atari ST Action Service Atari ST Addictaball Atari ST Advanced Fruit Machine Simulator Atari ST Advanced Rugby Simulator Atari ST Afterburner Atari ST Alien World Atari ST Alternate Reality - The City Atari ST Anarchy Atari ST Another World Atari ST Apprentice Atari ST Archipelagos Atari ST Arcticfox Atari ST Artificial Dreams Atari ST Atax Atari ST Atomix Atari ST Backgammon Royale Atari ST Balance of Power - The 1990 Edition Atari ST Ballistix Atari ST Barbarian : Le Guerrier Absolu Atari ST Battle Chess Atari ST Battle Probe Atari ST Battlehawks 1942 Atari ST Beach Volley Atari ST Beastlord Atari ST Beyond the Ice Palace Atari ST Black Tiger Atari ST Blasteroids Atari ST Blazing Thunder Atari ST Blood Money Atari ST BMX Simulator Atari ST Bob Winner Atari ST Bomb Jack Atari ST Bumpy Atari ST Burger Man Atari ST Captain Fizz Meets the Blaster-Trons Atari ST Carrier Command Atari ST Cartoon Capers Atari ST Catch 23 Atari ST Championship Baseball Atari ST Championship Cricket Atari ST Championship Wrestling Atari ST Chase H.Q. -

Super Everdrive V2 User Manual

Super EverDrive V2 User Manual www.krikzz.com 29.11.2013 Features: • Max. ROM size up to 7Mbyte • Return to menu after reset • SRAM auto backup on SD card • Supported SD/MMC up to 32GB • FAT16 and FAT32 are supported • GameGenie cheat codes • Simple menu • Connection to PC and any additional software is not require New cartridge has improved user interface, Game Genie cheats support, better compatibility with pirate ROMs. Games loads faster now. Super EverDrive V2 loads the OS directly from SD card at each startup, instead of flashing OS to internal flash memory, it allows to avoid possible damage to the cart during an OS update. Multi region CIC chip allow to use cart with any SNES/SFC system. Preparation required for the cart to work: • Download snesos-v*.zip from http://krikzz.com • Unzip archive content to the root folder of SD card • Unzip ROM files and copy them to SD card; • Insert SD card into cartridge; (It is not recommended to put a lot of files in a single folder, the cart will not display more than 1024 files per folder. Folders with large amount of files inside may open slowly. It would be better to make a few folders with alphabetic names and put the ROM files in these folders.) With the cart inserted and the SD prepared as instructed above you can then turn on your system, choose a ROM, invoke the file menu with the B button and run the game. File Browser Controls: B – Open the folder or open file menu A – Back to sub folder SELECT – Open main menu START – Run last selected game Yellow color display folders, gray color for files. -

ZSNES V1.51 Documentation

ZSNES v1.51 Documentation ================================ N a v i g a t i o n ================================ * Index [Index.txt] * Readme [Readme.txt] * GUI [GUI.txt] * Netplay [Netplay.txt] * Advanced Usage [Advanced.txt] * Games [Games.txt] 1. ROMs 2. Compatibility 3. Special-Chip Games 4. Special Cartridges - BS-X (Satellaview) - Super Gameboy 5. Individual Game Issues 6. Games Supported by ManyMouse 7. Multiplayer List * FAQ [FAQ.txt] - - - - - - - - - - - - - - - - - - * Getting Support [Support.txt] * History [History.txt] * About [About.txt] * License [License.txt] - - - - - - - - - - - - - - - - - - * NSRT Guide: [http://zsnes-docs.sf.net/nsrt] * ZSNES Home Page: [ZSNES.com] ================================================================================ ~ G a m e s ================================================================================ ............................................................ 1. ROMS ............................................................ ** ROMs are not included with ZSNES!!! ** You must find them on your own. Please read Wikipedia's article on ROM Images for a general overview. [http://en.wikipedia.org/wiki/ROM_image] In relation to SNES emulation, a "ROM image" is a computer file which is an exact copy of the data that is contained in a 'R'ead 'O'nly 'M'emory chip inside a game cartridge. This file contains the same data that a real SNES console reads from the game cartridge. An SNES emulator loads this ROM into its own memory, very much like how a real SNES operates. A problem appears when you have a ROM image that is not an exact copy of the data on a real SNES cartridge. Many of the ROMs available for download on the Internet are not in fact exact copies of real SNES games. There are a variety of reasons why a ROM that appears to be a real game is not an exact copy of the cartridge data. -

Usage of Today's Technology in Creating Authentic '8-Bit' and '1

CALIFORNIA STATE UNIVERSITY, NORTHRIDGE Renegade Drive: Usage of Today’s Technology in Creating Authentic ‘8-bit’ and ‘16-bit’ Video Game Experiences A thesis submitted in partial fulfillment of the requirements For the degree of Master of Science in Computer Science By Christian Guillermo Bowles December 2017 Copyright by Christian Guillermo Bowles 2017 ii The thesis of Christian Guillermo Bowles is approved: ______________________________ ____________ Prof. Caleb Owens Date ______________________________ ____________ Dr. Robert McIlhenny Date ______________________________ ____________ Dr. Li Liu, Chair Date California State University, Northridge iii Acknowledgements The author wishes to thank the following individuals and organizations for their contributions and support towards this thesis project: • Doris Chaney • Dr. G. Michael Barnes • Dr. Richard Covington • Dr. Peter Gabrovsky • Dr. Ani Nahapetian • Lauren X. Pham • Chase Bethea • Caleb Andrews • Sean Velasco • Ian Flood • Nick Wozniak • David D’Angelo • Shannon Hatakeda • Jake Kaufman • CSUN Game Development Club • Animation Student League of Northridge • CSUN Anime Club • Yacht Club Games • Mint Potion TV iv Table of Contents Signature Page iii Acknowledgements iv List of Figures x List of Tables xiv Abstract xv Introduction 1 Chapter 1: Hardware Limitations of the Nintendo Entertainment System 3 • Screen Resolution 3 • Tile Patterns 4 • Layers 4 • Sprites 6 • Palettes 7 • Audio 8 • Input 10 Chapter 2: Hardware Limitations of the Sega Master System 12 • Screen Resolution 12