A Survey of Enabling Technologies in Successful Consumer Digital Imaging Products

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

SECOND AMENDED COMPLAINT 3:14-Cv-582-JD

Case 3:14-cv-00582-JD Document 51 Filed 11/10/14 Page 1 of 19 1 EDUARDO G. ROY (Bar No. 146316) DANIEL C. QUINTERO (Bar No. 196492) 2 JOHN R. HURLEY (Bar No. 203641) PROMETHEUS PARTNERS L.L.P. 3 220 Montgomery Street Suite 1094 San Francisco, CA 94104 4 Telephone: 415.527.0255 5 Attorneys for Plaintiff 6 DANIEL NORCIA 7 UNITED STATES DISTIRCT COURT 8 NORTHERN DISTRICT OF CALIFORNIA 9 DANIEL NORCIA, on his own behalf and on Case No.: 3:14-cv-582-JD 10 behalf of all others similarly situated, SECOND AMENDED CLASS ACTION 11 Plaintiffs, COMPLAINT FOR: 12 v. 1. VIOLATION OF CALIFORNIA CONSUMERS LEGAL REMEDIES 13 SAMSUNG TELECOMMUNICATIONS ACT, CIVIL CODE §1750, et seq. AMERICA, LLC, a New York Corporation, and 2. UNLAWFUL AND UNFAIR 14 SAMSUNG ELECTRONICS AMERICA, INC., BUSINESS PRACTICES, a New Jersey Corporation, CALIFORNIA BUS. & PROF. CODE 15 §17200, et seq. Defendants. 3. FALSE ADVERTISING, 16 CALIFORNIA BUS. & PROF. CODE §17500, et seq. 17 4. FRAUD 18 JURY TRIAL DEMANDED 19 20 21 22 23 24 25 26 27 28 1 SECOND AMENDED COMPLAINT 3:14-cv-582-JD Case 3:14-cv-00582-JD Document 51 Filed 11/10/14 Page 2 of 19 1 Plaintiff DANIEL NORCIA, having not previously amended as a matter of course pursuant to 2 Fed.R.Civ.P. 15(a)(1)(B), hereby exercises that right by amending within 21 days of service of 3 Defendants’ Motion to Dismiss filed October 20, 2014 (ECF 45). 4 Individually and on behalf of all others similarly situated, Daniel Norcia complains and alleges, 5 by and through his attorneys, upon personal knowledge and information and belief, as follows: 6 NATURE OF THE ACTION 7 1. -

Device Support for Beacon Transmission with Android 5+

Device Support for Beacon Transmission with Android 5+ The list below identifies the Android device builds that are able to transmit as beacons. The ability to transmit as a beacon requires Bluetooth LE advertisement capability, which may or may not be supported by a device’s firmware. Acer T01 LMY47V 5.1.1 yes Amazon KFFOWI LVY48F 5.1.1 yes archos Archos 80d Xenon LMY47I 5.1 yes asus ASUS_T00N MMB29P 6.0.1 yes asus ASUS_X008D MRA58K 6.0 yes asus ASUS_Z008D LRX21V 5.0 yes asus ASUS_Z00AD LRX21V 5.0 yes asus ASUS_Z00AD MMB29P 6.0.1 yes asus ASUS_Z00ED LRX22G 5.0.2 yes asus ASUS_Z00ED MMB29P 6.0.1 yes asus ASUS_Z00LD LRX22G 5.0.2 yes asus ASUS_Z00LD MMB29P 6.0.1 yes asus ASUS_Z00UD MMB29P 6.0.1 yes asus ASUS_Z00VD LMY47I 5.1 yes asus ASUS_Z010D MMB29P 6.0.1 yes asus ASUS_Z011D LRX22G 5.0.2 yes asus ASUS_Z016D MXB48T 6.0.1 yes asus ASUS_Z017DA MMB29P 6.0.1 yes asus ASUS_Z017DA NRD90M 7.0 yes asus ASUS_Z017DB MMB29P 6.0.1 yes asus ASUS_Z017D MMB29P 6.0.1 yes asus P008 MMB29M 6.0.1 yes asus P024 LRX22G 5.0.2 yes blackberry STV100-3 MMB29M 6.0.1 yes BLU BLU STUDIO ONE LMY47D 5.1 yes BLUBOO XFire LMY47D 5.1 yes BLUBOO Xtouch LMY47D 5.1 yes bq Aquaris E5 HD LRX21M 5.0 yes ZBXCNCU5801712 Coolpad C106-7 291S 6.0.1 yes Coolpad Coolpad 3320A LMY47V 5.1.1 yes Coolpad Coolpad 3622A LMY47V 5.1.1 yes 1 CQ CQ-BOX 2.1.0-d158f31 5.1.1 yes CQ CQ-BOX 2.1.0-f9c6a47 5.1.1 yes DANY TECHNOLOGIES HK LTD Genius Talk T460 LMY47I 5.1 yes DOOGEE F5 LMY47D 5.1 yes DOOGEE X5 LMY47I 5.1 yes DOOGEE X5max MRA58K 6.0 yes elephone Elephone P7000 LRX21M 5.0 yes Elephone P8000 -

Network and Device Forensic Analysis of Android Social-Messaging Applications

DIGITAL FORENSIC RESEARCH CONFERENCE Network And Device Forensic Analysis Of Android Social-Messaging Applications By Daniel Walnycky, Ibrahim Baggili, Andrew Marrington, Frank Breitinger and Jason Moore Presented At The Digital Forensic Research Conference DFRWS 2015 USA Philadelphia, PA (Aug 9th - 13th) DFRWS is dedicated to the sharing of knowledge and ideas about digital forensics research. Ever since it organized the first open workshop devoted to digital forensics in 2001, DFRWS continues to bring academics and practitioners together in an informal environment. As a non-profit, volunteer organization, DFRWS sponsors technical working groups, annual conferences and challenges to help drive the direction of research and development. http:/dfrws.org Network'and'device'forensic'analysis'of'' Android'socialOmessaging'applica=ons' Daniel'Walnycky,'Ibrahim'Baggili,'Andrew'Marrington,' Jason'Moore,'Frank'Brei=nger' Graduate'Research'Assistant,'UNHcFREG'Member' Presen=ng'@'DFRWS,'Philadelphia,'PA,'2015' Agenda' • Introduc=on' • Related'work' • Methodology' • Experimental'results' • Discussion'and'conclusion' • Future'work' • Datapp' 2' Introduc=on' Tested'20'Android'messaging'apps'for'“low'hanging'fruit”'a.k.a'unencrypted'data:' • on'the'device,'in'network'traffic,'and'on'server'storage' Found'eviden=ary'traces:'passwords,'screen'shots,'text,'images,'videos,'audio,'GPS' loca=on,'sketches,'profile'pictures,'and'more…' 3' Related'work' • Forensic'value'of'smartphone'messages:' • Smartphones'may'contain'the'same'rich'variety'of'digital'evidence'which'might'be'found'on'a'computer' -

Terraillon Wellness Coach Supported Devices

Terraillon Wellness Coach Supported Devices Warning This document lists the smartphones compatible with the download of the Wellness Coach app from the App Store (Apple) and Play Store (Android). Some models have been tested by Terraillon to check the compatibility and smooth operation of the Wellness Coach app. However, many models have not been tested. Therefore, Terraillon doesn't ensure the proper functioning of the Wellness Coach application on these models. If your smartphone model does not appear in the list, thank you to send an email to [email protected] giving us the model of your smartphone so that we can activate if the application store allows it. BRAND MODEL NAME MANUFACTURER MODEL NAME OS REQUIRED ACER Liquid Z530 acer_T02 Android 4.3+ ACER Liquid Jade S acer_S56 Android 4.3+ ACER Liquid E700 acer_e39 Android 4.3+ ACER Liquid Z630 acer_t03 Android 4.3+ ACER Liquid Z320 T012 Android 4.3+ ARCHOS 45 Helium 4G a45he Android 4.3+ ARCHOS 50 Helium 4G a50he Android 4.3+ ARCHOS Archos 45b Helium ac45bhe Android 4.3+ ARCHOS ARCHOS 50c Helium ac50che Android 4.3+ APPLE iPhone 4S iOS8+ APPLE iPhone 5 iOS8+ APPLE iPhone 5C iOS8+ APPLE iPhone 5S iOS8+ APPLE iPhone 6 iOS8+ APPLE iPhone 6 Plus iOS8+ APPLE iPhone 6S iOS8+ APPLE iPhone 6S Plus iOS8+ APPLE iPad Mini 1 iOS8+ APPLE iPad Mini 2 iOS8+ 1 / 48 www.terraillon.com Terraillon Wellness Coach Supported Devices BRAND MODEL NAME MANUFACTURER MODEL NAME OS REQUIRED APPLE iPad Mini 3 iOS8+ APPLE iPad Mini 4 iOS8+ APPLE iPad 3 iOS8+ APPLE iPad 4 iOS8+ APPLE iPad Air iOS8+ -

BPOD-I2498 HTC One M7 Lollipop SU-V8.Indd

Android 5.0 operating system update for your HTC ONE®. Software Version: SU6A - Build Number: 5.28.605.12; Baseband: 1.13.41.1209 SU6B - Build Number: 6.21.605.3; Baseband: 1.13.41.1209 Verizon Wireless is pleased to announce an operating system update to Android 5.0 Lollipop. This version brings Android beyond smartphones and tablets, allowing access to apps and Android services on other connected screens like TV’s, cars and wearables. The new material design offers complex animations and 3-D views, 64-bit ABI support and improved runtime. NOTIFICATION PANEL • Lollipop Notification Panel behavior has been adopted • Swipe down once for Notifications • Swipe down a second time for Quick Settings • Toggle Button from KitKat has been replaced by Settings LOCK SCREEN • Lollipop Notification style has been adopted The following Sense settings have been removed • Security > Enable lock screen widgets • Security > Notification Settings • Security > Bypass lock screen on wake HTC One® | For step-by-step instructions on how to perform the download, please visit www.verizonwireless.com/htconeupdate | Data Usage Applies. © 2015 Verizon Wireless. 0315-I2498 1 2 3 HTC ONE LOLLIPOP SETTINGS • “Sound” has been changed to “Sound & notification” in Settings • Notification light settings have been moved to “Sound & notification” • Calendar Picker View offers dropdown capabilities • Search function has been added to settings • Date & Time settings have been reordered • Syncing with new Google Settings and adding in Accessibility • Switch Access • Color Inversion • Color Correction • High Contrast Text • “Sidetone” will be added as a Call Setting, which provides audible feedback to the caller CLOCK • World Clock Globe has been removed for memory considerations | For step-by-step instructions on how to perform the download, please visit www.verizonwireless.com/htconeupdate | Data Usage Applies. -

Brand Old Device

# New Device Old Device - Brand Old Device - Model Name 1 Galaxy A6+ Asus Asus Zenfone 2 Laser ZE500KL 2 Galaxy A6+ Asus Asus Zenfone 2 Laser ZE601KL 3 Galaxy A6+ Asus Asus ZenFone 2 ZE550ML 4 Galaxy A6+ Asus Asus Zenfone 2 ZE551ML 5 Galaxy A6+ Asus Asus Zenfone 3 Laser 6 Galaxy A6+ Asus Asus Zenfone 3 Max ZC520TL 7 Galaxy A6+ Asus Asus Zenfone 3 Max ZC553KL 8 Galaxy A6+ Asus Asus Zenfone 3 ZE520KL 9 Galaxy A6+ Asus Asus Zenfone 3 ZE552KL 10 Galaxy A6+ Asus Asus Zenfone 3s Max 11 Galaxy A6+ Asus Asus Zenfone Max 12 Galaxy A6+ Asus Asus Zenfone Selfie 13 Galaxy A6+ Asus Asus ZenFone Zoom ZX550 14 Galaxy A6+ Gionee Gionee A1 15 Galaxy A6+ Gionee Gionee A1 Lite 16 Galaxy A6+ Gionee Gionee A1 Plus 17 Galaxy A6+ Gionee Gionee Elife E8 18 Galaxy A6+ Gionee Gionee Elife S Plus 19 Galaxy A6+ Gionee Gionee Elife S7 20 Galaxy A6+ Gionee Gionee F103 21 Galaxy A6+ Gionee Gionee F103 Pro 22 Galaxy A6+ Gionee Gionee Marathon M4 23 Galaxy A6+ Gionee Gionee Marathon M5 24 Galaxy A6+ Gionee Gionee marathon M5 Lite 25 Galaxy A6+ Gionee Gionee Marathon M5 Plus 26 Galaxy A6+ Gionee Gionee P5L 27 Galaxy A6+ Gionee Gionee P7 Max 28 Galaxy A6+ Gionee Gionee S6 29 Galaxy A6+ Gionee Gionee S6 Pro 30 Galaxy A6+ Gionee Gionee S6s 31 Galaxy A6+ Gionee Gionee X1s 32 Galaxy A6+ Google Google Pixel 33 Galaxy A6+ Google Google Pixel XL LTE 34 Galaxy A6+ Google Nexus 5X 35 Galaxy A6+ Google Nexus 6 36 Galaxy A6+ Google Nexus 6P 37 Galaxy A6+ HTC Htc 10 38 Galaxy A6+ HTC Htc Desire 10 Pro 39 Galaxy A6+ HTC Htc Desire 628 40 Galaxy A6+ HTC HTC Desire 630 41 Galaxy A6+ -

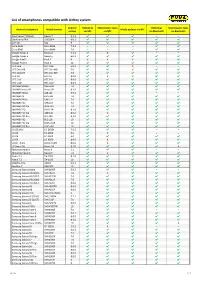

List of Smartphones Compatible with Airkey System

List of smartphones compatible with AirKey system Android Unlocking Maintenance tasks Unlocking Maintenance tasks Android smartphone Model number Media updates via NFC version via NFC via NFC via Bluetooth via Bluetooth Asus Nexus 7 (Tablet) Nexus 7 5.1.1 ✔ ✔ ✔ – – Blackberry PRIV STV100-4 6.0.1 ✔ ✔ ✔ ✔ ✔ CAT S61 S61 9 ✔ ✔ ✔ ✔ ✔ Doro 8035 Doro 8035 7.1.2 – – – ✔ ✔ Doro 8040 Doro 8040 7.0 – – – ✔ ✔ Google Nexus 4 Nexus 4 5.1.1 ✔ X ✔ – – Google Nexus 5 Nexus 5 6.0.1 ✔ ✔ ✔ ✔ ✔ Google Pixel 2 Pixel 2 9 X X X ✔ ✔ Google Pixel 4 Pixel 4 10 ✔ ✔ ✔ ✔ ✔ HTC One HTC One 5.0.2 ✔ ✔ X – – HTC One M8 HTC One M8 6.0 ✔ ✔ X ✔ ✔ HTC One M9 HTC One M9 7.0 ✔ ✔ ✔ ✔ ✔ HTC 10 HTC 10 8.0.0 ✔ X X ✔ ✔ HTC U11 HTC U11 8.0.0 ✔ ✔ ✔ ✔ ✔ HTC U12+ HTC U12+ 8.0.0 ✔ ✔ ✔ ✔ ✔ HUAWEI Mate 9 MHA-L09 7.0 ✔ ✔ ✔ ✔ ✔ HUAWEI Nexus 6P Nexus 6P 8.1.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P8 lite ALE-L21 5.0.1 ✔ ✔ ✔ – – HUAWEI P9 EVA-L09 7.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P9 lite VNS-L21 7.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P10 VTR-L09 7.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P10 lite WAS-LX1 7.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P20 EML-L29 8.1.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P20 lite ANE-LX1 8.0.0 ✔ X ✔ ✔ ✔ HUAWEI P20 Pro CLT-L29 8.1.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P30 ELE-L29 10 ✔ ✔ ✔ ✔ ✔ HUAWEI P30 lite MAR-LX1A 10 ✔ ✔ ✔ ✔ ✔ HUAWEI P30 Pro VOG-L29 10 ✔ ✔ ✔ ✔ ✔ LG G2 Mini LG-D620r 5.0.2 ✔ ✔ ✔ – – LG G3 LG-D855 5.0 ✔ X ✔ – – LG G4 LG-H815 6.0 ✔ ✔ ✔ ✔ ✔ LG G6 LG-H870 8.0.0 ✔ X ✔ ✔ ✔ LG G7 ThinQ LM-G710EM 8.0.0 ✔ X ✔ ✔ ✔ LG Nexus 5X Nexus 5X 8.1.0 ✔ ✔ ✔ ✔ X Motorola Moto X Moto X 5.1 ✔ ✔ ✔ – – Motorola Nexus 6 Nexus 6 7.0 ✔ X ✔ ✔ ✔ Nokia 7.1 TA-1095 8.1.0 ✔ ✔ X ✔ ✔ Nokia 7.2 TA-1196 10 ✔ ✔ ✔ -

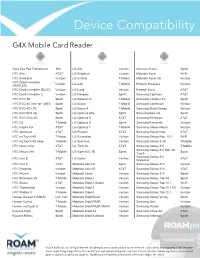

Device Compaibility List

Device Compatibility G4X Mobile Card Reader Asus Eee Pad Transformer N/A LG Ally Verizon Motorola Photon Sprint HTC Aria AT&T LG Enlighten Verizon Motorola Xoom Wi-Fi HTC Droid Eris Verizon LG G-Slate T-Mobile Motorola Xoom 4G Verizon HTC Droid Incredible Verizon LG G2X T-Mobile Pantech Breakout Verizon (AMOLED) HTC Droid Incredible (SLCD) Verizon LG Lucid Verizon Pantech Burst AT&T HTC Droid Incredible 2 Verizon LG Marquee Sprint Samsung Captivate AT&T HTC EVO 3D Sprint LG Mytouch Q T-Mobile Samsung Conquer 4G Sprint HTC EVO 4G (h/w ver. 0003) Sprint LG Nexus T-Mobile Samsung Continuum Verizon HTC EVO 4G LTE Sprint LG Nexus 4 T-Mobile Samsung Droid Charge Verizon HTC EVO Shift 4G Sprint LG Optimus Elite Sprint Samsung Epic 4G Sprint HTC EVO View 4G Sprint LG Optimus G AT&T Samsung Exhilarate AT&T HTC G2 T-Mobile LG Optimus S Sprint Samsung Fascinate Verizon HTC Inspire 4G AT&T LG Optimus T T-Mobile Samsung Galaxy Nexus Verizon HTC Jetstream AT&T LG Phoenix AT&T Samsung Galaxy Note AT&T HTC myTouch 4G T-Mobile LG Revolution Verizon Samsung Galaxy Note 10.1 Wi-Fi HTC myTouch 4G Slide T-Mobile LG Spectrum Verizon Samsung Galaxy S 4G T-Mobile HTC Nexus One AT&T LG Thrill 4G AT&T Samsung Galaxy S II T-Mobile Samsung Galaxy S II Epic 4G HTC Nexus One T-Mobile LG Viper 4G LTE Sprint Sprint Touch Samsung Galaxy S II HTC One S AT&T LG Vortex Verizon AT&T Skyrocket HTC One X AT&T Motorola Admiral Sprint Samsung Galaxy S III Verizon HTC Rezound Verizon Motorola Atrix 4G AT&T Samsung Galaxy S III AT&T HTC Rhyme Verizon Motorola Citrus Verizon Samsung Galaxy S III Sprint HTC Sensation 4G T-Mobile Motorola Droid 2 Verizon Samsung Galaxy Tab 3G Sprint HTC Status AT&T Motorola Droid 2 Global Verizon Samsung Galaxy Tab 10.1 Wi-Fi HTC Thunderbolt Verizon Motorola Droid 3 Verizon Samsung Galaxy Tab 10.1 4G Verizon HTC Wildfire S T-Mobile Motorola Droid 4 Verizon Samsung Galaxy Tab 10.1 Verizon Huawei Ascend II (M865) U.S. -

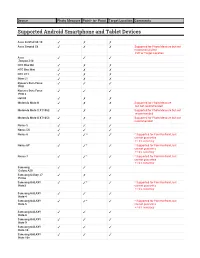

List of Supported Devices

Device Photo Measure Point- to- Point Target Location Comments Supported Android Smartphone and Tablet Devices Asus ZenPad 3S 10 ✓ ✗ ✗ Asus Zenpad Z8 ✓ ✗ ✗ Supported for Photo Measure but not recommended for P2P or Target Location Asus ✓ ✓ ✓ Zenpad Z10 HTC One M8 ✓ ✗ ✗ HTC One Mini ✓ ✗ ✗ HTC U11 ✓ ✗ ✗ iNew L1 ✓ ✗ ✗ Kyocera Dura Force ✓ ✓ ✓ PRO Kyocera Dura Force ✓ ✓ ✓ PRO 2 LGV20 ✓ ✗ ✗ Motorola Moto G ✓ ✗ ✗ Supported for Photo Measure but not recommended Motorola Moto X XT1052 ✓ ✗ ✗ Supported for Photo Measure but not recommended Motorola Moto X XT1053 ✓ ✗ ✗ Supported for Photo Measure but not recommended Nexus 5 ✓ ✓ ✓ Nexus 5X ✓ ✓ ✓ Nexus 6 ✓ ✓* ✓ * Supported for Point-to-Point, but cannot guarantee +/-3% accuracy Nexus 6P ✓ ✓* ✓ * Supported for Point-to-Point, but cannot guarantee +/-3% accuracy Nexus 7 ✓ ✓* ✓ * Supported for Point-to-Point, but cannot guarantee +/-3% accuracy Samsung ✓ ✓ ✓ Galaxy A20 Samsung Galaxy J7 ✓ ✗ ✓ Prime Samsung GALAXY ✓ ✓* ✓ * Supported for Point-to-Point, but Note3 cannot guarantee +/-3% accuracy Samsung GALAXY ✓ ✓ ✓ Note 4 Samsung GALAXY ✓ ✓* ✓ * Supported for Point-to-Point, but Note 5 cannot guarantee +/-3% accuracy Samsung GALAXY ✓ ✓ ✓ Note 8 Samsung GALAXY ✓ ✓ ✓ Note 9 Samsung GALAXY ✓ ✓ ✓ Note 10 Samsung GALAXY ✓ ✓ ✓ Note 10+ Device Photo Measure Point- to- Point Target Location Comments Samsung GALAXY ✓ ✓ ✓ Note 10+ 5G Samsung GALAXY ✓ ✓ ✓ Note 20 Samsung GALAXY ✓ ✓ ✓ Note 20 5G Samsung GALAXY ✓ ✗ ✗ Supported for Photo Measure but not Tab 4 (old) recommended Samsung GALAXY ✓ ✗ ✓ Supported for Photo -

Mobile Devices Mobile ……

…… Lecture 9 Mobile Devices . Mobile Business I (WS 2015/16) Prof. Dr. Kai Rannenberg [Source: Nokia] Deutsche Telekom Chair of Mobile Business & Multilateral Security . Johann Wolfgang Goethe University Frankfurt a. M. Overview …… Mobile Devices § Introduction § Categorisation of Mobile Devices § Components of Mobile Devices § Accumulators § Processors, Memory, and Storage § Display . § Means for I/O . 2 Mobile Terminal vs. …… Mobile Device § A Mobile Device is a small, handheld computing device. § Mobile Terminal emphasises the fact that the mobile device represents the end of a communications link or the edge node of a communications network. 3 Device Manufacturers and Brands …… (including some historic ones) § Alcatel § Philips § Apple § Sagem § Audiovox § Samsung § Benefon § Sendo § BenQ Mobile § Siemens § Blackberry § Sony § Bosch § TCL Communication § Ericsson § Google § Telepong § HTC § Telit § Huawei § Telme § LG Electronics § Toshiba § Microsoft § Trium . § Motorola § Windhorst § NEC § Xelibri § Nokia . § Yulong . § Panasonic § ZTE 4 Worldwide Mobile Phone Sales to End Users by Vendor …… Q1-2015 vs. Q1-2005 1Q15 Market In 1.000 Units 1Q05 Market Company 1Q15 units Share (%) 1Q05 units Samsung 97,986 21.3 24,479.8 13.5 Apple 60,177 13.1 - Microsoft (former Nokia) 33,002 7.2 54,960.1 30.4 LG Electronics (former LG) 19,637 4.3 11,464.2 6.3 Lenovo*/Motorola 19,280 4.2 30,143.3 16.7 Huawei 18,590 4.0 TCL Communication 14,189 3.1 Ü others ZTE 12,600 2.7 BenQ Mobile 10,209.5 5.7 Ü others Sony Mobile Com. 9,905.8 5.5 . Others 184,799.9 40.1 39,829.5 21.9 TOTAL 460,261.7 100.0 180,992.2 100.0 . -

Evaluating Bluetooth Low Energy for Iot

Evaluating Bluetooth Low Energy for IoT Jonathan Furst¨ ∗, Kaifei Cheny, Hyung-Sin Kimy and Philippe Bonnet∗ ∗IT University of Copenhagen, yUC Berkeley [email protected], fkaifei, [email protected], [email protected] Abstract—Bluetooth Low Energy (BLE) is the short-range, While others have experienced similar phenomena [7], we single-hop protocol of choice for the edge of the IoT. Despite could not find systematic studies of BLE characteristics on its growing significance for phone-to-peripheral communication, smartphones in the literature. Most existing work focus on the BLE’s smartphone system performance characteristics are not well understood. As others, we experienced mixed erratic perfor- BLE performance of BLE SoCs [8], [9], [10], [11], [12], with- mance results in our BLE based smartphone-centric applications. out quantifying BLE performance in a smartphone context. In these applications, developers can only access low-level func- However, smartphones-peripheral systems represent a large set tionalities through multiple layers of OS and hardware abstrac- of BLE applications in the wild [1], [2], [3]. In our work, tions. We propose an experimental framework for such systems, we thus focus on two questions: (1) Can we show systematic with which we perform experiments on a variety of modern smartphones. Our evaluation characterizes existing devices and variations in BLE application behavior across smartphone gives new insight about peripheral parameters settings. We show models? (2) Can we define a model to characterize BLE that BLE performances vary significantly in non-trivial ways, performance on smartphones, that could inform application depending on SoC and OS with a vast impact on applications. -

Device Compatibility APPLE™ COMPATIBILITY

Device Compatibility Android devices running the required software must also have a microUSB port and support powered USB OTG. iOS devices running the required software must be equipped with a lightning connector port. Visit the Help Center for more detailed explanations of Android requirements and iOS requirements. APPLE™ COMPATIBILITY Works with and tested against: iPhone XS Max iPhone XS iPhone XR iPhone X iPhone 8 Plus iPhone 8 iPhone 7+ iPhone 7 iPhone SE iPhone 5 iPhone 5c iPhone 5s iPhone 6 iPhone 6+ iPhone 6s iPhone 6s+ iPhone SE iPod Touch 5th Generation Works with, but not optimized for: iPad Mini (all versions) iPad Air iPad 4th Generation Not compatible with: iPhone 4s or lower iPad 3 or lower iPod Touch 4 or lower iPad Pro ANDROID™ COMPATIBILITY Works with and tested against: Motorola Moto X Motorola Moto G Samsung Galaxy S3 Samsung Galaxy S4 Samsung Galaxy S5 (except some running 5.1.1*) Samsung Galaxy S6 Samsung Galaxy S6 Edge Samsung Galaxy S7 Samsung Galaxy S7 Edge Samsung Galaxy Note 2 Samsung Galaxy Note 3 Samsung Galaxy Note 4 Samsung Galaxy Note 8 Samsung Galaxy Note Edge HTC One Mini 2 (requires adapter) HTC One A9 (requires adapter) HTC One M8 (requires adapter) HTC One M9 (requires adapter) HTC Desire EYE (requires adapter) HTC Desire 820 (requires adapter) Google Nexus 5 (requires adapter) Google Nexus 6 (requires reversible adapter or cable) Google Nexus 5x (requires USB-C adapter) Google Nexus 6p (requires USB-C adapter) Google Pixel (Requires USB-C adapter)