Zener Diode As Voltage Regulator

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Diode Limiters Or Clipper Circuits

Diode Limiters or Clipper Circuits Circuits which are used to clip off portions of signal voltages above or below certain levels are called limiters or clippers. Types of Clippers • Positive Clipper • Negative Clipper Positive Clipper • The circuit that limits or clips the positive part of the input voltage, is called a positive limiter or positive clipper. Working of Positive Clipper • As the input voltage goes positive, the diode becomes forward-biased and conducts current. • Since the cathode is at ground potential (0V), the anode cannot exceed 0.7V (for Si). • So point A is limited to +0.7V when the input voltage exceeds this value. • When the input voltage goes back below 0.7V, the diode is reverse-biased and appears as an open. • The output voltage looks like the negative part of the input voltage, but with magnitude determined by the voltage divider formed by R1 and load resistor RL; Negative Clipper • The circuit that limits or clips the negative part of the input voltage, is called a negative limiter or negative clipper. Working of Negative Clipper • If the diode is turned around, the negative part of the input voltage is clipped off. • When the diode is forward-biased during the negative part of the input voltage, point A is held at -0.7V by the diode drop. • When the input voltage goes above –0.7V, the diode is no longer forward- biased; and a voltage appears across RL proportional to input voltage. Practical Problem • What will be the output waveform across RL in the limiter circuit shown in figure Clamper Circuits Clamping is the process of introducing a dc level into an ac signal. -

Ee320l 05 Experiment 5.Pdf

EE320L Electronics I Laboratory Laboratory Exercise #5 Clipping and Clamping Circuits By Angsuman Roy Department of Electrical and Computer Engineering University of Nevada, Las Vegas Objective: The purpose of this lab is to understand the operation of clipping and clamping circuits and their applications. Equipment Used: Power Supply Oscilloscope Function Generator Breadboard Jumper Wires TL082 or LF412 Dual JFET Input Operational Amplifiers 10x Scope Probes Various Resistors and Capacitors Background: Clipping and Clamping Circuits Diodes, despite being two terminals devices have more uses than it may seem. While the application most commonly associated with diodes is rectification for power supplies and radio frequency detection, diodes are also used for clipping and clamping signals. Clipping is simply bounding a signal to limited amplitude. Clamping is shifting the center of an AC signal to a different value. Both of these operations can be implemented with a diode and a few passive components. Active versions of these circuits are implemented with op-amps. As is commonly the case, using op-amps allows the performance of a circuit to approach theoretical ideals. Clipping and clamping circuits find widespread use in audio and video circuitry. A brief digression into the types of diodes is important for designing clipping and clamping circuits. Diodes can be classified based on their material type, application and structure. Most diodes today are made out of silicon. These diodes have a forward voltage drop of around 0.6V. In the past, germanium diodes were more common and had a forward voltage drop of 0.3V. They can still be purchased if one looks hard enough. -

Lab #5: Clipping and Clamping Circuits

EE320L Electronics I Laboratory Laboratory Exercise #5 Clipping and Clamping Circuits By Angsuman Roy Department of Electrical and Computer Engineering University of Nevada, Las Vegas Objective: The purpose of this lab is to understand the operation of clipping and clamping circuits and their applications. Equipment Used: Power Supply Oscilloscope Function Generator Breadboard Jumper Wires TL082 or LF412 Dual JFET Input Operational Amplifiers 10x Scope Probes Various Resistors and Capacitors Background: Clipping and Clamping Circuits Diodes, despite being two terminals devices have more uses than it may seem. While the application most commonly associated with diodes is rectification for power supplies and radio frequency detection, diodes are also used for clipping and clamping signals. Clipping is simply bounding a signal to limited amplitude. Clamping is shifting the center of an AC signal to a different value. Both of these operations can be implemented with a diode and a few passive components. Active versions of these circuits are implemented with op-amps. As is commonly the case, using op-amps allows the performance of a circuit to approach theoretical ideals. Clipping and clamping circuits find widespread use in audio and video circuitry. A brief digression into the types of diodes is important for designing clipping and clamping circuits. Diodes can be classified based on their material type, application and structure. Most diodes today are made out of silicon. These diodes have a forward voltage drop of around 0.6V. In the past, germanium diodes were more common and had a forward voltage drop of 0.3V. They can still be purchased if one looks hard enough. -

Diode Circuits Rectifier Circuits

Chapter 2: Diode Circuits Rectifier Circuits 11/12/2015 JUEE – Electronics I –Dr. Hani Jamleh 1 Preview • In the last chapter, we discussed some of the properties of semiconductor materials and introduced the diode. 11/12/2015 JUEE – Electronics I –Dr. Hani Jamleh 2 Preview • We presented the ideal current–voltage relationship of the diode and considered the piecewise linear model, which simplifies the dc analysis of diode circuits. 11/12/2015 JUEE – Electronics I –Dr. Hani Jamleh 3 Preview • In this chapter, the techniques and concepts developed in Chapter 1 are used to analyze and design electronic circuits containing diodes. 11/12/2015 JUEE – Electronics I –Dr. Hani Jamleh 4 Goals • A general goal of this chapter is: • To develop the ability to use the piecewise linear model and approximation techniques in the hand analysis and design of various diode circuits. 11/12/2015 JUEE – Electronics I –Dr. Hani Jamleh 5 Preview • Each circuit to be considered accepts an input signal at a set of input terminals and produces an output signal at a set of output terminals. • This process is called signal processing: The circuit “processes” the input signal and produces an output signal that is a different shape or a different function compared to the input signal. • We will see in this chapter how diodes are used to perform these various signal processing functions. 11/12/2015 JUEE – Electronics I –Dr. Hani Jamleh 6 In chapter 2 of the book, we will: 1. Determine the operation and characteristics of diode rectifier circuits, which, in general, form the first stage of the process of converting an ac signal into a dc signal in the electronic power supply. -

Study and Analysis of Clipper and Clamper Circuits

© AUG 2019 | IRE Journals | Volume 3 Issue 2 | ISSN: 2456-8880 Study and Analysis of Clipper and Clamper Circuits MOH MOH KHAING1, YI LAY NGE2, KHIN THANDAR OO3 1, 2, 3 Department of Electronic Engineering, Technological University (Myitkyina) Abstract -- This paper presents the analysis of diode II. BASIC CIRCUITS AND WORKING clipper and clamper circuits that are commonly used in PRINCIPLE analog television receivers and FM transmitters. Different configurations of diode clipper circuits and clamper circuits are designed and analyzed through simulation In electronic circuits, the diode is the simplest and the results. Ordinary diodes, Zener diodes, resistors and most fundamental non-linear circuit element. A capacitors are used as circuit elements and circuit clipper circuit is one of the simple diode circuits and analyses are performed with the help of Multisim software. it has the ability to “clip off” a portion of the input signal without distorting the remaining part of the ac Indexed Terms: diode clipper circuits, clamper circuits, Simulation, Multisim Software waveform. Figure 1 illustrates the basic clipper circuit that can clipped off the positive or negative part of the input signal depending on the direction of I. INTRODUCTION the diode. The half-wave rectifier is an example of the simplest form of diode clipper. A clipping circuit designed with diodes is an electronic circuit that is used to „clip‟ the input D1 voltage to prevent it from attaining a value larger than a predefined one. The basic components V1 RL required for a clipping circuit are a diode and a resistor. Clipper circuits can be classified depend upon their biasing, configurations, level of clipping. -

Diode Applications Diode Clipper and Clamper Circuits These Are Diode Wave-Shaping Circuits I.E

It is the same of for ordinary full wave rectifier (f) Advantages: 1. No centre-tap is required on the transformer. 2. Much smaller transformers are required. 3. It is suitable for high-voltage applications. 4. It has less PIV rating per diode. The obvious disadvantage is the need for twice as many diodes as for the centre- tapped transformer version. Diode Applications Diode Clipper and Clamper Circuits These are diode wave-shaping circuits i.e. circuits meant to control the shape of the voltage and current waveforms to suit various purposes. Each performs the wave- shaping function indicated by its name. The output of the clipping circuit appears as if a portion of the input signal were clipped off. But clamper circuits simply lams (i.e. lift up or down) the input signal to a different dc level. Clippers A clipping circuit requires a minimum of two components i.e. a diode and a resistor. Often, dc battery is also used to fix the clipping level. The input waveform can be clipped at different levels by simply changing the battery voltage and by 20 interchanging the position of various elements. We will use an ideal diode which acts like a closed switch when forward-biased and as an open switch when reverse- biased. Such circuits are used in radars and digital computers etc. when it is desired to remove signal voltages above or below a specified voltage level. Another application is in radio receivers for communication circuits where noise pulses that rise well above the signal amplitude are clipped down to the desired level. -

Analog Electronics and Opamp

CONTENT GENERATION [UNDER EDUSAT PROGRAMME] AANNAALLOOGG EELLEECCTTRROONNIICCSS AANNDD OOPPAAMMPP [[EETTTT 332211]] 3RD SEM ELECTRICAL ENGG. Under SCTE&VT, Odisha PPRREEPPAARREEDD BBYY:: -- 1. Er. DEBI PRASAD PATNAIK [Sr. Lecture, Dept of ETC, UCP ENGG. SCHOOL, Berhampur] 2. Er. PARAMANANDA GOUDA [Lecturer (PT), Dept of ETC, UCP ENGG. SCHOOL, Berhampur [ PAGE – 1. 1 ] CHAPTER - 1 -------------------------------------- [P-N JUNCTION DIODE ] -------------------------------- DEFINITION:- When a p-type semiconductor is suitably joined to n-type semiconductor, the contact surface is called p-n Junction. FORMATION OF PN JUNCTION In actual practice, the characteristic properties of PN junction will not be apparent if a p- type block is just brought in contact with n-type block. It is fabricated by special techniques and one common method of making PN junction is called Alloying. In this method, a small block of indium (trivalent impurity) is placed on an n-type germanium slab as shown in Fig (i). The system is then heated to a temperature of about 500ºC. The indium and some of the germanium melt to form a small puddle of molten germanium-indium mixture as shown in Fig (ii). The temperature is then lowered and puddle begins to solidify. Under proper conditions, the atoms of indium impurity will be suitably adjusted in the germanium slab to form a single crystal. The addition of indium overcomes the excess of electrons in the n-type germanium to such an extent that it creates a p-type region. As the process goes on, the remaining molten mixture becomes increasingly rich in indium. When all germanium has been re-deposited, the remaining material appears as indium but- ton which is frozen on to the outer surface of the crystallized portion as shown in Fig (iii). -

Clippers and Clampers

Section B8: Clippers And Clampers We’ve been talking about one application of the humble diode – rectification. These simple devices are also powerful tools in other applications. Specifically, this section of our studies looks at signal modification in terms of clipping and clamping. Clippers Clipping circuits (also known as limiters, amplitude selectors, or slicers), are used to remove the part of a signal that is above or below some defined reference level. We’ve already seen an example of a clipper in the half-wave rectifier – that circuit basically cut off everything at the reference level of zero and let only the positive-going (or negative-going) portion of the input waveform through. To clip to a reference level other than zero, a dc source (shown as a battery in your text) is put in series with the diode. Depending on the direction of the diode and the polarity of the battery, the circuit will either clip the input waveform above or below the reference level (the battery voltage for an ideal diode; i.e., for Von=0). This process is illustrated in the four parts of Figure 3.43: ¾ Without the battery, the output of the circuit below would be the negative portion of the input wave (assuming the bottom node is grounded). When vi > 0, the diode is on (short-circuited), vi is dropped across R and vo=0. When vi <0, the diode is off (open-circuited), the voltage across R is zero and vo=vi. (Don’t worry; we won’t be doing this for all the circuits!) Anyway, the reference level would be zero. -

Pulse and Integrated Circuits Lab

Pulse and Integrated Circuits Lab EC-352 Prepared by M Baby Lecturer, ECE. DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING BAPATLA ENGINEERING COLLEGE: : BAPATLA (AUTONOMOUS) BAPATLA-522 101 Index 1. Linear Wave Shaping 2(a). Non Linear Wave Shaping-Clippers 2(b). Non Linear Wave Shaping-Clampers 3. Astable Multivibrator using Transistors 4. Monostable Multivibrator using Transistors 5(a). Schmitt Trigger using Transistors 5(b). Schmitt Trigger Circuits- using IC 741 6. Measurement of op-Amp parameters 7. Applications of Op-Amp 8. Instrumentation Amplifier using op-Amp 9. Waveform generation using op-amp (square & triangular) 10. Design Of Active Filters – Lpf, Hpf (First Order) 11. Applications of ic 555 timer ( Monostable &Astable multivibrators) 12. PLL Using 1C 565 13. IC723 Voltage Regulator 14. Design of VCO using IC 566 15. 4 bit DAC using OP AMP 2 1. Linear Wave Shaping Aim: i) To design a low pass RC circuit for the given cutoff frequency and obtain its frequency response. ii) To observe the response of the designed low pass RC circuit for the given square waveform for T<<RC,T=RC and T>>RC. iii) To design a high pass RC circuit for the given cutoff frequency and obtain its frequency response . iv) To observe the response of the designed high pass RC circuit for the given square waveform for T<<RC, T=RC and T>>RC. Apparatus Required: Name of the Specifications Quantity Component/Equipment 1K Ω 1 Resistors 2.2K Ω,16 K Ω 1 Capacitors 0.01 µF 1 CRO 20MHz 1 Function generator 1MHz 1 Theory: The process whereby the form of a non sinusoidal signal is altered by transmission through a linear network is called “linear wave shaping”. -

Pulse and Digital Circuits Lecture Notes B.Tech (Ii Year – Ii Sem)

PULSE AND DIGITAL CIRCUITS LECTURE NOTES B.TECH (II YEAR – II SEM) (2017-18) Prepared by: Mr. R. Chinnarao Assistant Professor Mrs. D.Asha Assistant Professor Department of Electronics and Communication Engineering MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India) Recognized under 2(f) and 12 (B) of UGC ACT 1956 (Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – ‘A’ Grade - ISO 9001:2015 Certified) Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India UNIT – I LINEAR WAVESHAPING ……………………………………………………………………………. High pass, low pass RC circuits, their response for sinusoidal, step, pulse, square and ramp inputs. RC network as differentiator and integrator, attenuators, its applications in CRO probe, RL and RLC circuits and their response for step input, Ringing circuit. ……………………………………………………………………………………………………… A linear network is a network made up of linear elements only. A linear network can be described by linear differential equations. The principle of superposition and the principle of homogeneity hold good for linear networks. In pulse circuitry, there are a number of waveforms, which appear very frequently. The most important of these are sinusoidal, step, pulse, square wave, ramp, and exponential waveforms. The response of RC, RL, and RLC circuits to these signals is described in this chapter. Out of these signals, the sinusoidal signal has a unique characteristic that it preserves its shape when it is transmitted through a linear network, i.e. under steady state, the output will be a precise reproduction of the input sinusoidal signal. There will only be a change in the amplitude of the signal and there may be a phase shift between the input and the output waveforms. -

![United States Patent (11) 3,562,549 [72] Inventor Juergen Teichmann Dresden, Germany [56] References Cited 2 L ) Appl](https://docslib.b-cdn.net/cover/5835/united-states-patent-11-3-562-549-72-inventor-juergen-teichmann-dresden-germany-56-references-cited-2-l-appl-7745835.webp)

United States Patent (11) 3,562,549 [72] Inventor Juergen Teichmann Dresden, Germany [56] References Cited 2 L ) Appl

United States Patent (11) 3,562,549 [72] Inventor Juergen Teichmann Dresden, Germany [56] References Cited 2 l ) Appl. No. 730,869 UNITED STATES PATENTS [22] Filed May 21, 1968 3,445,680 5/1969 Foster et al. .................. 307/215 [45] Patented Feb. 9, 1971 3,458,719 7/1969 Weiss ........................... 307/2 15X [73] Assignee Arbeitsstelle Fur Molekularelektronik Primary Examiner-John S. Heyman Dresden, Germany Assistant Examiner-John Zazworsky Attorney-Nolte and Nolte [54] SEMICONDUCTOR LOGIC CIRCUIT 7 Claims, 4 Drawing Figs. ABSTRACT: A plurality of diode inputs is connected through [52] U.S. Cl.......................... • • • • • • • • • • • • • • • • • • • • - a * * a * * · * 307/215, a Zener diode clipper and amplifier circuit with a subsequent 307/237; 328/93 output stage so that the Zener voltage determines the initial [51 ] Int. Cl............................ • • • • • • • • • • • • • • • • • • • • • ******** H03k 19/36, shifting voltage level. To change this initial level, a conven H03k 5/08 tional negator controls a transistor connected in parallel with [50] Field of Search............................ 307/25, said clipper and amplifier circuits, and turns off the latter in 237, 253, 289, 300; 328/93 dependence on the output condition. PATENTED FEB 9 1971 3,562,549 M . E out (V) S o INVENTOR JURGEN TECHMANN 3,562,549 1 2 SEMICONDUCTOR LOGIC CIRCUIT FIG. 2 is a hysteresis curve of the circuit of FG. 1. DESCRIPTION OF THE PREFERRED EMBODIMENTS BACKGROUND OF THE INVENTION In FIG. 1, there is shown a logic NAND circuit comprisinga l Field of the Invention 5 plurality of input diodes 4, 5 and 6, the cathodes of which are This invention relates to a semiconductor or solid state in tegrated circuit for performing various logical functions, connected to input terminals 1, 2 and 3 whereas the anodes preferably an “and-not,” (i.e.,NAND) function. -

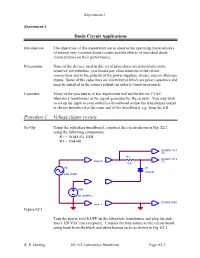

Diode Circuit Applications Procedure 1 Voltage Clipper Circuits

Experiment-2 Experiment-2 Diode Circuit Applications Introduction The objectives of this experiment are to observe the operating characteristics of several very common diode circuits and the effects of non-ideal diode characteristics on their performance. Precautions None of the devices used in this set of procedures are particularly static sensitive; nevertheless, you should pay close attention to the circuit connections and to the polarity of the power supplies, diodes, and oscilloscope inputs. Some of the capacitors are electrolytics which are polar capacitors and must be installed in the correct polarity in order to function properly. Comment Many of the procedures in this experiment will utilize the ±6.3 VAC laboratory transformer as the signal generator for the circuits. You may wish to set up the input to your solderless breadboard so that the transformer output is always introduced at the same end of the breadboard, e.g. from the left. Procedure 1 Voltage clipper circuits Set-Up Using the solderless breadboard, construct the circuit shown in Fig. E2.1 using the following components: R1 = 10 kΩ 5% 1/4W D1 = 1N4148 SCOPE CH-1 (X) R1 SCOPE CH-2 BLACK (Y) 10 k VS D1 1N4148 LAB XFMR VBB DC SUPPLY SCOPE GND WHITE Figure E2.1 Turn the power switch OFF on the laboratory transformer and plug the unit into a 120 VAC line receptacle. Connect the transformer to the circuit board using leads from the black and white banana jacks as shown in Fig. E2.1. R. B. Darling EE-331 Laboratory Handbook Page E2.1 Experiment-2 This will apply a 10 V peak sinewave to the circuit once the power is turned on.