The ITRS Design Technology and System Drivers Roadmap: Process and Status

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Cash Flow Comparison

國立政治大學商學院國際經營管理 英語碩士學位學程 International MBA Program College of Commerce National Chengchi University 碩士論文 治 Master政 ’s Thesis大 立 學 國 三大電腦晶片製造商之財務比較‧ ‧ A ComparisonN of Major Computer Chipset Vendors a y t t i Inio Financial Point of View s n r a e i v l C n heng chi U Student: Roger Chang Advisor: Professor James Liu 中華民國一百年六月 June 2011 三大電腦晶片製造商之財務比較 A Comparison of Major Computer Chipset Vendors In Financial Point of View 研究生: 張鼎昱 Student: Roger Chang 指導教授: 劉助 Advisor: Prof. James Liu 治 政 大 立 國立政治大學 商學院國際經營管理英語碩士學 學位學程 國 碩士論文 ‧ ‧ N a y t t A Thesis i i s o r Sunbmitted to International MBAe Program a i v l NationalC Chengchi nUniversity he i U in partial fulfillmentngch of the Requirements for the degree of Master in Business Administration 中華民國一百年六月 June 2011 i Abstract A Comparison of Major Computer Chipset Vendors In Financial Point of View By Roger Chang The goal of this master thesis is to analyze the治 three major chipset players in today’s Personal 政 大 Computer (PC) industry, while立 providing recommendations in different perspectives. One of the perspectives is from the investor’s point of view to single out a 學company with the most long term 國 investment value. The other is from each company’s management point of view to suggest for the ‧ areas of improvement for the companies. Two of the three companies discussed in this thesis are ‧ American-based global companiesN namely, Intel and AMD, while the other is a Taiwanese company: a y t t i VIA Technology. -

Open Source Software License Information

Open Source Software license information This document contains an open source software license information for the product VACUU·SELECT. The product VACUU·SELECT contains open source components which are licensed under the applicable open source licenses. The applicable open source licenses are listed below. The open source software licenses are granted by the respective right holders directly. The open source licenses prevail all other license information with regard to the respective open source software components contained in the product. Modifications of our programs which are linked to LGPL libraries are permitted for the customer's own use and reverse engineering for debugging such modifications. However, forwarding the information acquired during reverse engineering or debugging to third parties is prohibited. Furthermore, it is prohibited to distribute modified versions of our programs. In any case, the warranty for the product VACUU·SELECT will expire, as long as the customer cannot prove that the defect would also occur without these modification. WARRANTY DISCLAIMER THE OPEN SOURCE SOFTWARE IN THIS PRODUCT IS DISTRIBUTED IN THE HOPE THAT IT WILL BE USEFUL, BUT WITHOUT ANY WARRANTY, WITHOUT EVEN THE IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. See the applicable licenses for more details. Written offer This product VACUU·SELECT contains software components that are licensed by the holder of the rights as free software, or Open Source software, under GNU General Public License, Versions 2 and 3, or GNU Lesser General Public License, Versions 2.1, or GNU Library General Public License, Version 2, respectively. The source code for these software components can be obtained from us on a data carrier (e.g. -

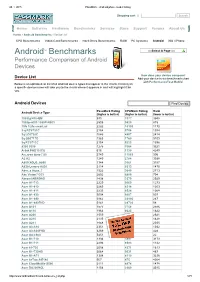

Androidtm Benchmarks

28. 1. 2015 PassMark Android phone model listing Shopping cart | Search Home Software Hardware Benchmarks Services Store Support Forums About Us Home » Android Benchmarks » Device List CPU Benchmarks Video Card Benchmarks Hard Drive Benchmarks RAM PC Systems Android iOS / iPhone TM Select A Page Android Benchmarks Performance Comparison of Android Devices How does your device compare? Device List Add your device to our benchmark chart with PerformanceTest Mobile! Below is an alphabetical list of all Android device types that appear in the charts. Clicking on a specific device name will take you to the charts where it appears in and will highlight it for you. Android Devices Find Device PassMark Rating CPUMark Rating Rank Android Device Type (higher is better) (higher is better) (lower is better) 1005tg N10QM 935 3377 3948 1080pn003 1080PN003 2505 9820 815 1life 1Life.smart.air 2282 10103 1170 3q RC9731C 2154 5756 1394 3q LC0720C 1646 4897 2414 3q QS0717D 1363 1760 3109 3q RC9712C 2154 5223 1396 9300 9300 1275 3364 3321 Alink PAD10 ICS 616 1130 4249 A.c.ryan dyno 7.85 2749 11065 596 A2 A2 1240 2784 3388 A800 XOLO_A800 1344 3661 3157 A830 Lenovo A830 2114 8313 1470 Abs_a Aqua_7 1522 3640 2713 Abc Vision7DCI 2602 6880 704 Abroad ABROAD 1438 3379 2929 Acer A1713 2229 9069 1273 Acer A1810 2265 8314 1203 Acer A1811 2233 8524 1268 Acer A1830 3004 9207 507 Acer A1840 3962 23996 267 Acer A1840FHD 5141 28720 58 Acer A101 1577 3758 2586 Acer A110 1964 8623 1822 Acer A200 1559 3822 2621 Acer A210 2135 8315 1428 Acer A211 1848 8130 2035 Acer A3A10 2351 8128 1032 Acer A3A20FHD 3269 11265 428 Acer AA3600 5451 22392 22 Acer B1710 1336 3897 3173 Acer B1711 2293 8583 1142 Acer b1720 2058 4371 1613 Acer B1730HD 3064 9031 487 Acer B1A71 1308 4119 3236 Acer beTouch E140 567 475 4264 Acer CloudMobile S500 2111 4874 1478 Acer DA220HQL 1156 2960 3545 http://www.androidbenchmark.net/device_list.php 1/71 28. -

Manufacturer Device Model Consumers Count Apple Iphone

Manufacturer Device Model Consumers Count Apple iPhone 24,666,239 Apple iPad 13,155,907 samsung SM-J500M 1,079,744 Apple iPod touch 1,070,538 samsung SM-G531H 1,043,553 samsung SM-G935F 1,026,327 samsung SM-T113 894,096 samsung SM-J700M 888,680 motorola MotoG3 860,116 samsung SM-J700F 847,315 samsung SM-G920F 834,655 samsung SM-G900F 827,050 samsung SM-G610F 786,659 HUAWEI ALE-L21 783,180 OPPO A37f 701,488 samsung SM-G955U 699,321 samsung SM-G930F 685,195 samsung SM-J510FN 673,415 samsung SM-G950U 654,635 samsung SM-G530H 651,695 samsung SM-J710F 647,723 motorola Moto G (4) 640,091 samsung SM-T110 627,013 samsung SM-J200G 611,728 OPPO A1601 588,226 samsung SM-G925F 571,858 samsung SM-G930V 557,813 samsung SM-A510F 533,209 ZTE Z981 532,290 samsung GT-I9300 516,580 samsung SM-J320FN 511,109 Xiaomi Redmi Note 4 507,119 samsung GT-I9505 504,325 samsung GT-I9060I 488,253 samsung SM-J120H 472,748 samsung SM-G900V 458,996 Xiaomi Redmi Note 3 435,822 samsung SM-A310F 435,163 samsung SM-T560 435,042 motorola XT1069 433,667 motorola Moto G Play 422,147 LGE LG-K430 406,009 samsung GT-I9500 392,674 Xiaomi Redmi 3S 388,092 samsung SM-J700H 384,922 samsung SM-G532G 384,884 samsung SM-N9005 382,982 samsung SM-G531F 382,728 motorola XT1033 380,899 Generic Android 7.0 374,405 motorola XT1068 373,075 samsung SM-J500FN 372,029 samsung SM-J320M 366,049 samsung SM-J105B 351,985 samsung SM-T230 348,374 samsung SM-T280 347,350 samsung SM-T113NU 341,313 samsung SM-T350 338,525 samsung SM-G935V 337,090 samsung SM-J500F 332,972 samsung SM-J320F 329,165 motorola -

Creación De Un Cluster Formado Por Tres Raspberry PI-3 Que Alojarán

Máster en Ingeniería Computacional y Matemática Trabajo Final de Máster Creación de un cluster formado por tres Raspberry PI-3 que alojarán una base de datos NoSQL (Apache Cassandra) y motor de cálculo distribuido (Apache Spark), desplegado en contenedores (Docker). Eduardo Romero López Sistemas Distribuidos Coordinador: Félix Freitag Nombre Profesor/a responsable de la asignatura: Joan Manuel Marquès 10 de septiembre de 2017 GNU Free Documentation License (GNU FDL) Copyright © 2017 Eduardo Romero López. Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.3 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front- Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License". DEDICADO A Lorena por su apoyo, paciencia y comprensión durante todo el periodo que duró el máster. AGRADECIMIENTO A todas las comunidades de desarrolladores y personas que comparten sus conocimientos en charlas y talleres sin miedo a que un tercero pueda aprenderlo, en especial a: @linux_malaga, @centrologic_es, @malaga_pythony @DataBeersMLG Ficha del Trabajo Fin de Máster Creación de un cluster formado por tres RaspberryPI-3 que alojarán una base de datos Título del trabajo NoSQL(Apache Cassandra) y motor de cálculo dis- tribuido(Apache Spark), alojado en un contenedor (Docker). Nombre del autor Eduardo Romero López Nombre del consultor/a Félix Freitag Nombre del PRA Joan Manuel Marquès Fecha de entrega 09/2017 Titulación Máster en Ingeniería Computacional y Matemática Área del Trabajo Final Sistemas Distribuidos Idioma del trabajo Español Palabras clave (máxi- Docker, Spark y Cassandra mo 3 palabras) Resumen del Trabajo (máximo 250 palabras): Este proyecto consiste en el ensamblaje e integración de todos los componentes hardware y software para formar un motor de cálculo distribuido sobre mini-PC (Raspberry PI-3), todo ello llevado a cabo desde un enfoque muy práctico. -

Sector Primer

U.S. Semiconductors Primer AMERICAS SEMICONDUCTORS EQUITY RESEARCH December 11, 2013 Chip-by-Chip: Semiconductor ABCs Sector view Remains Neutral Sector Primer In this detailed industry report, we provide a framework for longer- Research analysts term analysis by examining the market size, competitive landscape, and growth drivers for the semiconductor industry. Separately, we Americas Semiconductors have published an outlook piece, titled “Comfortably Numb,” with Romit Shah - NSI themes, catalysts, and best ideas for 2014. [email protected] +1 212 298 4326 Sidney Ho, CFA, CPA - NSI This report offers historical analysis, a discussion of key themes, and an [email protected] outlook for each of the major sub-segments including Microprocessors, +1 212 298 4329 Wireless, Logic, Memory, Analog, and Graphics. We also detail the Sanjay Chaurasia - NSI [email protected] semiconductor manufacturing processes, Moore’s Law, and new +1 212 298 4305 production technologies such as FinFET, double and quadruple patterning, and 450mm. We discuss in the Microprocessor section: new product roadmaps, Intel’s leadership position in servers, and ARM’s 64-bit architecture. We provide a PC model forecast with analysis of the weakening correlation between unit growth and GDP. We also examine integrated CPU graphics, PC gaming, and applications that will support GPU in cloud (GRID). In addition, we look at the evolution of cellular standards, economics of baseband processors, and Qualcomm’s leadership position in LTE. Emerging market smartphone adoption along the S-curve, increasing complexity of RF, and the number 2 player in LTE are key themes we discuss in the Wireless section. -

Postgresql License

SOURCE SOFTWARE NOTICE Software: postgresql 9.6 Copyright notice: Legal Notice PostgreSQL is Copyright © 1996-2020 by the PostgreSQL Global Development Group. Postgres95 is Copyright © 1994-5 by the Regents of the University of California. Permission to use, copy, modify, and distribute this software and its documentation for any purpose, without fee, and without a written agreement is hereby granted, provided that the above copyright notice and this paragraph and the following two paragraphs appear in all copies. IN NO EVENT SHALL THE UNIVERSITY OF CALIFORNIA BE LIABLE TO ANY PARTY FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING LOST PROFITS, ARISING OUT OF THE USE OF THIS SOFTWARE AND ITS DOCUMENTATION, EVEN IF THE UNIVERSITY OF CALIFORNIA HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. THE UNIVERSITY OF CALIFORNIA SPECIFICALLY DISCLAIMS ANY WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. THE SOFTWARE PROVIDED HEREUNDER IS ON AN "AS-IS" BASIS, AND THE UNIVERSITY OF CALIFORNIA HAS NO OBLIGATIONS TO PROVIDE MAINTENANCE, SUPPORT, UPDATES, ENHANCEMENTS, OR MODIFICATIONS. License: PostgreSQL License PostgreSQL is released under the PostgreSQL License, a liberal Open Source license, similar to the BSD or MIT licenses. PostgreSQL Database Management System (formerly known as Postgres, then as Postgres95) Portions Copyright © 1996-2020, The PostgreSQL Global Development Group Portions Copyright © 1994, The Regents of the University of California Permission to use, copy, modify, and distribute this software and its documentation for any purpose, without fee, and without a written agreement is hereby granted, provided that the above copyright notice and this paragraph and the following two paragraphs appear in all copies. -

BSH Hausgeräte Gmbh 1 / 266 LICENSE: Gplv2.0

Information regarding Free and Open Source Software This product includes software components that are licensed by the copyright holders as free software or open source software. The applicable license texts are printed below. Warranty Disclaimer The open source software in this product is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY, without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the applicable licenses for more details. The source code will be made available to you on request. To file a request, please email to [email protected] or send a written request to BSH Hausgeräte GmbH Carl-Wery-Str.34 D-81739 München Reference „OSSREQUEST“ The cost of performing your request will be charged to you. This offer is valid three years from the date of purchase or at least as long as we offer support and spare parts for the product. Information regarding Free and Open Source Software The license texts are displayed below the copyright statement at the end of this document. PACKAGE NAME: acl LICENSE: LGPLv2.1 Copyright statements: Copyright (c) 2000-2006 Silicon Graphics, Inc. All Rights Reserved. Copyright (C) 2007 Free Software Foundation, Inc. Antonio Trueba [email protected], 2007. Copyright (C) 2006 Free Software Foundation, Inc. Daniel Nylander [email protected], 2006. Copyright (C) 2005 Free Software Foundation, Inc. Sylvain Archenault [email protected], 2005. Copyright (C) 2004 Free Software Foundation, Inc. Jakub Bogusz [email protected], 2004. Copyright (C) 1996, 1997, 1998, 1999, 2000, 2001, 2003, 2004, 2005, 2006, 2007, 2008, 2009, 2010, 2011 Free Software Foundation, Inc. -

Open ARM GPU Drivers Slides

Open ARM GPU drivers: Where are we today, 1 year after the unveiling of the lima driver. Luc Verhaegen [email protected] The problem. The solution? Legal? (IANAL) GPU #1: ARM Mali ARM Mali-200/400 ● OpenGLES 2.0 ● Separate Vertex (GP) and Fragment (PP) shaders ● SoCs: ● Samsung exynos 4: world beater in 2011-2012 ● Allwinner, Amlogic, Rockchip, Telechips, Wondermedia, ... ● Future: Mali-450 ARM Mali T6xx ● OpenGLES 3.0/OpenCL 1.1 ● Unified shaders ● SoCs: ● Samsung exynos 5 ● Future: ARM T624/T628/T658/T678 Project: Lima Luc Connor Ben Verhaegen Abbott Brewer (libv) (cwabbott) (flatmush) Lima ● Status: research (highly advanced) ● No big secrets left in command-stream ● Compiler is tough due to Mali architecture ● Actual driver work will start after FOSDEM ● Full GNU/linux systems available ● Website: http://limadriver.org ● Repository: http://gitorious.org/lima ● Demos at the end of this talk / Lima compiler talk in X.org DevRoom (K.3.401) at 17:30. GPU #2: Qualcomm Adreno Qualcomm Adreno 2xx/3xx ● Former ATI Imageon ● OpenGLES 2.0, 3.0 (3xx) ● Unified shaders ● SoCs: ● Qualcomm Snapdragon S1-S4 ● Freescale iMX5 Project: Freedreno Rob Clark (robclark) Freedreno ● Status: WIP driver ● Job submission is like ATI radeon. ● Command-stream is mostly known. ● Shader architecture also mostly known. ● WIP xf86 (exa), mesa (gallium) drivers available ● No proper GNU/linux available :( ● Website: http://freedreno.github.com/ ● Further details and demos in the X.org DevRoom (K.3.401) at 17:00 today. GPU #3: Nvidia Geforce ULP (Tegra) Nvidia Geforce ULP/Tegra ● Supposedly a cut down older Geforce but... ● OpenGLES 2.0, 3.0 (tegra4), openCL/renderscript (tegra4) ● Split vertex and fragment shader design. -

【Reguler Member】 MEMBER COMPANIES・PRODUCT LINE

2019/10/09 MEMBER COMPANIES・PRODUCT LINE 【Reguler Member】 Company Name ALOMAN CO.,LTD Address of Head Office 3508, Noborito, Tama-ku, Kawasaki-shi, Kanagawa 214-0014 Japan TEL +81-44-934-0034 FAX +81-44-934-0017 URL http://www.aloman.co.jp ADVANCED MICRO DEVICES (AMD), ALPS ELECTRIC, ALTERA, ANALOG DEVICES, CEC-COILS, CONEXANT SYSTEMS, CYPRESS SEMICONDUCTOR, DELTA, FUJI ELECTRONICS, FUJITSU, HAMBRUG INDUSTRIES, HITACH, HYNIX SEMICONDUCTOR, IDT, INFINEON TECHNOLOGIES, INTEGRATED DEVICE TECHNOLOGY (IDT), INTEL , INTERSIL, LATTICE SEMICONDUCTOR, LG DISPLAY, LINEAR TECHNOLOGY, MAXIM INTEGRATED, MICRON TECHNOLOGY, MITSUBISHI ELECTRIC, MOLEX, MURATA, NATIONAL Product Line SEMICONDUCTOR (NS), NATIONAL SEMICONDUCTOR (NS), NANON GAOXIN ELECTRONICS, NEC, NEC TOKIN, NEW JAPAN RADIO, NIPPON CHEMI-CON, NXP SEMICONDUCTORS, OKI ELECTRIC INDUSTRY, ON SEMICONDUCTOR, PANASONIC, PHILIPS SEMICONDUCTOR, PMC-SIERRA, RENESAS ELECTRONICS, RICOH, ROHM, SAMSUNG ELECTRONICS, SANKEN, SEIKO EPSON, SEIKO INSTRUMENTS, SHARP, SHINDENGEN, SONY, SPANSION, STANLEY, STMICROELECTRONICS (ST), TDK, TDK-LAMBDA, TEXAS INSTRUMENTS (TI), TOSHIBA SEMICONDUCTOR & STORAGE PRODUCTS, VISHAY, WINSTER DISPLAY, XILINX, ZETEX Company Name ANALOG TECH K.K. Address of Head Office BC Plaza, 2-3-10 Kudan-minami, Chiyoda-ku, Tokyo 102-0074 TEL +81-3-3265-2801 FAX +81-3-3265-2804 URL http://www.analogtech.co.jp/ AAEON TECHNOLOGY,ADATA TECHNOLOGY, ADVANTECH, ANALOG DEVICES, APACER TECHNOLOGY, ASUSTEK COMPUTER, C&T SOLUTION, CHELSIO COMMUNICATIONS, CHENBRO MICOM, CERVOZ , CONGATEC, GIGA BYTE TECHNOLOGY, -

UNO Template

05 December 2012 Asia Pacific/China Equity Research Technology Hardware & Equipment Asia Semiconductor Sector Research Analysts SUPPLY CHAIN RESEARCH Randy Abrams, CFA 886 2 2715 6366 [email protected] Greater China IC Design powering the Yan Taw Boon 852 2101 7039 whitebox tablet ecosystem [email protected] Figure 1: Whitebox tablet builds at 50 mn in 2012 and 80-120 mn in 2013 CPU silicon IP 3D GPU silicon IP Foundries 300 250 Apps Processors 200 Touch screen controllers 150 100 Wireless and audio 50 - CY2012E CY2013E CMOS Apps processor image + baseband Branded tablets (mn units) White-box tablets (mn units) sensor Source: Company data, Credit Suisse estimates ■ Improving whitebox tablets expanding tablet TAM. The global tablet market is accelerating as whitebox tablets rapidly improve in functionality in the US$60-200 price range, below tier-one tablets. Initial demand is being led by Chinese makers exporting to emerging markets with low PC penetration, mainly for entertainment (games, movies, music) but have begun to offer productivity as keyboard attachments and apps proliferate. Whitebox tablets add 50 mn and 80-120 mn units to our 2012/13E global tablet estimate of 112 mn and 171 mn (45%/47% upside), respectively. Given cost sensitivity, pricing of Flash, DRAM, and touch display is the key swing factor to whitebox volumes. ■ Greater Chinese IC Design leading momentum. Greater China fabless leads in the space due to close ties to Shenzhen production/design base. ARM has lowered the entry barrier with dual / quad core Cortex processors, with leading domestic Chinese fabless Allwinner, Rockchip, Actions shipping dual-core now and quad-core in 1H13. -

CPU GPU RAM USB Ethernet Name Soc Nand Flash Video Outputs Audio Storage Wireless Other Ports Power Power Source Size Weight OS

Name Raspberry Pi Model B MK802 Mele A1000 Rhombus-Tech A10 EOMA-68 Gooseberry board SoC Broadcom BCM2835 Allwinner A10 Allwinner A10 Allwinner A10 A10 700 MHz ARM1176JZF-S core 1 Ghz - 1.5 Ghz CPU 1.5GHz? Cortex-A8 1GHz+ Cortex-A8 1.2ghz Cortex A8 ARM Core (ARM11 family) 1.2 Ghz highest stable Broadcom VideoCore IV, MALI400MP OpenGL ES MALI400MP OpenGL ES 2.0 GPU MALI400MP OpenGL ES 2.0 Mali 400 MHz OpenGL ES 2.0 2.0 GPU RAM 256 MB (shared with GPU) 1GB / 512MB DDR3 512MB DDR3 1gb 512MB Nand Flash - 4GB 4GB 1gb - 16gb 4Gb Video outputs Composite RCA, HDMI, DSI HDMI HDMI, CVBS, VGA HDMI, TV-Out Hdmi Audio 3.5 mm jack - R+L, optical SPDIF Headphones Socket 3.5mm Earphone Jack USB 2 USB 2.0 2 (USB + mini USB OTG) 3 usb USB-2 1x Mini Usb Storage SD / MMC / SDIO microSD SD, SATA Micro-SD, SATA Micro SD Ethernet 10/100 - 10/100Mbps 10/100 Eth - 802.11b/g, WAPI 802.11b/g/n Wireless - - 802.11 b/g/n (Ralink8188) WAPI(Ralink8188) Other ports 8 × GPIO, UART, I²C bus, SPI Internal board: UART, USB - a lot unclear bus ADB, MIC?, CVBS-IN?, I2C? idle 0.34A@5V = 1.7W Power 3.5 W youtube 720p = ~4.6W Power source 5V 5V/2A 5V Size 85.60 × 53.98 mm 88.5 x 35 x 13.4 mm 15.0 cm x 10.3 cm x 3.6 cm ? PCMCIA size Weight 45 g 406 g ? OS included - Android 4.0 Android 2.3 Android 2.3 Debian GNU/Linux, Fedora, ubuntu, Debian, puppy, ubuntu, Debian, Supported OS Puppy Linux, Ubuntu, .