1 of 38

DIGITAL LAB - The Oscilloscope Laboratory #1 K. Dudeck

Introduction:

The oscilloscope, or o-scope, is essentially a voltmeter, a device which displays a voltage in time. If the voltage is a constant in time, for example a 9V battery, the display is a horizontal line. If the voltage varies in time, it is referred to as a signal, and its display on the oscilloscope is more interesting. During this course, most of our signals will alternate at two voltage levels: 0V (binary 0) and 5V (binary 1), as shown below:

5V 0V time (s) <-- T -->

The term square wave is of used to describe the rectangular appearance of this waveform. If a signal, of any waveform, repeats its shape over and over again, it is said to be periodic. The time required, in seconds, for the wave to complete one unique cycle is called the period, T, as shown above. The frequency, F, of the waveform is the number of cycles that go by in one second, measured in cycles/s or hertz (Hz). If the period is the time required for one cycle to pass, and the frequency is the number of cycles per second, then the frequency and period are reciprocally related.

F = 1/T

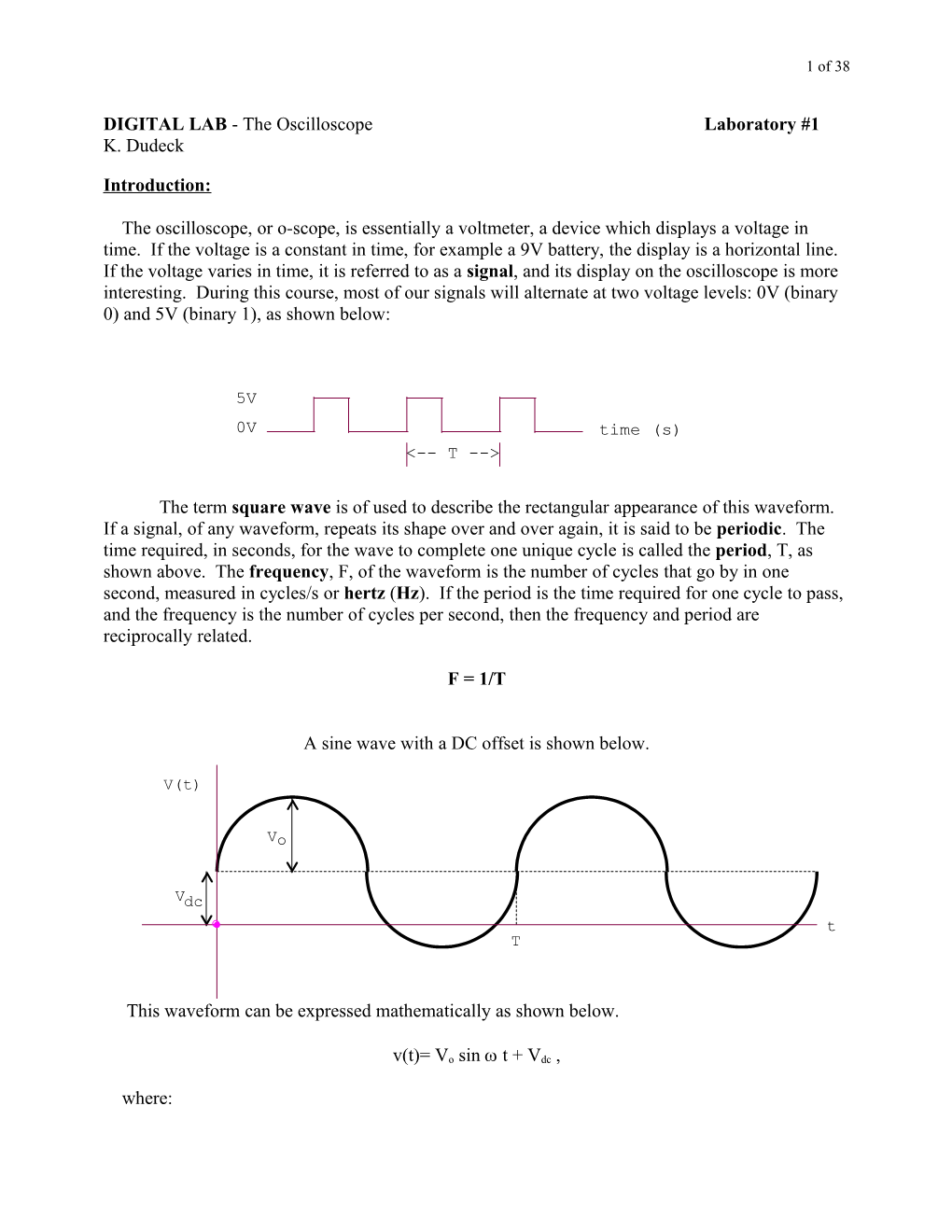

A sine wave with a DC offset is shown below.

V(t) >

Vo > > Vdc > t T

This waveform can be expressed mathematically as shown below.

v(t)= Vo sin t + Vdc ,

where: 2 of 38

Vo is called the amplitude,

is called the radian frequency measured in radians/s ( note: = 2 F ),

Vdc is called the DC offset.

Procedure:

Part I. Components

This is the front panel to the GDS-2000, the portions of this which will be concerned with are the function keys, the individual channel selections, and the auto-adjust. It also has a USB port in front for saving data from waveforms or snapshots of the screen.

These are the probes that come with the set, the probes attach to the unit at point N and has a retractable hook that can be pulled off to reveal a needle like point. Use whichever is more convenient at the time there is no difference. Also on the side of the probe there is an attenuation selector which is used to select between either a true value for measurement or a 1/10nth attenuated measurement useful for measuring values too high for the oscilloscope to safely read. 3 of 38

Part II. Functionality Checks Before using the Oscilloscope (O-scope) you should check to make sure that it is properly set up. This should be done EVERY time.

1) Plug in O-scope and turn on power (button D). 2) Attach Probe to channel one. 3) Ensure the Attenuation switch on the probe is set to 1x. 4) Turn on channel one by depressing button above the probe input until it is backlit. 5) Using the spring loaded hook attachment on the probe, hook around the test signal generator (metal tab S). 6) Press the “Auto-Set” switch on the main function keys panel (Panel E). This automatically sets the display to scale for the signal being measured. 7) Ensure the signal being displayed is 2Vpp and 1 kHz. Do this by verifying the voltage for CH1 (bottom right of display) times the number of grids between the top of the square wave to the bottom is =2V. Check the frequency by both looking at the value after the blinking M on the bottom of the display and multiplying that value times the number of grids it takes to complete one cycle. You can also check the frequency on the bottom-right of the screen.

8) The coupling of the waveform can be changed to dc. This would allow you to see if there was a dc offset on the wave form because the center of the waveform would move up or down corresponding to the amount of dc offset originally present. 9) If you can see this display please move onto next section if there are problems read on. 10) If you cannot see the tops or bottoms of the wave you can adjust the values of the Y axis (volts) via the knob above the probe input plug until you can. If the signal is not centered top to bottom you may adjust this via the vertical position knob, notice the arrow on the left side of the screen with the movement this shows the dc offset of the display (not the dc offset of the signal) 11) If you cannot see a whole cycle of the waveform you may adjust the X axis (time) via the time/Div knob (J) until you see enough of the waveform. 12) If you cannot see the grid squares, push the display button (function keys B), a submenu will come up on the screen, press the F key corresponding to grid and select the grid pattern you prefer. 13) If you see dots and not lines showing the waveform, push the display button, a submenu will come up on the screen; press the F key corresponding to Vectors/dots. 14) If the voltage you see is lower by a factor of 10 then push the channel 1 button a submenu will be displayed, check to ensure that the Probe is set to 1x not 10x’s. 4 of 38

15) If you cannot see any voltage signal at all, press the channel 1 button and make sure the symbol under the “coupling” menu is the shape of a sine wave (AC coupled).

Part III. Measuring input signals In this section you will attach a signal generator to the O-scope. This is to gain practice manually adjusting the O- scope to refine your skills. Do not use the auto-adjust button unless necessary as you will not learn skills you may need later.

1) After Functionality checking the O-scope attach two function generators, one to channel A and the other to channel B. 2) Set the function generator attached to channel A to a triangle wave 1 kHz and the function generator attached to channel B to a sine wave of 2 kHz neither should have any dc offset. 3) Ensure both probes are set at 1x, coupled as AC and both channel selector buttons are backlit. 4) Using the Volts/div (M) knob and the time/div knob (J) show both waveforms overlapping one another. 5) To make it easier to see the different waveforms you can separate them using the vertical position knobs (K). Notice the arrows on the right will move with the center of the waveform to show you where the dc offset of zero would be if you were not splitting the waveforms. 6) Adjust the DC offset of channel 1; notice the arrow does not move showing the difference between a dc offset from the signal generator and a “false” offset from the vertical position knobs. 7) Press the “Hori” button, and then press the f5 key corresponding to XY. The XY mode is a very useful mode where channel A and B are compared to one another rather than each one being compared to time individually. This is very useful for diagnosing problems, signal processing and in this case for producing Lissanjou figures. 8) Disconnect both function generators from the O-scope, you should see a single dot on the screen, using channel A and B’s vertical position knobs to center that dot, this will “zero” the display for the XY mode. 9) Set both function generators the same frequency, sine waves with no dc offset. 10) Attach the signal generators to channel A+B. 11) Adjust the V/div knobs of both channels to show entire waveform. 12) You will probably see a series of closed loop humps. 13) By fine adjusting the frequency of the signal generator attached to channel B you can reduce the number of humps and with sufficient trying you can reduce the signal to a single ovoid loop. This is a lissanjou figure for two signals with the same frequency. By varying frequencies to multiples of one another you can form other lissanjou figures such as saddle (2x frequency of A). These are types of resonance which can show valuable information about input and outputs of circuitry.

Part III. Saving a waveform to a jump drive The digital oscilloscope allows users to save waveforms onto a jump drive so that the images can be transferred to a computer. 1) Insert the jump drive and press the utility button and then press F2 (Interface Menu). 2) Press F1 until “Type USB” appears on the screen. 3) Once the waveform you want to save is on the screen press the Run/Stop button to freeze the image. 4) Then Select Save/Recall and then F4 (Save Waveform) 5) Repeatedly press F1 until Save Image appears on the screen the select F4 (Save) to transfer the image on to the jump drive

DIGITAL LAB - Binary Numbers and Counting Laboratory #2 K. Dudeck

Introduction: 5 of 38

In this lab, you will use a 74LS163 4-bit binary counter chip. This chip essentially counts the number of times that its CLK input goes from binary zero to one. The count is expressed as a four bit binary number. The binary count sequence is: 0000, 0001, 0010, 0011, .... , 1110, 1111, 0000,0001, ...and will be displayed by four LEDs.

If the CLK input frequency (the number of 0 to 1 transitions per second) is large, the distinct count states will not be able to be seen by the lights because they will be blinking on and off too fast for the eye to detect. However, an oscilloscope will be used to notice that the LEDs are in fact going on and off. When the information is viewed this way, the counter chip acts like a "frequency divider."

This lab will also familiarize you with the fundamentals of Integrated Circuits (ICs), as well as breadboard utilization.

Procedure:

1) Obtain a TTL Designer Breadboard Kit. This console provides 5VDC power, TTL switch inputs, TTL LED outputs, and a TTL clock generator. Also obtain an oscilloscope, probes for the o-scope, some #24 gauge solid wire pieces, and a 74LS163 chip.

2) Turn on the TTL Designer and set the internal power supply to 5VDC (TTL). Verify this DC voltage with the o-scope. You will be using the scope's 10X probes in this lab. These probes attenuate the voltage by a factor of 10, therefore you will need to use the 10X mark when reading the o-scope's set sensitivities (Ch. 1 & Ch. 2 Volts/div).

3) Look up the 74LS163 in your TTL Data book. Locate the Vcc and GND pins, what are the pin numbers? Turn off the power to the TTL Designer and carefully place the 74LS163 in the center of the breadboard. Connect the Vcc pin to +5V and the GND pin to the Ground. These power connections are always required for every chip used, and to avoid damage to the chip, should be made when the power is off.

4) Locate the QA, QB, QC, and QD output pins on the chip, record these pin numbers. These pins are the 4-bit binary count with QD being the most significant bit. Connect QD to the left most LED, and moving left to right on the LEDs, connect QC, QB, and QA.

5) Locate the CLK input pin on the 74LS163, what pin number is this? Connect this pin to the push button pulser switch.

6) Turn on the power, record the displayed binary count on the LEDs by assigning a one if a LED is ON, a zero if a LED is OFF. 6 of 38

7) Push the pulser button once. What is the new count? Continually push the pulser button until all four LEDs are off. Now push the pulser once more and record the binary number, it should be 0001. Do this 15 more times and make a table of the count sequence. You should recognize this binary pattern, this chip is a binary counter.

8) Set the Clock Frequency to 1Hz, and remove the wire from the pulser switch and connect it to the clock. Observe the LEDs, now the clock is simulating a switch being pushed once a second.

9) Increase the clock frequency to 10Hz and observe the LEDs. Now increase the clock frequency to 100Hz, 1kHz, and finally to 10kHz. Can you see the count sequence anymore? If you can, you have a really fast eye! If you can not, you will need a faster eye, an o-scope.

10)Keeping the Clock frequency set to 10kHz and using Channel 1 on the o-scope, measure the clock period and verify the 10kHz frequency.

11)Connect a second probe to the QA output of the 74LS163 and display both the Clock waveform on Ch. 1 and the QA waveform on Ch. 2. Notice the period of QA is twice that of the Clock. How do the frequencies compare?

12)Now look at the QB waveform. How does this period compare with the clock? Repeat this for QC and QD. Draw the waveforms you see for all 5 waveforms on a piece of paper. Can the 74LS163 be thought of as a "frequency divider"? For example, is the frequency of QB equal to 10kHz/4 = 2.5kHz? Is the frequency of QC equal to 10kHz/8 = 1.25kHz? ,etc.

7 of 38

DIGITAL LAB - Logic Inverter Laboratory #3 K. Dudeck

Introduction:

The binary number system is essentially a code which requires two discrete states, generally designed 1 and 0. This representation is basic to digital devices and systems, and these two states are easily realized as voltage levels in an electronic circuit. Any two voltages could be used, but in currently available integrated circuits (ICs) the most common voltages chosen are +5 and 0 V dc. One then makes the following definitions: Binary 1 = +5 V dc, Binary 0 = 0 V dc.

These two states are often referred to as logic levels, and thus a voltage of +5 V dc represents a logic level 1 (sometimes called logical 1), while 0 V dc represents a logic level 0 (logical 0).

An important fundamental logic function is the conversion from one logic level to the other, i.e., the ability to change a 1 to a 0 or a 0 to a 1. Changing from one logic level to the other is called complementing. A unit which will provide the complement is quite easy to realize with an electronic circuit, since this simply means changing +5 V dc to 0 V dc, or vice versa.

A basic electronic circuit whose output is the complement of its input is the inverting amplifier. The symbol for an inverter as used in digital electronics is shown in Fig. 1a. The triangular part of the symbol shows that this is an amplifier; it is especially important to note that the small circle on the output signifies signal inversion. Thus, if VIN=0 V dc, then VOUT=+5 V dc, and if VIN=+5 V dc, then VOUT=0 V dc. A tabular listing of the voltage outputs for each input voltage for this inverter is called a truth table, and this is shown in Fig. 1b.

VIN VOUT Fig. (1a) V 2 1 0 1 Inverter IN VOUT Fig. (1b) 1 0 Truth table

The typical IC inverter is composed of a number of transistors, resistors, and diodes (see, for example, the data sheet for an SN7404) and thus has some voltage gain from input to output. When used in a digital system, the input voltage is always either +5 or 0 V dc, respectively. However, if VIN in Fig. 1a were increased slowly from 0 to +5 V dc, VOUT would start at +5 V dc and at some point it would shift (switch) suddenly to 0 V dc. A plot of VOUT versus VIN is known as a 8 of 38 transfer characteristic, and an ideal curve for an inverter is shown in Fig. 2 on the next page.

Notice in Fig. 2 that VOUT remains at +5 V dc until VIN goes more positive than 1.5 V, and then VOUT switches to 0 V dc. The value of VIN at the point where VOUT switches VOH Is called the threshold voltage, VOUT(V) > and in this instance it is 1.5 V. The value of VOUT 5 below the threshold is often 4 designed VOH (V out high), and the value of VOUT above 3 the threshold is then VOL (V out low). 2 Threshold Voltage V 1 OL 0 > 1 2 3 4 5 VIN(V) 0 Fig. 2. Ideal transfer characteristic.

It is important to note that VOH and VOL may be significantly different from the ideal values in Fig. 2. As an example, VOH and VOL might be given as +4.6 and +0.3 V dc for a device marketed by some manufacturer (Fig. 3). This is acceptable, however, since there are still two clearly distinct logic levels, namely 1=+4.6 V dc and 0=+0.3 V dc. Furthermore, the actual values of VOH and VOL will be affected by the type of load connected to the output of the inverter.

It is equally important

V (V) > to note that the threshold OUT Fig. 3, Typical transfer characteristic. voltage may not be as clearly 5 defined as shown in Fig. 2; that is, the line from VOH to 4 3 Threshold Voltage (Normal) VOL may not be vertical but slope as in Fig. 3. In this 2 case, the threshold voltage V might be taken as the point 1 OL where VOUT has moved halfway from VOH to VOL as shown 0 > (about 1.1 V). 1 2 3 4 5 VIN(V) 0

V VIN In a practical situation, data sheets will give values for VIN below which VOUT will remain at VOH, this value of VIN is frequently called VIL (V in low). Similarly, a value for 9 of 38

VIN above which VOUT will remain at VOL is generally specified as VIH (V in high). The portion of the curve between VIL and VIH is referred to as the transition region; operation in this region is to be avoided for digital applications. See the appendix for 54XX, 74XX dc characteristics. Procedure:

Equipment and parts required: 1 signal source, 6.3 V rms 60 Hz 1 diode, 1N91 or equivalent 2 resistors, 330 ,1/4 W 1 hex inverter, 7404 TTL 1 volt-ohm-milliammeter (VOM) 1 oscilloscope, dc-coupled y, 5 V dc

1) Examine the data sheet for the 7404 hex inverter. It is called "hex" since there are six inverters. Note carefully the required power-supply voltage V and the proper pin connections. Apply power to the 7404.

2) The simplest method for determining proper operation of an inverter is a static test. This is performed by simply connecting a clip lead to the inverter input. The other end of the clip lead should then be alternately connected to ground (VIN=0 V dc) or =VEE (VIN =+5 V dc) while monitoring the output to see if it does indeed provide the complement of the input. Use a clip lead to perform this static test on each of the inverters; monitor the output with a VOM to determine proper operation.

Complete the truth table here for one of the inverters tested.

VIN (V) VOUT (V) 0

+5

Record the value of VOUT when VIN is left open-circuited.

VOUT with VIN open-circuited = ______.

3) To verify that one inverter can indeed drive another, connect two inverters in cascade as shown in Fig. 5. Apply the voltages for V1 as shown in the following table (use a clip on the input of INV 1), and record the resulting values for V2 and V3.

INV 1 INV 2 V1 (V) V2 (V) V3 (V) V 1 2 2 1 2 0 V V 1 3 +5 10 of 38

4) +5 The transfer characteristic of an inverter can be displayed on an oscilloscope by using a simple half-wave rectifier as a horizontal sweep circuit, as shown in Fig. 6. Connect this circuit as shown and adjust the horizontal and vertical oscilloscope inputs to a convenient scale, for example, 1 or 0.5 V/cm.

Test Unit Oscilloscope

1 2 Vert Horiz dc dc

1N91 330

6.3 V rms 60 Hz 330

Fig. 6.

Use dc coupling to the oscilloscope. The display observed should be quite similar to that sketched in Fig. 3. Carefully sketch the actual curve observed for the circuit shown Fig. 6 and shown in Picture 1; take care to locate critical points along the "knees" of the curve. It is absolutely essential to keep all leads short; otherwise, the observed curve will exhibit hysteresis. 11 of 38

DIGITAL LAB - Binary Input/Output Laboratory #4 K. Dudeck

Introduction:

This laboratory explores the concepts of digital input and output (I/O). When one designs a digital circuit, the implementation probably requires the use of more than one gate. The design may also require that the output of one gate needs to drive the input of another gate. The 74XX series of TTL integrated circuits are fabricated to achieve this result. Thus, the circuit designer does not have to worry about the electrical ability of one gate to drive another. It always will, provided the ICs are of the same class: TTL.

In addition, an actual application will inevitably need to accept digital inputs from the external world (i.e. switches, sensors), as well as drive some real world output devices (i.e. lights, relays). The electrical characteristics of the input and output connections to the digital circuit must be considered for proper operation.

In previous labs, the TTL Designer Kit was used to provide four switched binary inputs and four LED binary outputs. The convenience of the TTL designer isolates the student from the electrical requirements needed to make this I/O work properly. In this lab, we will not use the TTL Designer, but use a simple breadboard to construct the elementary I/O circuits that are already provided internally by the TTL designer kit.

PART I - Input Circuitry.

TTL inputs on 74XX series chips are usually interpreted as a binary HIGH when left unconnected (floating), not LOW as would be expected. In order to send a binary LOW to an IC, the input must be "grounded" in order to get 0V to the input. At the same time, in order to guarantee a binary HIGH to an IC input, the pin should be connected to 5VDC. In order to get both voltage levels from a single switch, a external "pull- up" resistor (1 to 5k in value) must be connected as shown in figure 1a and 1b. 12 of 38

+5V +5V

1k TTL Input

1k TTL Input

Figure 1 - Switch Controlled TTL Input Circuits

Switch Input Switch Input OPEN 0V OPEN +5V CLOSED +5V CLOSED 0V 1a - High Side Switching 1b - Ground Side Switching

Procedure

1) Obtain a DC power supply, a digital voltmeter with leads, a simple breadboard, a 8 element DIP switch, and four 1k resistors. Using one of the switches, connect the High Side Switching TTL circuit shown in Figure 1a.

2) Place the voltmeter on the input node and experimentally verify that the circuit produces 0V when the switch is OPEN and +5V when the switch is CLOSED, as listed in the operation table. The voltmeter is recording the voltage that an IC input would see if it were in its place.

3) Now re-connect the circuit so that it uses Ground Side Switching, as show in Figure 1b. Experimentally verify that this circuit operates like the complement of the High Side Switching circuit. This Ground Side Switching circuit is more desirable than the High Side Switching, for electrical noise reasons.

4) To get this circuit to functionally operate like Figure 1a, connect the input into a 7404 inverter as shown below. This circuit is the standard circuit for producing a positive logic TTL input.

+5V

1k

1 2

7404

Figure 2 - TTL Input Circuit. 13 of 38

5) Place the voltmeter on the output of the inverter and experimentally verify this circuit produces 0V when the switch is NOT CLOSED (open), and +5V when the switch is CLOSED.

6) Using three more switches from the DIP switch, three more 1k resistors and three more inverters (from the same chip!), connect three more of these circuits. You now have a 4-bit binary input, like the one on the TTL Designer Kit. Leave these circuits connected.

PART II - Output Circuitry.

The output of a TTL gate produces a +5VDC voltage when it is ON, and this output can be used to drive the input of another TTL gate. However, this output can not be used to directly drive a "real-world" device, for example like an LED. The electrical current required to drive an LED is more than a normal TTL gate can provide. In order to accomplish this, a special class of TTL gates exist, which have open collector outputs, sometimes referred to as drivers.

A gate with an open collector supplies ground or 0V when it is OFF, but it does not supply any output voltage when it is ON. In order to get the desired ON voltage, it must be supplied externally via a "pull-up" resistor as shown in Figure 3.

VCC = +5V

330 TTL Output 1 2

7417 LED

Figure 3 - TTL LED Output Circuit

Generally speaking the voltage on the pull-up resistor can be any voltage required for the LED to operate properly. In this case, the 5V is used with a 330 resistor which causes approximately 15mA of current 14 of 38 to flow through the LED when it's ON. When the gate is OFF, it "shorts out" the LED, and causes the 15mA to bypass the LED and flow through the gate instead.

1) Connect the circuit shown in figure 3 using a 7417 buffer/driver chip. Note: the LED has polarity. It must be inserted so that the cathode is connected to ground, if not, it will not light. If the LED does not light, turn it around and try again.

2) Connect a wire from one of your TTL input circuits, off the 7404 output, to the input of your LED output circuit.

3) By opening and closing the switch, you should be able to turn the LED on and off. There is no digital logic in the circuit yet, but if you can turn the LED on and off, you have you TTL input and TTL LED output circuits working properly.

4) Construct three more TTL LED circuits and feed each of them with one of the three remaining TTL Switch Input circuits. You can now send and display a four-bit binary number.

5) By modifying this circuit, design a circuit that displays the 1's complement of the four-bit binary set by the switches.

PART III - Pulser Circuits (optional)

When a switch closes, we think that it produces one 0V to 5V input pulse. But real switches have "switch-bounce", a period of time where the switch bounces between open and closed before it is firmly seated and electrically constant. This switch bounce can not be seen with the eye, because it lasts for only a short amount of time, usually less than 1ms. However, if the switch input goes into a TTL input that "counts" the number of pulses (low to high transitions), every time a switch in opened and closed, will not produce a count of one, but actually a random count. In order to "clean-up" the switch pulse, a pulser circuit must be constructed. This is accomplished by first slowing up the switch bounce, by using a capacitor charging and discharging (RC circuit), and then using a special TTL input circuit gate type called a Schmitt Trigger. A Schmitt Trigger gate has the characteristic of hysteresis which means it remembers its last valid input when the input is actually in the invalid region: above the LOW voltage threshold and below the HI voltage threshold. These two concepts, used together, will eliminate the switch bounce.

Procedure

1) Construct the circuit shown in Figure 3. The counter output (QD, QC, QB, and QA) will be displayed on the set of four LED output circuits 15 of 38

built in Part II. Use the fifth switch on the DIP package to make the pulser circuit, which feeds into the counter input.

2) By opening and closing the switch, verify the count sequence as was done in the previous lab.

3) Remove the capacitor and try again. Does it work as well?

VCC = +5V

330 3 14 1 2 +5V 4 A QA 13 5 B QB 12 C QC 6 11 7417 LED D QD 15 10k 7 RCO Schmitt 10 ENP 1 2 2 ENT 9 CLK 1 LOAD CLR 7414 74LS163 4 each Connect QB, QC, and QD to remaining three

Figure 4 - Pulser Circuit Input into 4-bit Counter.

DIGITAL LAB - Combinational Analysis Laboratory #5 K. Dudeck

1) Analyze the three combinational circuit below and write a boolean expression for each function: F1, F2, and F3.

2 A 1 3

1 B A 3 1 1 F2 2 3 3 B 2 2 C 2 B 1 3 1 F1 1 3 C A 3 2 2 B

1 3 2

1 1 B 3 A 3 2 F3 2 2 C B 3 C 16 of 38

2) Simplify the expressions for F1 and F2 using identities. Do either of these circuits functionally equal F3?

3) Build the circuits for F2 and F3 and experimentally obtain their truth tables. Use three switches to implement the input variables A, B, and C. You will need to use inverters (not shown) off of the switches to make the complemented literals. Are the measured truth tables the results you expected?

4) Build the circuit below using one NAND chip (4 gates per chip), and experimentally determine the truth table for F. What are the minterms of this function ( m (?) ) ?

Show how you would build this circuit using AND and OR gates. Is there a single gate that can be used which would implement this function? If you find the gate, experimentally verify its truth table to show that it does equal the function F.

1 3 2

1 1 A 3 3 F 2 2 B 1 3 2

DIGITAL LAB - Combinational Design Laboratory #6 K. Dudeck

In this lab you will design a control system for an electrically activated roadway fence which is the access into an automotive service station. The service station has four stalls ( 1,2,3, and 4) and three mechanics on duty at all times. When a car pulls into a stall, a limit switch automatically closes and sends a binary "1" to your control circuit indicating a car is in that particular stall. The switches are labeled S1, S2, S3, and S4, corresponding to the stall numbers.

Road Fence 17 of 38

Stalls

# 1 # 2 # 3 # 4

One mechanic is needed per stall (when a car is there) except for stall #2, where two mechanics are needed because that stall services transmissions. Your control system should send a "0" to the fence motor to close the fence when all the mechanics are busy and thereby not allow any more car through, and send a "1" to open the fence when more cars can be serviced.

1) Design a truth table which satisfies the required logic.

2) Derive and simplify the Boolean expression.

3) Implement the solution with “Logic Works”.

3) Build the control system in the simplest way possible. This can be implemented using only two chips, how?

4) Experimentally verify that your design works for the given problem.

DIGITAL LAB - BCD to Seven Segment Decoder/Driver Laboratory #7 K. Dudeck

1) In this lab you will learn how to use a BCD to Seven Segment Display Decoder/Driver. This chip takes a 4-bit BCD number as an input, and decides which LEDs to turn on in the seven segment display, which will generate a visual representation of the decimal number. Essentially there are two types of displays: Common Cathode, and Common Anode. If the display is Common Cathode, all the cathodes (negative side) of the LEDs inside the packaged display are connected together internally and one common GND pin is made available (see below). 18 of 38

f g a b h a' f' Vcc' b' f g a b GND GND f' a' b'

a a' a a' f b f' b' f b f' b' g g

e c e' c' e c e' c' h h' h d d' d d'

e d c Vcc e' d' g' c' h' e d c h e' d' g' c' h'

Dual Common Anode (Active Low) Seven Segment Display Dual Common Cathode Seven Segment Display

Use 74LS47 Decoder/Driver Use 74LS48 Decoder/Driver

In this case, a 5V signal to the appropriate LED input (a through g) will cause that particular LED to illuminate. A 74LS48 has positive outputs to accomplish this task. On the other hand, if a common anode display is used, all the anodes of the display are connected together to a common 5V supply. It therefore requires a ground (or binary "0") to turn on the LEDs. In this case a 74LS47, which has inverted outputs, is used to drive a Commode Anode display.

2) Determine which type of display you have assuming you have a Common Cathode display, shown above, and placing ground on the "GND" pin, and 5V on the "a" input pin. If the "a" LED lights, then you have a Common Cathode display. Move the 5V to the other input pins (b->g) and verify that all seven LEDs work.

3) Leave the "GND" pin of the display still connected to ground, and remove any of 5V test wires used to test the display. If you have a common cathode display obtain a 74LS48 Decoder/Driver (otherwise use a 74LS47) and connect the a -> g outputs of the decoder/driver to the a -> g inputs of the display. Connect the A,B,C,D inputs of the decoder/driver to the four switches of TTL designer box. Test the circuit by simulating all 16 4-bit binary numbers by the switches and observing the display. What happens when the input number is greater than 9?

4) Test the lamp test feature of the decoder/driver by momentarily grounding the LT input. Conversely, test the blanking feature of the chip by momentarily grounding the RBI input.

5) Now build the electronic digital clock circuit by adding a 74LS163 counter as shown below. Set the frequency of the clock to 1Hz. Do not include the NAND gate at first. Notice how the circuit counts zero to fifteen. Explain why the NAND gate corrects the circuit so it is truly a decimal counter. 19 of 38

U? U? 3 14 7 13 4 A QA 13 1 1 A 12 5 B QB 12 2 2 B 11 6 C QC 11 6 4 C 10 D QD 15 4 8 D 9 7 RCO 5 BI/RBO E 15 GND 10 ENP 3 RBI F 14 2 ENT LT G CLK 9 7448 Clock 1 LOAD CLR 74LS163

1 3 2

74LS00

6) (Challenge) Design, build, and test a circuit which will count and display from 00 to 99, implement using “Logic Works”.

20 of 38

DIGITAL LAB - Decoders and Mutiplexers (2 weeks) Laboratory #8 K. Dudeck

In this lab you will have the opportunity to gain hands on experience with decoders and multiplexers, learn of a different type of output called a tri-state, and discover a new application using open-collector outputs.

PART I. Open Collector Outputs. We have seen thus far that there exists two types of TTL outputs, Normal and Open Collector. Normal TTL outputs supply 5V when "on" and ground, 0V, when "off". Normal TTL outputs can NEVER BE CONNECTED TOGETHER because if one is on and another off, a short circuit will result and cause damage to both gates.

Open collector outputs supply ground when "off" but just float (like an open circuit) when "on". If an output voltage is desired, it must be supplied externally through a "pull up" resistor, as seen in a previous lab. Since the outputs do not supply output voltage, they can be connected together with +5 V out damage. 1k

U?A A 1 2 1) Connect the two 74LS17 open-collector buffers together 7417 drive their inputs with two switches as shown and determine U?B B the resulting the truth table. 3 4

7417 2) What is the equivalent logic that occurs when two open collector outputs are connected LED together?

3) This result seems to indicate that any boolean expression could be implemented in a single level using only open collector "NAND" gates connected together simulating a final invert-AND (NOR) gate. This implementation would yield the complement of the function. In order to generate the function itself, the complement needs to be implemented.

Show how you would implement the boolean expression:

F(A,B,C,D)= m (0,5,7,8,13,15) 21 of 38

using only open collector NAND gates (74LS03).

4) Implement your design using “Logic Works” and verify that it works.

PART II. Tri-State Outputs.

A tri-state output is a combination of a Normal TTL and an open collector output. The output of the gate is determined by its logic (as any gate is) and a controlling input, called C, that can make the gate function either a normal TTL output (5V or ground depending on the logic), or floating (open circuit) like a open collector. If the gate

is floating, however, it acts like it is disconnected, or high impedance (Z) regardless of the inputs or logic. In this manner the output is said to have three states: "on" (5V), "off"(ground, 0V), or "High Z" (disconnected). See the figure below and the function table for a tri- state buffer of a 74LS125. C C A Y = A 1 0 0 0

2 3 A Y 0 1 1 1 X High Z 74LS125

Notice the C input requires a low input to enable the tri-state output. This is so that the tri-state is normally disabled if the C input is not connected.

Many tri-state gates can be connected together if the controlling input, C, of only one is enabled at a time. It is typical to use a 1 0 2 1 3 2 4 1 3 5 4 6 2 3 3 14 23 5 7 4 A QA 13 22 A 6 8 A 5 B QB 12 21 B 7 9 74LS125 6 C QC 11 20 C 8 10 D QD 15 D 9 11 7 RCO 10 13 10 ENP 11 14 4 2 ENT 12 15 9 CLK 18 13 16 5 6 Clock 1 LOAD 19 G1 14 17 CLR G2 15 B 74LS125 74LS163 74LS154 1 0 OUT

9 8

C 74LS125 1 3

12 11

D 74LS125 22 of 38 decoder with inverted outputs (only one low) to drive the C input of tri-states to guarantee that only one tri-state output is internally connected at a time while all the others are disconnected (high Z). See the circuit below.

1) Connect the circuit shown on the previous page. Set the clock frequency to 1kHz and monitor the tri-state bus with an oscilloscope. The two bit counter can be built by using only the Qa and Qb outputs of a 74LS163. A 2x4 decoder can be realized by using only the A and B inputs and grounding the C and D inputs of a 74LS154 (4x16 decoder). This restricts the decoder to the 0 to 3 outputs only.

2) Vary the switches as you watch the oscilloscope. Think about want you are seeing. As the counters counts each of the four digital channels (simulated by the switches) takes its turn on the bus. You have built a 4-bit parallel to serial converter by multiplexing the four channels into a single serial stream. Note: Multiplexer chips are made from decoders and tri-states.

3) Unground the C and D inputs of the decoder and connect them to the Qc and Qd outputs of the counter. What happens to the display?

PART III. Multiplexer Application.

In Part II you essentially built a multiplexer from a decoder and tri- states. In this part, replace the decoder and tri-states with a 74LS153 dual 4 to 1 multiplexer.

1) Place the oscilloscope on the output of the multiplexer and verify that you still have a 4-bit to serial converter.

2) Suppose you wanted to convert the serial back to parallel at the other end. You will need to build a serial to parallel converter. The circuit on the following page does this. Only two wires need to be run from the transmitting end: the serial data from the multiplexer, and the clock for synchronization. The 74LS154 decoder is being used as Demultiplexer. Build this circuit first using “Logic Works” and then on the bread board. Test that when switches are opened and closed on the transmitter end, the corresponding lights follow.

3) Slow the clock to 1 Hz and observe how the lights are really multiplexed one at a time. When running at the higher clock speed, your eye can not see that these lights are really "time sharring" the multiplexed channel.

23 of 38

A

B 6 7 5 1C0 1Y C 4 1C1 3 1C2 D 1C3 10 9 11 2C0 2Y 12 2C1 13 2C2 2C3 3 14 14 4 A QA 13 2 A 5 B QB 12 1 B 6 C QC 11 15 1G D QD 15 2G Data RCO 7 74LS153 10 ENP 2 ENT 9 CLK 1 LOAD CLR 74LS163

Clock 1

7404 1 3 4 0 2 1 3 2 2 4 7404 3 5 4 6 3 14 23 5 7 5 6 4 A QA 13 22 A 6 8 5 B QB 12 21 B 7 9 C QC C 8 6 11 20 10 7404 TO D QD 15 D 9 11 7 RCO 10 13 LEDS 10 ENP 11 14 9 8 2 ENT 12 15 9 CLK 18 13 16 LOAD G1 14 1 19 17 7404 CLR G2 15 74LS163 74LS154 11 10

7404

PART IV. Tri-state Application. (OPTIONAL) A car factory has two final assembly lines. In one line sports cars roll off finished and in the other, passenger cars. In a day, no more than 9 cars are roll off completed. The plant manager wants a digital circuit that will compare the number of cars finished by each line, and display the greater number on a 7-segment display.

PART V. How do I do this? (OPTIONAL) A garage has 9 service stalls. If a car is in the stall, a floor switch is closed and sends a "1" to you to process as a digital input. There are nine inputs. Design a circuit that displays the number of occupied stalls on a seven-segment display. Encoders and decoders may be useful. 24 of 38

DIGITAL LAB – Sequential Design Laboratory #9 K. Dudeck

In this lab you will design the control system for an Electrical Heater. The heater has a heater element, H, and a fan, F. The unit has two inputs thermocouple inputs, TH and TL. These inputs are temperature controlled switches that are true when the room temperature is above the thermocouple set point of the switch. The set point for TL is 2 degrees below the desired room temperature and the set point for TH is 2 degrees above the desired room temperature. The unit will not change it’s state if the room temperature is in between both set points, namely TL=1 TH=0. If the unit is running, it stays running until the upper temperature is reached. If the unit is not running, it stays off unit the lower temperature is no longer made. This is called dead band control.

The state is define as [H F] for Heater Fan. The input combination is defined as: (TL TH) Note: the input (01) can not exist.

The control sequence is as follows:

The heater turns on whenever both TL and TH are false and then fan ALWAYS turns on one clock pulse later. The unit stays in this state until both TL and TH are true. The heater will then turn off then the fan will ALWAYS turn off one clock pulse later.

1) Design the circuit that satisfies this design using two J-K flips.

2) Simulate the design using Logic Works.

3) Build the circuit and use a clock frequency of 1 Hz.

4) Challenge: Modify the design so that the Fan comes on 4 clock pulses after the Heater goes on, and the fan goes off two clock pulses after the heater goes off. Use Logic Works to show this design.

25 of 38

DIGITAL LAB - Pulse and Clock Generation Laboratory #10 K. Dudeck

In this lab you will learn how to generate a digital pulse with a time duration (called pulse width) of your own design. The device which provides the capability to accomplish this is a 74LS123 dual Retriggerable Monostable Multivibrator (commonly referred to as a "one- shot"). Basically a "one-shot" generates one, and only one, pulse every time it is triggered by an input, that is either a positive going pulse or a negative going pulse. The length of the pulse, , is controlled by an external resistor, R, and capacitor, C, that varies the discharge rate. The pulse length, , can be calculated as shown below:

= 0.33 R C .

The figure below shows the following: one of the two one-shots of 74LS123 dual one-shot, how the external R and C are connected to the chip, and the function table. Notice the variety of ways in which an output pulse can be triggered: with a positive edge on input CLR or B, or with a negative edge on input A.

INPUTS OUTPUTS

CLR A B Q Q VCC

L X X L H 14 CEXT

X H X L H C 15 REXT/CEXT X X L L H R 1 13 2 A Q H L 3 B 4 CLR Q 74LS123 H H

L H 26 of 38

PART I: Design and implement two separate one-shot configurations. Use 0.1 F capacitors. The first should put out a pulse of 330 s when triggered from a negative edge, and the second put out a pulse of 726 us when triggered from a positive edge. In order to test your design, use the TTL output of a function generator set to 500Hz for the one shot triggers. Look at the function generator output and the one-shot output simultaneously on an oscilloscope. Are the pulse widths at the designed values?

What happens as you slowly vary the function generator from 500 to 5000 Hz?

PART II. Pulse Positioner: In many applications it is desirable to delay a pulse of a certain amount of time after the trigger.

Trigger Input Delay Time

Output Pulse

This is accomplished by using one one-shot to provide the delay and trigger the second one-shot from the output of the first. How would you design a pulse of 330 s that is generated exactly 726 s after a triggering pulse? Design and test your solution.

PART III. Free Running Clock.

If the output of the first one-shot is connected to the input of the second one-shot, and the output of the second is connected to the input of the first, a free running square wave oscillator is built (see below). The duty cycle of a square wave is defined as the ratio of time that the wave is "high," compared to the total period. Therefore a duty cycle of 0.5 is a standard symmetrical wave.

1) Design and test a 1515Hz, 0.5 duty cycle square wave oscillator.

2) Design and test a 950Hz, 0.76 duty cycle square wave oscillator. 27 of 38

VCC VCC

R1 R2

C C 1 1 1 1 3 2 1 5 4 1 0 9 7 6 C B A R C C B A R C L E E L E E R R X X X X T T T T / / C C E E X X T T Q Q Q Q 4 1 1 5

3 74LS123 2 74LS123

OUTPUT 28 of 38

Digital Lab – Field Programmable Logic Devices (FPLD) Supplemental Lab K. Dudeck & T. Wachs

Introduction: The Field Programmable Logic Device is basically a collection of logic gates arranged into counters, encoders, flip-flops and other commonly used arrays arranged on a common board, ours also has extra inputs, outputs, displays (LED’s, LCD’s) and switches. Logic devices are mass produced as blank boards with thousands of components connected via fusible links, these links are then “burned” by using a “programmer” to isolate the logic functions wanted. Basically you remove the unneeded connections and components. Unlike most commercial logic devices a FPLD has fusible links which can be reset (reconnecting everything) so that it can be reprogrammed. To use a FPLD you must first decide which logic function you want to make. We will be constructing an “and” gate, an “or” gate, and a program which will add two 8-bit binary numbers inputted via switches and display a 2- digit hexadecimal on the LCD display or say “hi” when a specific button is depressed. Then using a programming language called VHDL (Very high speed Integrated circuits Hardware Descriptive Language) or a graphical model (similar to logic works in use) the logic function is built. Then you must compile the logic function, which means you translate the logic function into a map of fuses that must be blown so that the circuit works. Within the program it is possible to test and verify that the function you have built will work as expected. After testing you can download this map into the FPLD where the fuses will be blown and you can test your design using real inputs. We will be using the UP1 development board:

The UP1 development board has 2 Liquid Crystal Displays, 4 push-buttons, two chips, multiple LED lights, jumpers and various input/output hook-ups. The program we will be using is Altera MAX +PLUS II 10.2 Student Edition software. This Program should already be in the lab computer, free editions of this software can be obtained at (http://www.altera.com/support/licensing/lic-university.html). Instructions on how to set up this program and board setup will be explained in the supplement at the end of this Lab. Assume the program and board is already configured for this lab. Procedure “ Or” Gate

Opening the Software 1) We will open and download into the FPLD the VHDL Code for an OR gate program in which the two push button switches control the decimal point on the LED display. (Also see the “Rapid Prototyping of Digital Systems” book Chapter 1.) 29 of 38

2) Run the MAX+PLUS II software 3) Select File=>Open>orgate.vhd

4) The Code should look like this. LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all;

ENTITY orgate IS PORT( PB1, PB2 : IN STD_LOGIC; LED : OUT STD_LOGIC ); END orgate;

ARCHITECTURE a OF orgate IS BEGIN LED <= NOT( NOT PB1 OR NOT PB2 ); END a; 5) Select File=>Project=> Set 30 of 38

Project to current file

6) You now have a file “orgate.sof” that can be downloaded to the board.

Downloading Program into board 31 of 38

1) Select MAX+PLUS II => Programmer 2) From Options =>Hardware Setup selected LPT1. If a window comes up that displays “No Hardware” use the pull-down to change to “Byteblaster II” 32 of 38

3) VERIFY JTAG; Select JTAG =>Multi- Device JTAG chain so the checkmark appears. 4) Select JTAG=> Multi-Device JTAG Setup. Select the Device name to be EPF10K70. Hit Select Programming File and Select c:\max2work\vhd1\orgate.sof (previously created small program). Click OK. Click the ADD button. The new filename should move in to the list in the inner window. 33 of 38

5) Select Detect JTAG Chain info button, board has to be installed for this to work. . System should respond “JTAG chain information confirmed by hardware check”. If not, double check the hardware connections. 6) The Configure button in the programming window should be highlighted. If it is not, try to fix it by opening Options => Hardware Setup and confirm the port setting. If you still have problems confirm that the printer port BIOS setting uses ECP or EPP mode. “ And” Gate Procedure to make “And” gate is same as “Or” gate except the program must be altered. Rewriting the Software 7) We will write and compile the VHDL Code for an “AND” gate program in which the two push button switches control the decimal point on the LED display. (Also see the “Rapid Prototyping of Digital Systems” book Chapter 1.) 8) Run the MAX+PLUS II software 9) Select File=>Open> orgate.vhd 10) Alter code (shown in BOLD) as follows: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all;

ENTITY andgate IS PORT( PB1, PB2 : IN STD_LOGIC; LED : OUT STD_LOGIC ); END andgate;

ARCHITECTURE a OF andgate IS BEGIN LED <= NOT(NOT PB1 AND NOT PB2) ; END a; 34 of 38

11) Then select Save as “andgate.vhd” 12) Select File=>Project=> Set Project to current file 13) Now you can compile by selecting File=> Project => Save and Compile. 14) There should be 0 errors and 0 warnings. 15) You now have a file “andgate.sof” that can be downloaded to the board. Downloading Program into board 7) Select MAX+PLUS II => Programmer 8) From Options =>Hardware Setup selected LPT1. If a window comes up that displays “No Hardware” use the pull-down to change to “Byteblaster II” 9) Select JTAG =>Multi- Device JTAG chain so the checkmark appears 10) Select JTAG=> Multi-Device JTAG Setup. Select the Device name to be EPF10K70. Hit Select Programming File and Select c:\max2work\vhd1\orgate.sof (previously created small program). Click OK. Click the ADD button. The new filename should move in to the list in the inner window. This should already be done for you. 11) Select Detect JTAG Chain info button, board has to be installed for this to work. . System should respond “JTAG chain information confirmed by hardware check”. If not double check the hardware connections. This should already be done for you. 12) The Configure button in the programming window should be highlighted. If it is not, try to fix it by opening Options => Hardware Setup and confirm the port setting. If you still have problems confirm that the printer port BIOS setting uses ECP or EPP mode.

“ Hi”

Procedure to make “Hi” is same as before with exception that the program must be written, then compiled and tested. The VHDL language should be replaced with: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all; --USE IEEE.STD_ARITH.all; --USE IEEE.STD_UNSIGNED.all; --BCD display -- DL3-DL0 lower four dip switches -- SL6-SL0 Least Sign display a-g -- DH3-DH0 upper four dip switches -- SH6-SH0 Most Sign display a-g ENTITY bcdled IS PORT( PB1, PB2: IN STD_LOGIC; --LED: OUT STD_LOGIC; DL: IN STD_LOGIC_VECTOR(3 downto 0); DH: IN STD_LOGIC_VECTOR(3 downto 0); SL: OUT STD_LOGIC_VECTOR(6 downto 0); SH: OUT STD_LOGIC_VECTOR(6 downto 0) ); END bcdled;

ARCHITECTURE seg OF bcdled IS BEGIN --Pressing PB1 makes the display say HI SL <="1001111" when PB1='0' else "0111000" when DL="0000" else "0110000" when DL="0001" else "1000010" when DL="0010" else "0110001" when DL="0011" else "1100000" when DL="0100" else "0001000" when DL="0101" else 35 of 38

"0001100" when DL="0110" else "0000000" when DL="0111" else "0001111" when DL="1000" else "0100000" when DL="1001" else "0100100" when DL="1010" else "1001100" when DL="1011" else "0000110" when DL="1100" else "0010010" when DL="1101" else "1001111" when DL="1110" else "0000001" ;

SH <="1001000" when PB1='0' else "0111000" when DH="0000" else "0110000" when DH="0001" else "1000010" when DH="0010" else "0110001" when DH="0011" else "1100000" when DH="0100" else "0001000" when DH="0101" else "0001100" when DH="0110" else "0000000" when DH="0111" else "0001111" when DH="1000" else "0100000" when DH="1001" else "0100100" when DH="1010" else "1001100" when DH="1011" else "0000110" when DH="1100" else "0010010" when DH="1101" else "1001111" when DH="1110" else "0000001" ;

END seg;

In Order for this VHDL to run, the pin assignments must be made under the Assign/Pin/Location/Chip menu.

Name Type Pin # DH0 Input 36 DH1 Input 35 DH2 Input 34 DH3 Input 33 DL0 Input 41 DL1 Input 40 DL2 Input 39 DL3 Input 38 PB1 Input 28 PB2 Input 29 SH0 Output 13 SH1 Output 12 SH2 Output 11 SH3 Output 9 SH4 Output 8 SH5 Output 7 SH6 Output 6 SL0 Output 24 SL1 Output 23 SL2 Output 21 SL3 Output 20 36 of 38

SL4 Output 19 SL5 Output 18 SL6 Output 17

Downloading Program into board 13) Run the MAX+PLUS II software 14) Select MAX+PLUS II => Programmer 15) From Options =>Hardware => Setup selected LPT1. If a window comes up that displays “No Hardware” use the pull-down to change to “Byteblaster II” 16) Select JTAG =>Multi- Device JTAG chain so the checkmark appears 17) Select JTAG=> Multi-Device JTAG Setup. Select the Device name to be EPF10K70. Hit Select Programming File and Select c: \max2work\vhd1\orgate.sof (previously created small program). Click OK. Click the ADD button. The new filename should move in to the list in the inner window. 18) Select Detect JTAG Chain info button. System should respond “JTAG chain information confirmed by hardware check”. If not double check the hardware connections. 19) The Configure button in the programming window should be highlighted try Options => Hardware Setup and Confirm the port setting. If you still have problems confirm that the printer port BIOS setting uses ECP or EPP mode.

Test the Design 1) Using the switches at the bottom of the board, a binary input will display a hexadecimal value on the LED’s. 2) Any true signal to the FPLD on the push-buttons will override the hexadecimal output and “Hi” will instead be displayed on the LED’s.

Graphic Program Note: Ignore errors that may apper due to file location!

1) Select File => Open => C:/ => EET => CSE 275 => VHDL 2) Select graphic editor files and open the file counter_display.gdf 3) Select File=>Project=> Set Project to current file 4) Select MAX+PLUS II => Programmer 5) Select JTAG =>Multi-Device JTAG chain setup 6) Select the current device name listed and hit delete 7) Hit Select Programming File and select counter_display.sof 8) Select Add => Detect Jtag Chain Info 9) Hit ok and exit menu 10) Select Configure on programmer 11) The board should begin counting from 0-99 and reset when the left toggle is held and hold the present number when the right toggle is held

Supplement

The Altera FPLD is programmed via Altera MAX +PLUS II 10.2 Student Edition software. In order to use this program it is necessary to acquire a student license for use, update the software and install drivers. Then we must ensure the board is correctly configured by checking the jumper positions. Lastly we must use the software acquired earlier to make a program, compile and download it onto the FPLD. Software Installation 1) Obtain Altera Max FPLD, software cd “Altera MAX +PLUS II 10.2 Student Edition” and insert cd in computer. 2) Obtain a free “ student” license through the ALTERA website (http://www.altera.com/support/licensing/lic- university.html) 3) On the website choose the option “MAX+PLUS II Student edition software Version 10.2, 10.1,or 9.23” 4) Fill out fields as follows: E-mail address: (Any you have ready access to) 37 of 38

First Name: Kenneth Last name: Dudeck Address: City: State: Zip: Country: USA Telephone: School: Penn State University Hazleton Course Title: CSE 275 Course instructor: Kenneth Dudeck Current education level: Source of Software: Design laboratory package 5) An email has been sent to the address you provided. 6) Access the email and save the file license.dat to c:\maxplus2 7) Run MAX +PLUS 10.2 II Baseline from the Start menu 8) Answer “NO” to the prompt “Would You like information on how to obtain a free MAX+PLUS II Baseline license?” 9) Go to Options ->License Setup 10) Under “License File or Sever Name” enter: c:\maxplus2\license.dat 11) Click “OK”, “The license was installed successfully” should be displayed. To upgrade from MAX+PLUS II 10.2 to 10.22, Run the program; cdrom:\maxplusii_1022_pc.exe and install under install under c: \maxplus2.To install the new Byteblaster Driver; Open the DOS or command prompt and go c: \maxplus2\drivers\i386. Type bblpt /I and hit Enter. Hardware Installation 1) Hook the board up to the computer by connecting the board to the computer’s parallel port using the ByteBlaster II cable. 2) Supply power using the adapter supplied. Connect it to the board at the upper left-hand corner. 3) Verify that the device jumpers (located right below where the ByteBlaster II cable was connected to the board) are set to the following positions.

DIGITAL LAB - Project K. Dudeck

You can select one the projects listed below, or propose your own idea. These projects will be demonstrated in Logic Works and presented in Logic Works.

Project #1 In this project you will design another heater control circuit. 38 of 38

The circuit will control an Electrical Heater. The heater has a heater element, H, and a fan, F. Unlike the last heater which used two thermocouple inputs, TH and TL, this unit uses a two four bit binary numbers as inputs. The first four bit binary number corresponds to the desired room temperature set point, and second four-bit binary corresponds to the actual room temperature. The control should be as follows:

When the room temperature is more than two degrees cooler than the set point, the heater should come on and the fan should come on four clock pulses later.

When the room temperature is more than two degrees warmer than the set point, the heater should go off and the fan should stay on for two additional clock pulses then go off.

Use Logic Works to simulate your design.

Project #2 Design a bowling alley display that shows how many pins have been knocked down. The circuit has 10 inputs that come from the limit switches from each of the ten pins. If a pin is present, it sends a one to your circuit.

Project #3 Design a BCD display that will display a number BBBBBBBB.BBB as a decimal number DD.DDD

For example if the BCD number is 10010101.101 the display would show 95.625