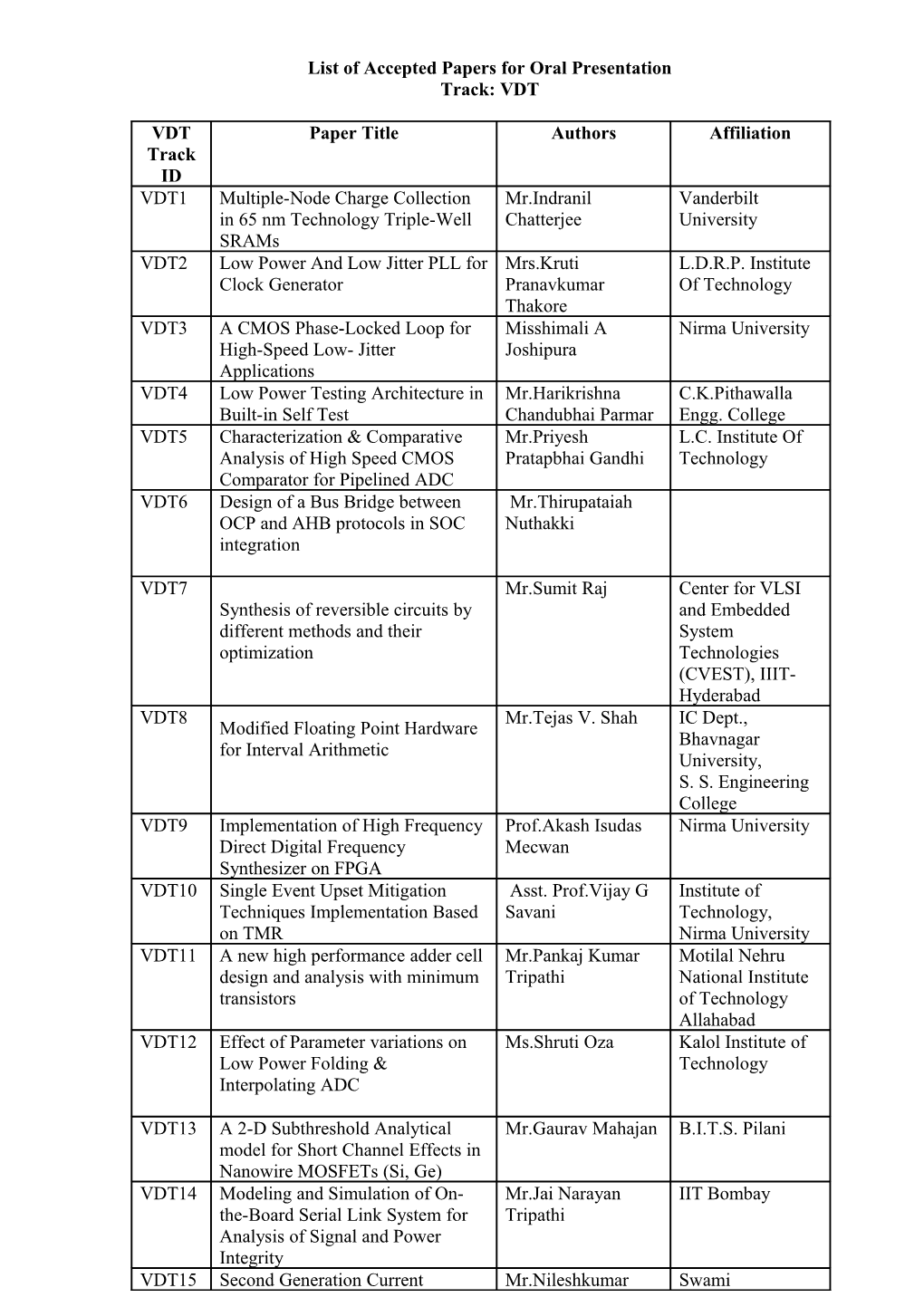

List of Accepted Papers for Oral Presentation Track: VDT

VDT Paper Title Authors Affiliation Track ID VDT1 Multiple-Node Charge Collection Mr.Indranil Vanderbilt in 65 nm Technology Triple-Well Chatterjee University SRAMs VDT2 Low Power And Low Jitter PLL for Mrs.Kruti L.D.R.P. Institute Clock Generator Pranavkumar Of Technology Thakore VDT3 A CMOS Phase-Locked Loop for Misshimali A Nirma University High-Speed Low- Jitter Joshipura Applications VDT4 Low Power Testing Architecture in Mr.Harikrishna C.K.Pithawalla Built-in Self Test Chandubhai Parmar Engg. College VDT5 Characterization & Comparative Mr.Priyesh L.C. Institute Of Analysis of High Speed CMOS Pratapbhai Gandhi Technology Comparator for Pipelined ADC VDT6 Design of a Bus Bridge between Mr.Thirupataiah OCP and AHB protocols in SOC Nuthakki integration

VDT7 Mr.Sumit Raj Center for VLSI Synthesis of reversible circuits by and Embedded different methods and their System optimization Technologies (CVEST), IIIT- Hyderabad VDT8 Mr.Tejas V. Shah IC Dept., Modified Floating Point Hardware Bhavnagar for Interval Arithmetic University, S. S. Engineering College VDT9 Implementation of High Frequency Prof.Akash Isudas Nirma University Direct Digital Frequency Mecwan Synthesizer on FPGA VDT10 Single Event Upset Mitigation Asst. Prof.Vijay G Institute of Techniques Implementation Based Savani Technology, on TMR Nirma University VDT11 A new high performance adder cell Mr.Pankaj Kumar Motilal Nehru design and analysis with minimum Tripathi National Institute transistors of Technology Allahabad VDT12 Effect of Parameter variations on Ms.Shruti Oza Kalol Institute of Low Power Folding & Technology Interpolating ADC

VDT13 A 2-D Subthreshold Analytical Mr.Gaurav Mahajan B.I.T.S. Pilani model for Short Channel Effects in Nanowire MOSFETs (Si, Ge) VDT14 Modeling and Simulation of On- Mr.Jai Narayan IIT Bombay the-Board Serial Link System for Tripathi Analysis of Signal and Power Integrity VDT15 Second Generation Current Mr.Nileshkumar Swami Conveyors Using Current Mirrors Kantilal Patel Sachchidanand Polytechnic College Visnagar VDT16 Effect of Parameter variation on Mrs.Amisha Naik Nirma University Second generation Current Conveyor VDT17 Analysis of Test Data Compression Mrs.Kinjal VPMP Methods Using Huffman Codes Ashokkumar Polytechnic Bhavsar VDT18 A Proposed Low Power 8-T SRAM Mr.Prashant NITTR, Cell for Programmable Devices Upadhyay Chandigarh VDT19 Sense Amplifier Based D Flip Flop Prof. Piyush Nirma University Implementation in 0.18µm Bhatasana Technology VDT20 Scaling Effect over Proposed Mr.Vaibhav Neema Devi Ahilya Technique “VSECURE” for Static University, Indore Power Reduction in Digital CMOS VLSI cir List of Accepted Papers for Poster Presentation

Track: VDT

VDT Paper Title Authors Affiliation Paper ID VDT21 Expidite the verification of DSP Mr.Bhargavraj E-Infochips, ASIC design using System Vijaykumar Patel Ahmedabad Verilog and MATLAB VDT22 Fault Detection And Mr.Bhargavraj E-Infochips, Localization On Symmetrically Vijaykumar Patel Ahmedabad Distributed FPGA’s VDT23 Novel nano scaled Mr.Bhavin D Gajjar L.D.Collge of MOSFET(Tunnel FET) Engineering, Ahmedabad VDT24 Performance Evaluation of Mr.Yashwant Singh L.D.Collge of Leakage Reduction Technique Engineering, for a Single SRAM Cell at 45nm Ahmedabad Technology VDT25 A Comparative Analysis of Misshimadri Singh Mits Power & Delay Optimize Raghav Lakshmangarh Digital Logic Families for High Performance System VDT26 Survey on Current Verification Mr.Dhaval L.D.Collge of Techniques for System on Chip Maheshkumar Modi Engineering, (SoC) Ahmedabad VDT27 An FPGA Implementation Misschanpreet Kaur Nitttr Sec 26 Efficient Equalizer for ISI Toor Chandigarh Removal in Wireless Applications VDT28 Analog VLSI Implementation Mr.Amit Joshi Student and Simulation of Neural Network Architecture for Signal Processing VDT29 Multiple Input Single Output Prof.Vaishali Hitesh NU- Filters Using CMOS DVCC in Dhare IT,Ahmedabad 0.25µm Technology VDT30 Implementation Of Lowpower Missswathi JNTU,Anantap Audio Subword Sorter Unit For Boinapally ur Audio Streaming Applications VDT31 Missarchana Shri. Rameshkumar Tiwari Ramdeobaba Amba Dedicated Dma Kamla Nehru Controller With Multiple Engineering Masters Using Vhdl College, Nagpur, RTM Nagpur University VDT32 Mr.Prashant R Rothe Priyadarshini Implementation Of Single College of Precision Floating Point Engineering, Processor Using FPGA Nagpur, India VDT33 High Speed Pattern Matching Mr.Goreddy JNTU For Intrusion Detection in Govardhana Reddy Network Security VDT34 Implementation of low power Missboinapally JNTU College audio subword sorter unit for Swathi Of Engineering audio streaming applications Anantapur VDT35 Accurate Evaluation Of Sensor Mr.Abhinay Bollam Jawaharlal Networks Using Economical Technical Pipelined Mips University VDT36 Organic semiconductors as Ms.Sarita Kumari IIT Delhi / Organic Field Effect Gjust Hisar Transistors: A mini review & Simulation studies VDT37 High Speed Encryption And Missshruthi JNTU Decryption Of Blowfish Mallepula VDT38 Ms.Payal Jain Education and Vhdl Implementation Of Research Network Repeater Infosys Technologies Chandigarh VDT39 Implementation Of High Speed Mr.Valluru Satish Sri Indu Huffman Decoder Kumar College of Engineering & Technology, JNTU Hyderabad affiliation VDT40 Low Power Sram Cell Using Mr.Pankaj SSPC,Visnagar 0.18µM Technology Punamchand Prajapati